SCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - Check

Diunggah oleh

Jayesh PopatJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

SCAN DRC Violation Solutions: Add - Cell - Models Report - DFT - Check

Diunggah oleh

Jayesh PopatHak Cipta:

Format Tersedia

SCAN DRC Violation Solutions

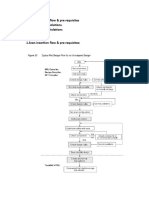

S1 Violation: all the clock inputs (including sets and resets) of In dofile, before inserting

each non-scan scan chains, you must

memory element to ensure that these inputs can be turned off. specify the cell models

with the

Unstable non-scan cells when clock is off add_cell_models

command. You can use

/StartSyncWr_reg clock the report_dft_check

/PMWr_r_reg set command to display the

/DMWr_r_reg set signals where test logic

/MemWrSync1_reg Reset & Clock can be inserted to make

the signals controllable.

set test logic -set on -

reset on -clock on :

Inserts test logic to

control the set, reset,

clock, enable, or write

control signals to make

them

scannable when scan

chains are inserted

Or by manually hacking

the netlist i.e. by manually

adding required library

cells(in our case mux)

make the clock, set, and

reset controllable

S2 Violations: checks all clock inputs (not including sets and In dofile, before inserting

resets) of each non-scan scan chains, you must

memory element to see whether they can capture data. specify

The report_dft_check command set test logic -clock on:

provides information for troubleshooting these failures, by Inserts test logic to

listing the cells that fail this check control clock, to make it

along with their associated gate identification numbers. scannable when scan

chains are inserted

There were 3 clock rule C7 fails (nonscan cell capture ability check).

Or by manually hacking

Note: There were 3 S2 violations that will be fixed by adding test logic the netlist i.e. by manually

adding required clk to the

C7: #fails=3 handling=warning (scan cell capture ability check) failing cells.

D5: #fails=3 handling=warning (non-scan memory element)

S2: #fails=3 handling=warning (clock capture ability check)

/IncCr_reg clock grounded

/StartSyncWr_reg clock grounded

/MemWrSync1_reg clock grounded

E4 violation: bus contention: Solution: Manual hack the

Warning: There were 1 BUS gates which may have possible contention. netlist.

(E10)

E4: #fails=4 handling=warning (bus contention during test procedures) Make scan_en as input

E10: #fails=1 handling=warning/atpg (possible BUS contention) port and add two and

ATPG bus checking performed on '/c3' (116) for 3 bussed TSDs. gates and one OR gate to

Where /c3 is bus having multiple input and one output. possible pass one of the

bus input to output by

Bus input enabling corresponding

i0, i1, i2 all three are driven by tristate buffer enable by

OR gate

Bus is having two drivers ‘72’ tristate buffer is enabled and ‘70’ tristate

buffer is also enabled

Solution: command edit:

Not knowing. Please

suggest the same.

Case 5: No violations Two latches are skipped

from the scan-insertion

"Design has 1 clock domain with DFFs and latches and insert 2 scan process. This is expected.

chains"

Latches in the original net-list(pre-scan).

1.) TLATX1 StartSyncRd_reg ( .G(n425), .D(MemReadSync1), .QN(n74)

);

2.) TLATX1 StartSyncRd_reg (.Q () , .QN ( n74 ) , .D ( MemReadSync1 )

, .G ( n425 ));

***********************************************************

***************************************************

***********************************************************

***************************************************

Latches in the scan inserted netlist

1.) TLATX1 StartRd_reg (.Q ( StartRd ) , .QN ( net232898 ) , .D ( N53 ) ,

.G ( N52 ));

2.) TLATX1 StartSyncRd_reg (.Q () , .QN ( n74 ) , .D ( MemReadSync1 )

, .G ( n425 ));

Two non-scan elements in the design net-list. Two scan-chains were

created. There were 56 sequential elements found and 54 are

converted into scan-cells and stitched properly.

Case 6: Design has 1 clock domain with only Scan FFs and insert 3 scan

chains.

Case 7: Design has no ATPG model for a Flip flop used in the netlist,

later create the model and insert scan with 2 scan chains.

Case 8: Design has 1 clock domain and a 10bit shift register. Insert scan

for the design and make the 10bit shift register has part of the scan

chain without converting it to Scan FFs. Use 2 scan chains with new

ports for scan in and scan out

Case 9: Design has 1 clock domain, insert 2 scan chains for design

containing 2 memories but no memory Bist or collar around the

memory

10) Design has modules where in block1 is already scan inserted with 4

scan chains. Insert scan for other blocks with 4 chains. Balance the scan

chains for the entire design from the top module using 4 chains.

Case 11: Design has 2 modules block1 and block2. Insert 4 scan chains

for the design by

ignoring block2 and insert lockup latches at end of chains

Top

|___block1

|___block2

Case 12: Design has 3 clocks(one +ve, one -ve, one using both edges)

a) use default scan insertion

b) mix clock domains and insert scan

c) mix edges and clock domains and insert scan

d) use a single test clock and insert 4 scan chains

Anda mungkin juga menyukai

- Atpg Answer Name: Meet ZankatDokumen5 halamanAtpg Answer Name: Meet ZankatMeet ZankatBelum ada peringkat

- DFT QuestionsDokumen8 halamanDFT QuestionsNaga NitheshBelum ada peringkat

- Scan Insertion Lab ObservationsDokumen2 halamanScan Insertion Lab ObservationssenthilkumarBelum ada peringkat

- Simulation Mismatches Can Foul Up Test-Pattern VerificationDokumen6 halamanSimulation Mismatches Can Foul Up Test-Pattern VerificationAdhi SuruliBelum ada peringkat

- What Is DFT in VLSIDokumen22 halamanWhat Is DFT in VLSINaga Nithesh100% (4)

- Scan Insertion FlowDokumen9 halamanScan Insertion Flowsharath ABelum ada peringkat

- Post-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Dokumen10 halamanPost-Silicon SOC: Keywords: DFT (Design For Testability), ATPG (Automatic Test Pattern Generation)Amena FarhatBelum ada peringkat

- Debugging Simulation Mismatches in Fastscan: by Geir Eide Last Modified: July 03, 2001Dokumen21 halamanDebugging Simulation Mismatches in Fastscan: by Geir Eide Last Modified: July 03, 2001prakashthamankar100% (3)

- Few Important QuestionsDokumen7 halamanFew Important QuestionsShankhadeep DasBelum ada peringkat

- Scan Insertion Lab Observations: Vlsiguru DFT TrainingDokumen2 halamanScan Insertion Lab Observations: Vlsiguru DFT Trainingsenthilkumar100% (1)

- Scan Insertion - Week2&3Dokumen48 halamanScan Insertion - Week2&3VENKATRAMAN100% (1)

- COMPRESSION PPT by HK - OdpDokumen23 halamanCOMPRESSION PPT by HK - Odpsuneetha100% (5)

- Scan PDFDokumen49 halamanScan PDFferoz100% (1)

- Timing SimulationDokumen3 halamanTiming SimulationKarthik Sharma100% (1)

- Scan Insertion Lab Observation (K.S.K.S.sarma)Dokumen33 halamanScan Insertion Lab Observation (K.S.K.S.sarma)Kittu Krishna100% (2)

- Mahitha Scan Insertion Observation PDFDokumen30 halamanMahitha Scan Insertion Observation PDFPrafulani Gajbhiye100% (1)

- Compression AssignmentDokumen7 halamanCompression Assignmentpoojithas acharya100% (1)

- Atpg Coverage LossDokumen4 halamanAtpg Coverage LossUmesh ParasharBelum ada peringkat

- DFT VisionDokumen18 halamanDFT VisionNaganithesh Ghattamaneni0% (1)

- Compression NotesDokumen10 halamanCompression NotesSurendra Lovely Surendra50% (2)

- ATPGDokumen54 halamanATPGsrikanth100% (1)

- DFT QnsDokumen6 halamanDFT QnsRajishaBelum ada peringkat

- Test Point Insertion For Test Coverage Improvement in DFT - Design For Testability (DFT) .HTMLDokumen75 halamanTest Point Insertion For Test Coverage Improvement in DFT - Design For Testability (DFT) .HTMLIlaiyaveni IyanduraiBelum ada peringkat

- Synthesis Netlist - Library Model - Dofile CommandsDokumen30 halamanSynthesis Netlist - Library Model - Dofile CommandsPrafulani GajbhiyeBelum ada peringkat

- Wrapper p1500Dokumen8 halamanWrapper p1500srikanth100% (1)

- Frequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimeDokumen15 halamanFrequencies.: Transition Fault Model: This Is Considered To Stuck at Fault Model Within A TimedeepaBelum ada peringkat

- Assignment Section-1 1. What Is DFT?Dokumen18 halamanAssignment Section-1 1. What Is DFT?PAVAN KUMAR TAVADABOINA100% (1)

- Assignment CompressionDokumen8 halamanAssignment CompressionPrafulani Gajbhiye100% (2)

- Name DFT Trainee Atpg Insertion Cases ObservationsDokumen17 halamanName DFT Trainee Atpg Insertion Cases ObservationssenthilkumarBelum ada peringkat

- Assignment 1 Poovika.tDokumen12 halamanAssignment 1 Poovika.tsenthilkumarBelum ada peringkat

- Tips For Simulation Debug PDFDokumen21 halamanTips For Simulation Debug PDFSaurin Shah100% (1)

- DFT Interview QsDokumen4 halamanDFT Interview QsHARISH DAMARLABelum ada peringkat

- DFT Interview QuestionsDokumen3 halamanDFT Interview QuestionsJayesh PopatBelum ada peringkat

- Interview Questions Related To Scan, ATPG, EDT and SimulationDokumen1 halamanInterview Questions Related To Scan, ATPG, EDT and SimulationSiva SreeramdasBelum ada peringkat

- DFTDokumen21 halamanDFTMuhsin Nk100% (1)

- Streaming Scan NetworkDokumen51 halamanStreaming Scan NetworkVENKATRAMAN100% (1)

- Named Capture ProcedureDokumen2 halamanNamed Capture Proceduresenthilkumar67% (3)

- Edt Insertion Lab Observations Test Case 1: - Problem Definition: - InputsDokumen42 halamanEdt Insertion Lab Observations Test Case 1: - Problem Definition: - Inputspoojithas acharyaBelum ada peringkat

- Debugging Simulation MismatchesDokumen4 halamanDebugging Simulation Mismatcheselectro123eBelum ada peringkat

- Scan Insertion Labs GuidelinesDokumen12 halamanScan Insertion Labs GuidelinessenthilkumarBelum ada peringkat

- ATPG Tool FlowDokumen12 halamanATPG Tool FlowAdhi SuruliBelum ada peringkat

- DFT Interview QuestionsDokumen9 halamanDFT Interview QuestionsNaga Nithesh100% (1)

- DFT Interview QuestionsDokumen2 halamanDFT Interview Questionsrupesh kumarBelum ada peringkat

- DFT Interview Questions - Welcome To World of VLSIDokumen5 halamanDFT Interview Questions - Welcome To World of VLSINaganithesh GhattamaneniBelum ada peringkat

- Embedded Deterministic Test: by M. BalakrishnaDokumen28 halamanEmbedded Deterministic Test: by M. Balakrishnasuryatejamula0% (1)

- Atpg Lab NotesDokumen11 halamanAtpg Lab Notesrajkumar gunjaBelum ada peringkat

- High Test CoverageDokumen58 halamanHigh Test CoverageAdhi SuruliBelum ada peringkat

- 1 LOS and LOC in Vlsi Conference-ProceedingDokumen9 halaman1 LOS and LOC in Vlsi Conference-Proceedingbharghav saiBelum ada peringkat

- Q-A's On ATPG & SCAN.Dokumen21 halamanQ-A's On ATPG & SCAN.Hitesh PradhanBelum ada peringkat

- ATPG Methodology FlowDokumen37 halamanATPG Methodology FlowaanbalanBelum ada peringkat

- Compression NotesDokumen12 halamanCompression Notessenthilkumar100% (2)

- Training On EDT (1) - Copy (1) (3) 1Dokumen52 halamanTraining On EDT (1) - Copy (1) (3) 1veena100% (1)

- Lab2 Block Level SSN Insertion On Processor CoreDokumen33 halamanLab2 Block Level SSN Insertion On Processor Corezys WdBelum ada peringkat

- DFT Interview Questions1Dokumen34 halamanDFT Interview Questions1rajkumar gunjaBelum ada peringkat

- DFT FaqDokumen15 halamanDFT FaqBrijesh S D100% (1)

- DFT Interview Questions & AnswersDokumen22 halamanDFT Interview Questions & Answersdeepa100% (4)

- Loc Vs LosDokumen22 halamanLoc Vs LoseashwarBelum ada peringkat

- EDTDokumen47 halamanEDTRaghavendra MatturBelum ada peringkat

- VLSI Test Principles and Architectures: Design for TestabilityDari EverandVLSI Test Principles and Architectures: Design for TestabilityPenilaian: 4.5 dari 5 bintang4.5/5 (4)

- Lab ReportDokumen17 halamanLab ReportYashwanthKumarBelum ada peringkat

- CosmoNote RequirementsDokumen6 halamanCosmoNote RequirementsJayesh PopatBelum ada peringkat

- DFT Interview QuestionsDokumen5 halamanDFT Interview QuestionsJayesh PopatBelum ada peringkat

- CosmoNote RequirementsDokumen6 halamanCosmoNote RequirementsJayesh PopatBelum ada peringkat

- 32 DFT Inc. Interview Questions (With Answers)Dokumen6 halaman32 DFT Inc. Interview Questions (With Answers)Jayesh PopatBelum ada peringkat

- Laravel TaskDokumen2 halamanLaravel TaskJayesh PopatBelum ada peringkat

- Practical - Develop in LaravelDokumen3 halamanPractical - Develop in LaravelJayesh PopatBelum ada peringkat

- B8B10 EncodeDokumen13 halamanB8B10 EncodeJayesh PopatBelum ada peringkat

- DFT Interview QuestionsDokumen3 halamanDFT Interview QuestionsJayesh PopatBelum ada peringkat

- Chain Blockage IssueDokumen1 halamanChain Blockage IssueJayesh PopatBelum ada peringkat

- DFT Interview QuestionsDokumen3 halamanDFT Interview QuestionsJayesh PopatBelum ada peringkat

- DFT Interview QuestionsDokumen3 halamanDFT Interview QuestionsJayesh PopatBelum ada peringkat

- Kmap Teknik DigitalDokumen27 halamanKmap Teknik DigitalmutaharrikBelum ada peringkat

- Verilog Scheduling SemanticsDokumen14 halamanVerilog Scheduling SemanticsJayesh PopatBelum ada peringkat

- Edited - 7 On Chip Clock ControllerDokumen8 halamanEdited - 7 On Chip Clock ControllerJayesh Popat0% (1)

- Chapter 1: Software Development ProcessDokumen21 halamanChapter 1: Software Development ProcessJayesh PopatBelum ada peringkat

- SV Scheduling SemanticsDokumen13 halamanSV Scheduling SemanticsJayesh PopatBelum ada peringkat

- SV Scheduling SemanticsDokumen13 halamanSV Scheduling SemanticsJayesh PopatBelum ada peringkat

- 2110016Dokumen25 halaman2110016Jayesh PopatBelum ada peringkat

- Arunima SinhaDokumen5 halamanArunima SinhaJayesh PopatBelum ada peringkat

- SV Scheduling SemanticsDokumen13 halamanSV Scheduling SemanticsJayesh PopatBelum ada peringkat

- Kmap Teknik DigitalDokumen27 halamanKmap Teknik DigitalmutaharrikBelum ada peringkat

- Chapter 1: Software Development ProcessDokumen21 halamanChapter 1: Software Development ProcessJayesh PopatBelum ada peringkat

- 1 Class IntroDokumen16 halaman1 Class IntroJayesh PopatBelum ada peringkat

- Plain TextDokumen1 halamanPlain TextJayesh PopatBelum ada peringkat

- Manual User EcgDokumen40 halamanManual User EcgJoy MarvelBelum ada peringkat

- IFE Training ManualDokumen184 halamanIFE Training ManualJAYACHANDRANBelum ada peringkat

- Operation and Maintenance Instructions: Medipoint 26 Alarm System Local AlarmDokumen22 halamanOperation and Maintenance Instructions: Medipoint 26 Alarm System Local AlarmShoaib KhanBelum ada peringkat

- Lightsmart - Pe150E User'S Manual: Multi-Service Fiber Optical MultiplexerDokumen119 halamanLightsmart - Pe150E User'S Manual: Multi-Service Fiber Optical MultiplexerHanh LeBelum ada peringkat

- Semiconductor QBDokumen9 halamanSemiconductor QBdheeraj rajBelum ada peringkat

- Service ManUal - Error CodesDokumen13 halamanService ManUal - Error CodesStefanoViganóBelum ada peringkat

- Dse850 Data SheetDokumen2 halamanDse850 Data SheetGeorge AniborBelum ada peringkat

- HikVision DS-D5019QE-B 18.5" MonitorDokumen3 halamanHikVision DS-D5019QE-B 18.5" Monitorchandak ghatakBelum ada peringkat

- AE340 - Architectural Illumination and Electrical System NotesDokumen11 halamanAE340 - Architectural Illumination and Electrical System Noteschloe2197Belum ada peringkat

- Kamranmahar O3O4 1797633: 15. Which Type of Computers Uses The 8-Bit Code Called Ebcdic?Dokumen26 halamanKamranmahar O3O4 1797633: 15. Which Type of Computers Uses The 8-Bit Code Called Ebcdic?AmirSaeedBelum ada peringkat

- BigJoe S22Dokumen162 halamanBigJoe S22martinBelum ada peringkat

- Multilin EPM 7000P: Grid SolutionsDokumen14 halamanMultilin EPM 7000P: Grid SolutionsMohammad ShreatehBelum ada peringkat

- COM600S - Substation Automation, Analysis and Data ManagementDokumen52 halamanCOM600S - Substation Automation, Analysis and Data ManagementVamanBelum ada peringkat

- A Bridgeless Single-Stage Half-Bridge AC DC ConverterDokumen12 halamanA Bridgeless Single-Stage Half-Bridge AC DC ConverterSaravana Prakash PBelum ada peringkat

- Frontech User's Manual PDFDokumen9 halamanFrontech User's Manual PDF06l01a0224Belum ada peringkat

- Decca TreeDokumen4 halamanDecca Treeiuridicaprima4Belum ada peringkat

- CS6461 - Computer Architecture Fall 2016 Instructor Morris LancasterDokumen28 halamanCS6461 - Computer Architecture Fall 2016 Instructor Morris Lancaster闫麟阁Belum ada peringkat

- Measuring Planck's Constant Using The Photoelectric Effect Purpose: TheoryDokumen3 halamanMeasuring Planck's Constant Using The Photoelectric Effect Purpose: TheoryAmrit NumanBelum ada peringkat

- Assignment 10: Unit 13 - Week 10Dokumen4 halamanAssignment 10: Unit 13 - Week 10Anjali YadavBelum ada peringkat

- 31 SDMS 02rev01Dokumen15 halaman31 SDMS 02rev01sardarmkhanBelum ada peringkat

- Jndal Power ResumeDokumen2 halamanJndal Power ResumeRahul Kumar YadavBelum ada peringkat

- 78 - 1375264594 - 142606 - Lockout Relay CatalogueDokumen52 halaman78 - 1375264594 - 142606 - Lockout Relay CatalogueJarrett MathewsBelum ada peringkat

- Genius IO High Speed Counter User's Manual, GFK-0415EDokumen145 halamanGenius IO High Speed Counter User's Manual, GFK-0415EEduardo DiazBelum ada peringkat

- SRT 1F Equipment DetailsDokumen8 halamanSRT 1F Equipment Detailsjcardenas55Belum ada peringkat

- GB38031-2020EN Electric Vehiles Traction Battery Safety RequerimentsDokumen15 halamanGB38031-2020EN Electric Vehiles Traction Battery Safety RequerimentsMarianoBelum ada peringkat

- Agolar PCB Catalogue 2022-23Dokumen41 halamanAgolar PCB Catalogue 2022-23Karthikeyan .NBelum ada peringkat

- Groundfos - SP 9-48Dokumen10 halamanGroundfos - SP 9-48suwono radukBelum ada peringkat

- Abeba DebruDokumen90 halamanAbeba Debruabera alemayehuBelum ada peringkat

- ECII Fill in The BlanksDokumen5 halamanECII Fill in The BlanksprabraghuBelum ada peringkat

- 24.71.00007 ATU X CrossesDokumen14 halaman24.71.00007 ATU X CrossesTitoBelum ada peringkat