Sathyabama University: (Established Under Section 3 of UGC Act, 1956)

Diunggah oleh

johnarulrajJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Sathyabama University: (Established Under Section 3 of UGC Act, 1956)

Diunggah oleh

johnarulrajHak Cipta:

Format Tersedia

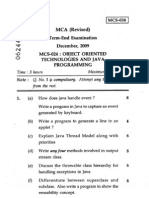

Register Number

SATHYABAMA UNIVERSITY

(Established under section 3 of UGC Act,1956)

Course & Branch : M.Tech - VLSI

Title of the Paper : VLSI Signal Processing Max. Marks:80

Sub. Code : SECX5024-782301 (2008-2010) Time : 3 Hours

Date : 05/03/2012 Session :FN

______________________________________________________________________________________________________________________

PART - A (6 x 5 = 30)

Answer ALL the Questions

1. Distinguish loop bound and iteration bound.

2. List the properties of Retiming techniques.

3. What is the need for systolic architecture design?

4. Explain redundant to non redundant converter.

5. What is wave pipelining?

6. Explain scaling versus power consumption.

PART – B (5 x 10 = 50)

Answer ALL the Questions

7. Explain algorithms for computing iteration bound.

(or)

8. Consider the recursive filter x(n)=ax(n-2)+u(n).Pipeline this

multiply-add operator by 2 stages, by first breaking up the

multiply add operation into 2 components and redistributing the

delay elements in the loop.

9. Prove that the critical path of a J –unfolded DFG is greater than

or equal to the critical path of the (J-1) unfolded DFG.

(or)

10. Unfolding preserves the number of delays in a DFG. Prove.

11. Draw the space time mapping of design R1.

(or)

12. Design a radix-4 minimally redundant to non redundant converter

operating in the lsd-first mode for word length of 8 digits.

13. Draw an H-tree distribution network for a 4-bit x 4-bit array of

regular cells with and without intermediate buffering.

(or)

14. Design a 9-transistor positive edge triggered true single phase

clocked flip-flop and explain its operation.

15. Discuss Speed –Area-Power tradeoff issues related to mixed

signal design and SOC.

(or)

16. Explain CORDIC algorithm with example.

Anda mungkin juga menyukai

- S3 Bca 2017 Reg - SupplyDokumen9 halamanS3 Bca 2017 Reg - SupplyLeslie QwerBelum ada peringkat

- A1127sample Paper 2014sdfsdfsdfsdfsdfsdfsdfsdfdfsdfsdfsdfsdfsdfsdfDokumen2 halamanA1127sample Paper 2014sdfsdfsdfsdfsdfsdfsdfsdfdfsdfsdfsdfsdfsdfsdfRajwinder Singh BansalBelum ada peringkat

- s4 Cse Ns May 2013Dokumen15 halamans4 Cse Ns May 2013rakhilpvBelum ada peringkat

- LIT Digital Logic Circuits Model ExamDokumen2 halamanLIT Digital Logic Circuits Model ExamSoorya Priya Gopala KrishnaBelum ada peringkat

- Cse Aids Dec 2021Dokumen14 halamanCse Aids Dec 2021RitikaBelum ada peringkat

- MCS 031Dokumen5 halamanMCS 031rajivkkBelum ada peringkat

- M.SC (Computer Science) 2008 PatternDokumen48 halamanM.SC (Computer Science) 2008 PatternTempBelum ada peringkat

- Signal & Systems: Roll No. Total No. of Pages: 02 Total No. of Questions: 09Dokumen2 halamanSignal & Systems: Roll No. Total No. of Pages: 02 Total No. of Questions: 09everythingperfect2003Belum ada peringkat

- Nanomap: An Integrated Design Optimization Flow For A Hybrid Nanotube/Cmos Dynamically Reconfigurable ArchitectureDokumen27 halamanNanomap: An Integrated Design Optimization Flow For A Hybrid Nanotube/Cmos Dynamically Reconfigurable Architectureசக்தி இலக்கியா சத்தீஸ்வரன்Belum ada peringkat

- SRI VELLAPPALLY NATESAN COLLEGE MICROWAVE DEVICE EXAMDokumen1 halamanSRI VELLAPPALLY NATESAN COLLEGE MICROWAVE DEVICE EXAManupvasuBelum ada peringkat

- R13 - December, 2014 - Regular ExaminationsDokumen3 halamanR13 - December, 2014 - Regular ExaminationsmushahedBelum ada peringkat

- CMP 776 Final 2020Dokumen2 halamanCMP 776 Final 2020Ounteni hyacinthe firmin OboulbigaBelum ada peringkat

- SET-1: Answer To The Interview QuestionsDokumen9 halamanSET-1: Answer To The Interview QuestionsÆshok IncreĐible KingBelum ada peringkat

- Power SystemDokumen17 halamanPower Systemprachi singhBelum ada peringkat

- WWW Manaresults Co inDokumen1 halamanWWW Manaresults Co inSudheer BabuBelum ada peringkat

- Printed Pages-4: Optical Fiber Basics & Holography PrinciplesDokumen4 halamanPrinted Pages-4: Optical Fiber Basics & Holography PrinciplesVinal KumarBelum ada peringkat

- CSIT211 Computer ArchitectureDokumen1 halamanCSIT211 Computer Architectureभुपेन्द्र बोहराBelum ada peringkat

- 2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Dokumen7 halaman2011 Advanced Computer Architecture: CS/B.TECH (CSE) /SEM-4/CS-403/2011Avik MitraBelum ada peringkat

- Model Exam DSPDokumen2 halamanModel Exam DSPChristoBelum ada peringkat

- Smart Materials, Sensors and ActuatorsDokumen2 halamanSmart Materials, Sensors and ActuatorsmanojBelum ada peringkat

- Mrcet R22 Ii - I QBDokumen38 halamanMrcet R22 Ii - I QBAyyan reddyBelum ada peringkat

- Modern Control Theory Exam Questions NR/R09Dokumen3 halamanModern Control Theory Exam Questions NR/R09IbmWasuserBelum ada peringkat

- Cse5 CN Dec09Dokumen2 halamanCse5 CN Dec09rahul_prabhakarBelum ada peringkat

- Tribhuvan University Exam Questions on Distributed SystemsDokumen10 halamanTribhuvan University Exam Questions on Distributed SystemsBirat KarkiBelum ada peringkat

- ECS088 - Soft ComputingDokumen3 halamanECS088 - Soft ComputingManjeet MishraBelum ada peringkat

- B.Tech. Theory Examination (Sem-Viii) 2016-17 Electronic SwitchingDokumen1 halamanB.Tech. Theory Examination (Sem-Viii) 2016-17 Electronic SwitchingDeepak Kumar100% (1)

- ES PaperDokumen22 halamanES PaperRaghu Nath SinghBelum ada peringkat

- Adaptive sequencing circuits and TSPC based D flip-flopDokumen94 halamanAdaptive sequencing circuits and TSPC based D flip-flopPranav DarganBelum ada peringkat

- C - Obstacle-Aware Symmetrical Clock Tree Construction - 2017Dokumen4 halamanC - Obstacle-Aware Symmetrical Clock Tree Construction - 2017JanviBelum ada peringkat

- Paper ID I IA0467l: QI) e o X 2 - 2 0)Dokumen2 halamanPaper ID I IA0467l: QI) e o X 2 - 2 0)amanvirbBelum ada peringkat

- Digital Nov 07Dokumen6 halamanDigital Nov 07skssushBelum ada peringkat

- DSP-Code No: 117CKDokumen2 halamanDSP-Code No: 117CKCH. Kranthi RekhaBelum ada peringkat

- Sem 5 Put 2022-23Dokumen8 halamanSem 5 Put 2022-23Jatin ChoudharyBelum ada peringkat

- Section A: Note-: Attempt All QuestionsDokumen17 halamanSection A: Note-: Attempt All QuestionsmbhagavanprasadBelum ada peringkat

- 133 BQ 122019Dokumen2 halaman133 BQ 122019vinod chittemBelum ada peringkat

- Cs 204 Operating SystemsDokumen3 halamanCs 204 Operating SystemsJoona JohnBelum ada peringkat

- HT TP: //qpa Pe R.W But .Ac .In: Pattern RecognitionDokumen4 halamanHT TP: //qpa Pe R.W But .Ac .In: Pattern RecognitionDuma DumaiBelum ada peringkat

- Mca 405 BDokumen2 halamanMca 405 Bkola0123Belum ada peringkat

- MCA 312 Design&Analysis of Algorithm QuestionBankDokumen7 halamanMCA 312 Design&Analysis of Algorithm QuestionBanknbprBelum ada peringkat

- Design and Analysis of Algorithms Laboratory (15Csl47)Dokumen12 halamanDesign and Analysis of Algorithms Laboratory (15Csl47)Raj vamsi Srigakulam100% (1)

- Question Papers of Two Year M. Tech I Semester Regular Examinations April - 2012Dokumen29 halamanQuestion Papers of Two Year M. Tech I Semester Regular Examinations April - 2012mdphilipBelum ada peringkat

- Gujarat Technological UniversityDokumen1 halamanGujarat Technological UniversityAlpesh DafdaBelum ada peringkat

- HW 4Dokumen2 halamanHW 4jameelahmadBelum ada peringkat

- Journal 11Dokumen6 halamanJournal 11Eccker RekcceBelum ada peringkat

- MODULE - Wise Question - 2022-ADE-CODokumen4 halamanMODULE - Wise Question - 2022-ADE-COvinayvinayakars313Belum ada peringkat

- WWW - Manaresults.Co - In: (Electronics and Communication Engineering)Dokumen2 halamanWWW - Manaresults.Co - In: (Electronics and Communication Engineering)vinod chittemBelum ada peringkat

- Cusat Ec 6th Sem Question PaperDokumen16 halamanCusat Ec 6th Sem Question PaperJinu Madhavan0% (1)

- Btech Cs 5 Sem Design and Analysis of Algorithm Rcs502 2022Dokumen1 halamanBtech Cs 5 Sem Design and Analysis of Algorithm Rcs502 2022YASH GARGBelum ada peringkat

- KL UNIVERSITY CSE M.Tech II SEM COMPUTER NETWORKS MODEL PAPERDokumen1 halamanKL UNIVERSITY CSE M.Tech II SEM COMPUTER NETWORKS MODEL PAPERPraneetha ReddyBelum ada peringkat

- ECS305 (OOS) 2nd SessionalDokumen3 halamanECS305 (OOS) 2nd SessionalAshutosh SinghBelum ada peringkat

- Q PaperDokumen1 halamanQ PaperniteshSFSBelum ada peringkat

- Question Bank - ADSD ET7101Dokumen7 halamanQuestion Bank - ADSD ET7101karthikamageshBelum ada peringkat

- BE 2008 Electronics&TelecommunicationDokumen71 halamanBE 2008 Electronics&TelecommunicationAdib ShaikhBelum ada peringkat

- 603 PaperDokumen6 halaman603 PaperMaarij RaheemBelum ada peringkat

- DSP Integrated Circuits 3Dokumen3 halamanDSP Integrated Circuits 3brindkowsiBelum ada peringkat

- (5037) - 11 M.Sc. Computer Science CS-101: Principles of Programming Languages (2011 Pattern) (Semester-I)Dokumen28 halaman(5037) - 11 M.Sc. Computer Science CS-101: Principles of Programming Languages (2011 Pattern) (Semester-I)XIAOBEL TradingsBelum ada peringkat

- DGD 8Dokumen2 halamanDGD 8Dolores MakaruinaBelum ada peringkat

- Mathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsDari EverandMathematical and Computational Modeling: With Applications in Natural and Social Sciences, Engineering, and the ArtsRoderick MelnikBelum ada peringkat

- Catholic Saints Calendar April-SeptemberDokumen3 halamanCatholic Saints Calendar April-SeptemberjohnarulrajBelum ada peringkat

- PLV Recruitment Notice and Application 2021 - 0Dokumen3 halamanPLV Recruitment Notice and Application 2021 - 0johnarulrajBelum ada peringkat

- Std11 TamilDokumen216 halamanStd11 TamilSiva NanbaendaBelum ada peringkat

- Image Transformations: A Concise Guide to 2D Unitary TransformsDokumen9 halamanImage Transformations: A Concise Guide to 2D Unitary Transformsvisalrajk4467Belum ada peringkat

- Notification Bank of India Officer PostsDokumen31 halamanNotification Bank of India Officer PostsKushagra ThakurBelum ada peringkat

- Image Transformations: A Concise Guide to 2D Unitary TransformsDokumen9 halamanImage Transformations: A Concise Guide to 2D Unitary Transformsvisalrajk4467Belum ada peringkat

- 606 FileM5152623523Dokumen203 halaman606 FileM5152623523johnarulrajBelum ada peringkat

- Electronics and Communication EngineeringDokumen131 halamanElectronics and Communication EngineeringjohnarulrajBelum ada peringkat

- Unit 2Dokumen131 halamanUnit 2ShanilDayalanBelum ada peringkat

- AddDokumen1 halamanAddjohnarulrajBelum ada peringkat

- Latches and Flip-Flops: Storage ElementsDokumen18 halamanLatches and Flip-Flops: Storage ElementsArnav GuptaBelum ada peringkat

- GATE 2018 ECE Morning Session Detailed Solutions by KREATRYXDokumen73 halamanGATE 2018 ECE Morning Session Detailed Solutions by KREATRYXjohnarulrajBelum ada peringkat

- Sihsd R-2017 It IiiDokumen1 halamanSihsd R-2017 It IiijohnarulrajBelum ada peringkat

- Acquaint Yourself Booklet EnglishDokumen7 halamanAcquaint Yourself Booklet EnglishSelva KumarBelum ada peringkat

- VL7301 Testing of Vlsi Circuits PDFDokumen2 halamanVL7301 Testing of Vlsi Circuits PDFjohnarulrajBelum ada peringkat

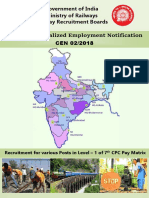

- Official Recruitemnt Notification For Sub Inspectors in Railway Protection Force and Railway Protection Special ForceDokumen27 halamanOfficial Recruitemnt Notification For Sub Inspectors in Railway Protection Force and Railway Protection Special ForceTopRankersBelum ada peringkat

- Ma6453 - PQTDokumen163 halamanMa6453 - PQTmayank321Belum ada peringkat

- Sihsd R-2017 It IiDokumen2 halamanSihsd R-2017 It IijohnarulrajBelum ada peringkat

- Digital Principles SwitchingDokumen545 halamanDigital Principles SwitchingHarshaBelum ada peringkat

- Suresh Academy Railway BIOLOGY MaterialDokumen10 halamanSuresh Academy Railway BIOLOGY MaterialjohnarulrajBelum ada peringkat

- CEN - 02 - 2018 - Group DDokumen36 halamanCEN - 02 - 2018 - Group DRrb Jobs Alert86% (49)

- My LifeDokumen6 halamanMy LifeAlicia TaylorBelum ada peringkat

- Obc CertificateDokumen1 halamanObc Certificateriteshh05Belum ada peringkat

- Notification IDBI Bank Executive Posts PDFDokumen17 halamanNotification IDBI Bank Executive Posts PDFTamilBelum ada peringkat

- Ec2013 A1 PDFDokumen24 halamanEc2013 A1 PDFBiswajit BeheraBelum ada peringkat

- ME Degree Exam Paper on Applied Mathematics for Electronics EngineersDokumen4 halamanME Degree Exam Paper on Applied Mathematics for Electronics EngineersLogesh WaranBelum ada peringkat

- SSC CPO Final PaperDokumen13 halamanSSC CPO Final PaperjohnarulrajBelum ada peringkat

- Aptitude Math Shortcuts Part1Dokumen11 halamanAptitude Math Shortcuts Part1kingraaja100% (1)

- Digital Principles SwitchingDokumen545 halamanDigital Principles SwitchingHarshaBelum ada peringkat