BLG222E Project3

Diunggah oleh

adJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

BLG222E Project3

Diunggah oleh

adHak Cipta:

Format Tersedia

BLG222E Computer Organization

Project 3

Due Date: 16.05.2017, 15:00

Design a hardwire-control unit for the following architecture. Use the structure that you

have designed in project #2.

Instruction format

There are two types of instructions as described below.

(1) Instructions with address reference has the format shown in Figure 1:

The OPCODE is a 5-bit field (See Table 1 for the definition).

The REGSEL is a 2-bit field (See left side of Table 2 for the definition).

The ADDRESSING MODE is a 1-bit field (See Table 3 for the definition).

The ADDRESS is 8 bits

OPCODE REGSEL ADDRESSING MODE ADDRESS

Figure 1: Instructions with an address reference

(2) Instructions without address reference has the format shown in Figure 2:

The OPCODE is a 5-bit field (See Table 1 for the definition).

DESTREG is a 3-bit field which specifies the destination register (See right side of

Table 2 for the definition).

SRCREG1 is a 3-bit field which specifies the first source register (See right side of

Table 2 for the definition).

SRCREG2 is a 3-bit field which specifies the second source register (See right side of

Table 2 for the definition).

OPCODE DESTREG SRCREG1 SRCREG2

Figure 2: Instructions without an address reference

Table 1: OPCODE field and SYMBols for opertions and their descriptions

OPCODE (HEX) SYMB ADDRESSING MODE DESCRIPTION

Ri (Selected according to REGSEL) Value (Value is

0x00 LD IM, D

described in Table 3)

0x01 ST D Value Ri (Selected according to REGSEL)

0x02 MOV N/A DESTREG SRCREG1

0x03 PSH N/A M[SP] SRCREG1, SP SP - 1

0x04 PUL N/A SP SP + 1, DESTREG M[SP]

0x05 ADD N/A DESTREG SRCREG1 + SRCREG2

0x06 SUB N/A DESTREG SRCREG2 - SRCREG1

0x07 DEC N/A DESTREG DESTREG - 1

0x08 INC N/A DESTREG DESTREG + 1

0x09 AND N/A DESTREG SRCREG1 AND SRCREG2

0x0A OR N/A DESTREG SRCREG1 OR SRCREG2

0x0B NOT N/A DESTREG NOT SRCREG1

0x0C LSL N/A DESTREG LSL SRCREG1

0xOD LSR N/A DESTREG LSR SRCREG1

0x0E BRA IM PC Value

0x0F BEQ IM IF Z=1 THEN PC Value

0x10 BNE IM IF Z=0 THEN PC Value

0x11 CALL IM M[SP] PC, SP SP – 1, PC Value

0x12 RET N/A SP SP + 1, PC M[SP]

Table 2:REGSEL (Left) and DESTREG/SRCREG1/SRCREG2 (Right) select the register of

interest for a particular instruction

REGSEL REGISTER DESTREG/SRCREG1/SRCREG2 REGISTER

00 R0 000 R0

01 R1 001 R1

10 R2 010 R2

11 R3 011 R3

100 PC

101 PC

110 AR

111 SP

Table 3: Addressing modes

ADDRESSING MODE MODE SYMB Value

0 Immediate IM ADDRESS Field

1 Direct D M[AR]

Example Code:

The code given below adds data that are stored at M[A0]+M[A1]+M[A2]+M[A3]+M[A4]

and stores the total at M[A5]. It is written as a loop that iterates 5 times.

ORG 0x20 # Write the program starting from the address 0x20

LD R0 IM 0x05 # R0 is used for iteration number

LD R1 IM 0x00 # R1 is used to store total

LD R2 IM 0xA0

MOV AR R2 # AR is used to track data adrress: starts from 0xA0

LABEL: LD R2 D # R2 <- M[AR] (AR = 0xA0 to 0xA4)

INC AR AR # AR <- AR + 1 (Next Data)

ADD R1 R1 R2 # R1 <- R1 + R2 (Total = Total + M[AR])

DEC R0 R0 # R0 <- R0 – 1 (Decrement Iteration Counter)

BNE IM LABEL # Go back to LABEL if Z=0 (Itertaion Counter > 0)

INC AR AR # AR <- AR + 1 (Total will be written to 0xA5)

ST R1 D # M[AR] <- R1 (Store Total at 0xA5)

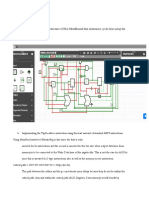

ASelALU

OutA

Register

0

8 A

8 OutALU

1

File

8 ALU

8

0

( Project1 OutB B OutFlag

1

Part2a )

4 4

BSelALU Z C N O

FunSel

2 2 2 4

OutASel Cin Flag Register

OutBSel

FunSel

RegSel

MUX

1 0 MemMuxSel

Address OutD

Register 8

I File Address

MUX 8 OutC 8

( Project1 Memory

Part2b )

OutCSel 2 2 2 3

OutDSel

FunSel

RegSel

I

8

L/H

Enable IR(8-15) IR(0-7)

FunSel (Project1 Part2c)

2

8 8

IR (0-7)

IR (8-15)

Figure 1: Organization of the Computer (OutDSel has the same configuration as OutCSel in Project1

Part2b)

Anda mungkin juga menyukai

- Exam 1: EE319K Spring 2013 Exam 1 (Practice 1)Dokumen6 halamanExam 1: EE319K Spring 2013 Exam 1 (Practice 1)SRITHA PBelum ada peringkat

- Assignment 4 (10 Marks) : Online Submission Is Accepted ONLY. You May Scan Your Submission and Upload in BBDokumen2 halamanAssignment 4 (10 Marks) : Online Submission Is Accepted ONLY. You May Scan Your Submission and Upload in BBMahirChoudhuryBelum ada peringkat

- Assembler Dependent FeaturesDokumen25 halamanAssembler Dependent FeaturesManasa100% (2)

- MicroControllers HandbookDokumen13 halamanMicroControllers Handbookjhon doeBelum ada peringkat

- CombinepdfDokumen14 halamanCombinepdfDuoDrenchBelum ada peringkat

- Table 1a: The Complete MSP430 Instruction Set of 27 Core InstructionsDokumen9 halamanTable 1a: The Complete MSP430 Instruction Set of 27 Core Instructionsmanjus46Belum ada peringkat

- IT 209 Summer 2019 Practise ExamDokumen10 halamanIT 209 Summer 2019 Practise ExamRishabh PatelBelum ada peringkat

- Coa 4th LessonDokumen23 halamanCoa 4th LessonMukeshBelum ada peringkat

- Midterm 1 SolutionDokumen6 halamanMidterm 1 SolutionsagarBelum ada peringkat

- 16 32 r0 RTN Program Counter or PC: CPE 221 Test 1 Solution Spring 2019Dokumen4 halaman16 32 r0 RTN Program Counter or PC: CPE 221 Test 1 Solution Spring 2019Kyra LathonBelum ada peringkat

- Outline: Microprocessor ProgrammingDokumen22 halamanOutline: Microprocessor ProgrammingGide BaniekBelum ada peringkat

- Mini MIPSDokumen6 halamanMini MIPSKeith NissankaBelum ada peringkat

- Pertemuan 7 Bahasa Rakitan: III: Matakuliah: T0324 / Arsitektur Dan Organisasi Komputer Tahun: 2005 Versi: 1Dokumen30 halamanPertemuan 7 Bahasa Rakitan: III: Matakuliah: T0324 / Arsitektur Dan Organisasi Komputer Tahun: 2005 Versi: 1Ten Dian Novita SariBelum ada peringkat

- 18s Cpe221 Test1 SolutionDokumen4 halaman18s Cpe221 Test1 SolutionKyra LathonBelum ada peringkat

- SR30 - Modbus MapDokumen9 halamanSR30 - Modbus MapMuathBelum ada peringkat

- Part A - 1 - 2 - 3 - 4 - 5Dokumen15 halamanPart A - 1 - 2 - 3 - 4 - 5Dr. Anoop B KBelum ada peringkat

- Lecture 21Dokumen10 halamanLecture 21VINAYBelum ada peringkat

- CEG 2136 - Fall 2009 - Final PDFDokumen7 halamanCEG 2136 - Fall 2009 - Final PDFAmin DhouibBelum ada peringkat

- Ee445M: Embedded and Real Time Systems: Study Guide Set #01Dokumen4 halamanEe445M: Embedded and Real Time Systems: Study Guide Set #01hilgadBelum ada peringkat

- Ee445M: Embedded and Real Time Systems: Study Guide Set #01Dokumen4 halamanEe445M: Embedded and Real Time Systems: Study Guide Set #01hilgadBelum ada peringkat

- Veccopy NoteDokumen7 halamanVeccopy NoteMd. Mizanur RahmanBelum ada peringkat

- 18f Cpe221 Test1 SolutionDokumen4 halaman18f Cpe221 Test1 SolutionKyra LathonBelum ada peringkat

- CSEN701 PA2 Solution 27172 29689Dokumen4 halamanCSEN701 PA2 Solution 27172 29689Sreeraj Pisharody100% (1)

- Computer Architechture ReportDokumen15 halamanComputer Architechture ReportNguyn LBelum ada peringkat

- Lab-8 Digital To Analog Converter: AIM: To Use The On Chip DAC To Generate Different Waveforms. DescriptionDokumen5 halamanLab-8 Digital To Analog Converter: AIM: To Use The On Chip DAC To Generate Different Waveforms. DescriptionSathvik S PrabhuBelum ada peringkat

- Lecture 22Dokumen8 halamanLecture 22VINAYBelum ada peringkat

- ES Module 2 NotesDokumen39 halamanES Module 2 NotesBhavana H NBelum ada peringkat

- ARM Prog Model 2 AddressingDokumen28 halamanARM Prog Model 2 AddressingSachin RajputBelum ada peringkat

- Instr Set PDFDokumen150 halamanInstr Set PDFvannybowoooBelum ada peringkat

- Sample Questions: Count - Zero Are in Registers R0, R1, R2, R3 RespectivelyDokumen5 halamanSample Questions: Count - Zero Are in Registers R0, R1, R2, R3 RespectivelyEmre CakmakyurduBelum ada peringkat

- Sample Questions: Count - Zero Are in Registers R0, R1, R2, R3 RespectivelyDokumen5 halamanSample Questions: Count - Zero Are in Registers R0, R1, R2, R3 RespectivelyEmre CakmakyurduBelum ada peringkat

- Mano CpuDokumen8 halamanMano Cpuarsalan ghasemianBelum ada peringkat

- Bommireddy Rambabu: MPMC Ii-UnitDokumen12 halamanBommireddy Rambabu: MPMC Ii-UnitrambabuBelum ada peringkat

- EEE 446 ISA Design Report: Instruction FormatsDokumen4 halamanEEE 446 ISA Design Report: Instruction FormatsАндрей МалаховBelum ada peringkat

- Microprocessor and Microcontrroller Module 1 - Calicut UniversityDokumen32 halamanMicroprocessor and Microcontrroller Module 1 - Calicut UniversityAshwin GopinathBelum ada peringkat

- Central Processing UnitDokumen49 halamanCentral Processing UnitFaizal KhanBelum ada peringkat

- Avr Set IntructionsDokumen160 halamanAvr Set IntructionsLuuLu Gaarciaa CeervaanteesBelum ada peringkat

- Atmel 0013Dokumen1 halamanAtmel 0013salarBelum ada peringkat

- CME331: Microprocessor, 2018-19, Term 1 Assignment 3: 10 MarksDokumen3 halamanCME331: Microprocessor, 2018-19, Term 1 Assignment 3: 10 MarksMahirChoudhuryBelum ada peringkat

- Lect5 Computer System ArchitectureDokumen18 halamanLect5 Computer System ArchitectureisaacwylliamBelum ada peringkat

- SBC (Subtract With Borrow)Dokumen36 halamanSBC (Subtract With Borrow)EnesVSBelum ada peringkat

- MC Part A Programs-UpdatedDokumen6 halamanMC Part A Programs-UpdatedM.A rajaBelum ada peringkat

- ALP-Embedded LabDokumen5 halamanALP-Embedded LabRuthvik ThumuluriBelum ada peringkat

- Lab3 Dec30043 18nov19Dokumen11 halamanLab3 Dec30043 18nov19Aizad FikrieBelum ada peringkat

- BH345 Final1Dokumen6 halamanBH345 Final1jakirakaBelum ada peringkat

- 5 PIC18 AddressingModes FSRs Table Part2Dokumen15 halaman5 PIC18 AddressingModes FSRs Table Part2Zain UL ABIDINBelum ada peringkat

- MTQP Emb Sys 2015 16Dokumen3 halamanMTQP Emb Sys 2015 16Rajasekhar MekalaBelum ada peringkat

- Chapter SevenDokumen29 halamanChapter Sevenremi1989Belum ada peringkat

- Atmega328 - P Avr Mcu With Picopower Technology - Seleção RegisterDokumen123 halamanAtmega328 - P Avr Mcu With Picopower Technology - Seleção RegisterclaudioandrevalverdeBelum ada peringkat

- 8051 Instruction Set SlidesDokumen72 halaman8051 Instruction Set SlidesNaWin NKBelum ada peringkat

- Arm ProcessorDokumen9 halamanArm ProcessorRahul AgarwalBelum ada peringkat

- MIPS OpcodesDokumen2 halamanMIPS OpcodesKnowledge SeekerBelum ada peringkat

- V Semester B.Tech (Electrical & Electronics Engineering) End Semester Examinations, November 2017Dokumen2 halamanV Semester B.Tech (Electrical & Electronics Engineering) End Semester Examinations, November 2017DuoDrenchBelum ada peringkat

- CPE 221 Final Exam Solution Fall 2018Dokumen6 halamanCPE 221 Final Exam Solution Fall 2018Kyra LathonBelum ada peringkat

- PC PC: PC+ 4+se (Imm 2) RT Field, Bits 20-16: Floating Point Instructions (FR Format, Even Regs Only)Dokumen1 halamanPC PC: PC+ 4+se (Imm 2) RT Field, Bits 20-16: Floating Point Instructions (FR Format, Even Regs Only)Hamza AsimBelum ada peringkat

- Module IV LOCDokumen21 halamanModule IV LOCrahulBelum ada peringkat

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDari EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationBelum ada peringkat

- Assembly Programming:Simple, Short, And Straightforward Way Of Learning Assembly LanguageDari EverandAssembly Programming:Simple, Short, And Straightforward Way Of Learning Assembly LanguagePenilaian: 5 dari 5 bintang5/5 (1)

- Model Exam - 1 Cs6303 CA - 19.02.18 Answer KeyDokumen8 halamanModel Exam - 1 Cs6303 CA - 19.02.18 Answer KeyJaga DeeshBelum ada peringkat

- CA04 2022S2 NewDokumen33 halamanCA04 2022S2 NewPhạm Hiếu AhiiBelum ada peringkat

- 8051 Microcontroller Instruction Set: Electronics HubDokumen12 halaman8051 Microcontroller Instruction Set: Electronics Hubibrar saqibBelum ada peringkat

- EKT Model Question Paper (Computer Science) - IIDokumen4 halamanEKT Model Question Paper (Computer Science) - IInixsBelum ada peringkat

- 8085 Microprocessor NotesDokumen44 halaman8085 Microprocessor Notesbob deoBelum ada peringkat

- 68HC11 Assembly ProgrammingDokumen50 halaman68HC11 Assembly ProgrammingAmine EssakenBelum ada peringkat

- Digital Signal Processors and Architectures (DSPA) Unit-2Dokumen92 halamanDigital Signal Processors and Architectures (DSPA) Unit-2Chaitanya DuggineniBelum ada peringkat

- Chapter 2 Topics: S R C R RTNDokumen41 halamanChapter 2 Topics: S R C R RTNMohammad Jamal AmratBelum ada peringkat

- 122 TextbookDokumen332 halaman122 Textbookarieljane06Belum ada peringkat

- Microprocessors 68HC11Dokumen20 halamanMicroprocessors 68HC11Juan Carlos LunaBelum ada peringkat

- CS401 Glossary CS401Dokumen7 halamanCS401 Glossary CS401hassan_m2222Belum ada peringkat

- EE6008 QB RejinpaulDokumen3 halamanEE6008 QB RejinpaulBoobalan SriBelum ada peringkat

- Mp8th UnitDokumen40 halamanMp8th UnitPankaj GaonkarBelum ada peringkat

- Computer Organization and Architecture (Coa) : EET 2211 4 Semester - Cse & Csit Overview of 8086 MicroprocessorDokumen59 halamanComputer Organization and Architecture (Coa) : EET 2211 4 Semester - Cse & Csit Overview of 8086 MicroprocessorDibyanshu AmanBelum ada peringkat

- Nvis 5586A FinalDokumen191 halamanNvis 5586A FinalSaiKumarBelum ada peringkat

- NESDocDokumen47 halamanNESDocJeff RudBelum ada peringkat

- MIC Solved Questions BankDokumen14 halamanMIC Solved Questions BankAdvait kamthekarBelum ada peringkat

- CS252 Midterm ElmaDokumen4 halamanCS252 Midterm Elmafadwa badiBelum ada peringkat

- 8085 Addressing Modes and Memory MappingDokumen8 halaman8085 Addressing Modes and Memory MappingRocky SamratBelum ada peringkat

- Overview or Features of 8086Dokumen33 halamanOverview or Features of 8086Supraja SundaresanBelum ada peringkat

- Unit 1 MPMC NotesDokumen40 halamanUnit 1 MPMC NotesRohit Venkat PawanBelum ada peringkat

- Chapter 3Dokumen283 halamanChapter 3Biruk DawitBelum ada peringkat

- DSP C16 - UNIT-6 (Ref-2)Dokumen26 halamanDSP C16 - UNIT-6 (Ref-2)Vaishnavi. KoyaBelum ada peringkat

- Vol 2 BDokumen416 halamanVol 2 Bom_dinuBelum ada peringkat

- BLOCKTRANSFERANDSEARCHDokumen7 halamanBLOCKTRANSFERANDSEARCHNaomi Aira Gole CruzBelum ada peringkat

- Hand Held 1747 PT1Dokumen486 halamanHand Held 1747 PT1Ismael Sanchez HernandezBelum ada peringkat

- RouthDokumen102 halamanRouthAvinashBelum ada peringkat

- PIC12F675 I P MicrochipDokumen132 halamanPIC12F675 I P MicrochipSintesoftBelum ada peringkat

- ECE 212 Lecture 1Dokumen9 halamanECE 212 Lecture 1jchipchuBelum ada peringkat

- Hcs12 Instruction Set SummaryDokumen15 halamanHcs12 Instruction Set SummaryRedduan HarisBelum ada peringkat