Assignment Week4

Diunggah oleh

saigdv1978100%(2)100% menganggap dokumen ini bermanfaat (2 suara)

184 tayangan3 halamanThe document provides solutions to 9 multiple choice questions about Verilog concepts. Question 1 asks about valid targets for procedural assignment statements and the answer is that a "wire" type variable cannot be assigned. Question 2 provides code to calculate the final value of variable "c", which is 75. Question 3 is similar but uses non-blocking assignments, with the final value of "c" being 65.

Deskripsi Asli:

This is the solution for week 4 assignment in nptel

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniThe document provides solutions to 9 multiple choice questions about Verilog concepts. Question 1 asks about valid targets for procedural assignment statements and the answer is that a "wire" type variable cannot be assigned. Question 2 provides code to calculate the final value of variable "c", which is 75. Question 3 is similar but uses non-blocking assignments, with the final value of "c" being 65.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

100%(2)100% menganggap dokumen ini bermanfaat (2 suara)

184 tayangan3 halamanAssignment Week4

Diunggah oleh

saigdv1978The document provides solutions to 9 multiple choice questions about Verilog concepts. Question 1 asks about valid targets for procedural assignment statements and the answer is that a "wire" type variable cannot be assigned. Question 2 provides code to calculate the final value of variable "c", which is 75. Question 3 is similar but uses non-blocking assignments, with the final value of "c" being 65.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 3

Week 4: Assignment Solutions

1. Which of the following cannot be used as the target of a procedural

assignment statement?

a. A part select of a “reg” type variable.

b. An “integer” type variable.

c. An output signal of a module that is also declared as “reg”.

d. A “wire” type variable.

Correct answer is (d).

In a procedural assignment statement, only register type variables or part

select thereof can be used in the left hand side. A wire type variable

cannot be assigned a value within a procedural block.

2. For the following code segment, the final value of variable “c” will be

…………..

integer a, b, c;

initial

begin

a = 55; b = 10; c = 5;

a = b * c;

b = a – 25;

c = a + b;

end

Correct answer is 75.

In blocking assignments, statements are executed one after the other.

First assignment: a = 10 * 5 = 50

Second assignment: b = 50 – 25 = 25

Third assignment: c = 50 + 25 = 75

3. For the following code segment, the final value of variable “c” will be

…………..

integer a, b, c;

initial

begin

a = 55; b = 10; c = 5;

end

initial

begin

a <= #10 b * c;

b <= #10 a – 25;

c <= #10 a + b;

end

Correct answer is 65.

In non-blocking statements inside a procedural block, all right hand side

expressions are evaluated in parallel, and are assigned to the left hand side

variables all together.

First assignment: a = 10 * 5 = 50

Second assignment: b = 55 – 25 = 30

Third assignment: c = 55 + 10 = 65

4. What will the following code segment do?

always @(posedge clock)

begin

red = blue;

blue = red;

end

a. Exchange the values of the variables “red” and “blue”.

b. Both variables will get the value previously stored in “red”.

c. Both variables will get the value previously stored in “blue”.

d. None of the above.

Correct answer is (c).

Because the assignments are blocking, first, the value of “blue” will be

assigned to “red”, and then the new value of “red” will be assigned to

“blue”. Thus both the variables “red” and “blue” will get the previous value

stored in “blue”.

5. If the 8-bit variable “data” declared as “reg [7:0] data” is initialized to

8’b10100110, what will be its value after execution of the following code

segment?

always @(posedge clock)

begin

data = data << 1;

data[0] = data[7];

end

a. 8’b01001100

b. 8’b01001101

c. 8’b11001101

d. 8’b11001100

Correct answer is (a).

First data is left shifted by 1 position; its value will become 8’b01001100.

Then data[7], which is 0, is assigned to data[0], which is also 0. So there

will be no change, and the value will remain 8’b01001100.

6. What will the following code segment generate on synthesis, assuming

that the four variables y0, y1, y2 and y3 map into four latches / flip-flops?

always @(posedge clock)

begin

y3 = in;

y2 = y3;

y1 = y2;

y0 = y1;

end

a. A 4-bit shift register.

b. A 4-bit parallel-in parallel-out register.

c. Four D flip-flops all fed with the data “in”.

d. None of the above.

Correct answer is (c).

Since blocking assignment statements are executed one after another,

the value of “in” will be first assigned to “y3”, then to “y2”, then to “y1”,

and finally to “y0”. So the same input will feed all the four D flip-flops

in the synthesized circuit.

7. What will the following code segment generate on synthesis?

always @(posedge clock)

begin

y3 <= in;

y2 <= y3;

y1 <= y2;

y0 <= y1;

end

a. A 4-bit shift register.

b. A 4-bit parallel-in parallel-out register.

c. Four D flip-flops all fed with the data “in”.

d. None of the above.

Correct answer is (a).

Since we use non-blocking assignments, the values on the RHS are

assigned to the variables on the LHS in synchronism with the clock. This

will generate a 4-bit shift register.

8. Which of the following are true for “generate” blocks?

a. Multiple copies of code blocks are generated dynamically before

simulation or synthesis.

b. Can be used to instantiate multiple copies of some module.

c. Must be used along with a variable of type “genvar”.

d. None of the above.

Correct answersare (a), (b) and (c).

All of (a), (b) and (c) are true for “generate” blocks.

9. Which of the following are false for user defined primitives in Verilog?

a. Can be used to specify a combinational circuit with any number of

outputs.

b. Can be used to specify a finite state machine with one or two state

variables.

c. Don’t care or unspecified values are not allowed in the description.

d. None of the above.

Correct answer is (a), (b) and (c).

We can specify a combinational circuit with only one output.

We can specify a FSM with only one state variable.

We can use don’t care (denoted by “?”) to make the description more

compact.

Anda mungkin juga menyukai

- Solution of Quiz 3Dokumen5 halamanSolution of Quiz 3Pranavkumar PatilBelum ada peringkat

- Verilog SolnDokumen15 halamanVerilog Solngannoju423100% (1)

- Assignments Week02Dokumen4 halamanAssignments Week02vidhya dsBelum ada peringkat

- Hardware Modeling Using Verilog Assignment-Week 5Dokumen7 halamanHardware Modeling Using Verilog Assignment-Week 5krishna414100% (1)

- Hardware Modeling Using Verilog Assignment-Week 4Dokumen7 halamanHardware Modeling Using Verilog Assignment-Week 4krishna4140% (1)

- Hardware Modeling Using Verilog Assignment-Week 2Dokumen5 halamanHardware Modeling Using Verilog Assignment-Week 2krishna414Belum ada peringkat

- Hardware Modeling Using Verilog Assignment-Week 3Dokumen6 halamanHardware Modeling Using Verilog Assignment-Week 3krishna41450% (2)

- Verilog Objective TestDokumen5 halamanVerilog Objective Testsushmitha v100% (1)

- Assignments Week04Dokumen5 halamanAssignments Week04HARIPRASATH ECE0% (2)

- Ee 241 Digital Circuits Final Exam Solution ManualDokumen10 halamanEe 241 Digital Circuits Final Exam Solution ManualkdrdBelum ada peringkat

- Week 04 Assignment 04Dokumen4 halamanWeek 04 Assignment 04Modicare QuiteBelum ada peringkat

- Department of Electronics and Communication 8051 Microcontroller and Interfacing Objective Questions and Answers Iii Year Unit - IDokumen20 halamanDepartment of Electronics and Communication 8051 Microcontroller and Interfacing Objective Questions and Answers Iii Year Unit - IdeptBelum ada peringkat

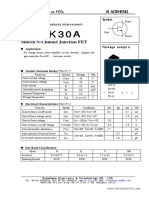

- K30a PDFDokumen1 halamanK30a PDFVictorManuelBernalBlancoBelum ada peringkat

- Hardware Modeling Using Verilog - Unit 2 - Week 1 AssignmentDokumen3 halamanHardware Modeling Using Verilog - Unit 2 - Week 1 AssignmentgudduBelum ada peringkat

- Lecture by Navakanta BhattDokumen33 halamanLecture by Navakanta BhattVivek RoyBelum ada peringkat

- Verification Test Question Paper - MavenDokumen4 halamanVerification Test Question Paper - Mavenaman nigamBelum ada peringkat

- Path SensitizationDokumen4 halamanPath SensitizationTarun SinghBelum ada peringkat

- Pseudo Random Sequence Generator in VerilogDokumen3 halamanPseudo Random Sequence Generator in VerilogAhmed AbduljabbarBelum ada peringkat

- Up Down CounterDokumen20 halamanUp Down Countersumi36117Belum ada peringkat

- DDDC87ECAA084E5DA4D2D77F7DC80391Dokumen5 halamanDDDC87ECAA084E5DA4D2D77F7DC80391Sameer NandagaveBelum ada peringkat

- DV FinalDokumen27 halamanDV FinalAnusha ChidagniBelum ada peringkat

- Introduction To Cryptography: Homework 4: Alvin Lin January 2018 - May 2018Dokumen6 halamanIntroduction To Cryptography: Homework 4: Alvin Lin January 2018 - May 2018Nguyễn Quang MinhBelum ada peringkat

- (Up, Down and Modn) CountersDokumen76 halaman(Up, Down and Modn) CountersAashik ShaikBelum ada peringkat

- Logic Circuits Midterm ReviewerDokumen38 halamanLogic Circuits Midterm ReviewerHector Ledesma IIIBelum ada peringkat

- Verilog HDL: ModuleDokumen9 halamanVerilog HDL: ModuleAvinash ReddyBelum ada peringkat

- Verilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation PrinciplesDokumen3 halamanVerilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation PrinciplesSindhu RajanBelum ada peringkat

- تجميعات المعالجات1Dokumen104 halamanتجميعات المعالجات1GaBelum ada peringkat

- Solved - The MediQuick Lab Has Three Lab Technicians Available T... - Chegg - Comd PDFDokumen3 halamanSolved - The MediQuick Lab Has Three Lab Technicians Available T... - Chegg - Comd PDFDiego Castro100% (1)

- Noc18 cs48 Assignment3Dokumen4 halamanNoc18 cs48 Assignment3shweta100% (1)

- Haredare Modeling Using Verilog Assignment-Week 1Dokumen6 halamanHaredare Modeling Using Verilog Assignment-Week 1krishna414Belum ada peringkat

- 1 Number SystemDokumen14 halaman1 Number SystemhemanthBelum ada peringkat

- Chap 6 RandomizationDokumen73 halamanChap 6 RandomizationravichettyraviBelum ada peringkat

- Verilog Palnitkar Solutions Chapter 9Dokumen13 halamanVerilog Palnitkar Solutions Chapter 9Aahnaf Mustafiz 1631698043Belum ada peringkat

- Assignment-8 Solution July 2019Dokumen8 halamanAssignment-8 Solution July 2019sudhirBelum ada peringkat

- Baugh Wooley MultiplierDokumen4 halamanBaugh Wooley MultiplierPavithran ThiyyanoorBelum ada peringkat

- Lab2 VerilogDokumen5 halamanLab2 VerilogHải TrầnBelum ada peringkat

- Digital Image Processing Assignment-Week 2: NPTEL Online Certification Courses Indian Institute of Technology KharagpurDokumen12 halamanDigital Image Processing Assignment-Week 2: NPTEL Online Certification Courses Indian Institute of Technology KharagpurPandu KBelum ada peringkat

- Ver I Log ExamplesDokumen22 halamanVer I Log ExamplesDayanand Gowda KrBelum ada peringkat

- Brent Kung Adder 16 Bit Full CodeDokumen8 halamanBrent Kung Adder 16 Bit Full CodeShavel Kumar100% (2)

- HDL Manual 2020 5th Sem E&CE 18ECL58Dokumen74 halamanHDL Manual 2020 5th Sem E&CE 18ECL58vishvakiranaBelum ada peringkat

- Digital Circuits For GATE ExamDokumen15 halamanDigital Circuits For GATE ExamSAMIT KARMAKAR100% (1)

- 4bit Array MultiplierDokumen4 halaman4bit Array MultiplierRahul TiwariBelum ada peringkat

- Digital System Objective QuestionsDokumen17 halamanDigital System Objective QuestionsRanjeet pratap singh bhadoriyaBelum ada peringkat

- D Cube TestingDokumen48 halamanD Cube TestingVinod Khera100% (1)

- Philips Placement Papers 1305641447Dokumen16 halamanPhilips Placement Papers 1305641447Prateek Prabhash100% (1)

- Assignment 3Dokumen5 halamanAssignment 3Rahi SarkarBelum ada peringkat

- DAA Lab Manual VTUDokumen41 halamanDAA Lab Manual VTUManohar NV100% (2)

- Design and Verification of AMBA AHBDokumen6 halamanDesign and Verification of AMBA AHBrishi tejuBelum ada peringkat

- Introduction To Machine Learning - IITKGP - Unit 4 - Week 2Dokumen5 halamanIntroduction To Machine Learning - IITKGP - Unit 4 - Week 2Priya VenkadachalamBelum ada peringkat

- Verilog Parameters and OperatorsDokumen25 halamanVerilog Parameters and OperatorsR INI BHANDARIBelum ada peringkat

- Sample Question Paper 1 - PFDokumen11 halamanSample Question Paper 1 - PFRaJu SinGhBelum ada peringkat

- Timing Design in Digital Systems: Dr. Paul D. FranzonDokumen24 halamanTiming Design in Digital Systems: Dr. Paul D. FranzonMaheshBelum ada peringkat

- Digital Electronics (MCQ) PART-1Dokumen7 halamanDigital Electronics (MCQ) PART-101ABHIGYAN MAJIBelum ada peringkat

- Lab 4Dokumen25 halamanLab 4Santosh Kumar100% (1)

- Assignment-7 Solution July 2019Dokumen5 halamanAssignment-7 Solution July 2019sudhirBelum ada peringkat

- Assignment Solution Week3Dokumen3 halamanAssignment Solution Week3HARIPRASATH ECEBelum ada peringkat

- Solution of Quiz 2Dokumen4 halamanSolution of Quiz 2Pranavkumar PatilBelum ada peringkat

- Solution of Quiz 5Dokumen5 halamanSolution of Quiz 5Pranavkumar PatilBelum ada peringkat

- Questions&AnswersDokumen8 halamanQuestions&AnswersECEII 065Belum ada peringkat

- Week 7: Assignment SolutionsDokumen5 halamanWeek 7: Assignment SolutionsPushpalathaBelum ada peringkat

- VHDL Lab ManualDokumen51 halamanVHDL Lab Manualsaigdv1978Belum ada peringkat

- (Ercegovac Milos D., Lang Tomas) Digital Arithmeti (B-Ok - Xyz)Dokumen731 halaman(Ercegovac Milos D., Lang Tomas) Digital Arithmeti (B-Ok - Xyz)saigdv1978Belum ada peringkat

- Week 2 Course MaterialDokumen60 halamanWeek 2 Course Materialsaigdv1978Belum ada peringkat

- Memory Structures DRAM CellsDokumen14 halamanMemory Structures DRAM Cellssaigdv1978Belum ada peringkat

- Week 1 Lecture MaterialDokumen96 halamanWeek 1 Lecture Materialsaigdv1978Belum ada peringkat

- 6th Central Pay Commission Salary CalculatorDokumen15 halaman6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Either Source or Destination Is One Of: CPU RegisterDokumen81 halamanEither Source or Destination Is One Of: CPU Registersaigdv1978Belum ada peringkat

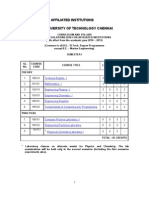

- Digital System Design & Digital Ic ApplicationsDokumen4 halamanDigital System Design & Digital Ic Applicationssaigdv1978Belum ada peringkat

- Wireless Sensor Networks SyllabusDokumen3 halamanWireless Sensor Networks Syllabussaigdv19780% (1)

- Embedded Software in C For ARM Cortex MDokumen114 halamanEmbedded Software in C For ARM Cortex MMohamedHassanBelum ada peringkat

- GPRS and GPS Based Vehicle TrackingDokumen1 halamanGPRS and GPS Based Vehicle Trackingsaigdv1978Belum ada peringkat

- Arduino Based Home Automation System Using Bluetooth Through An Android Mobile PDFDokumen72 halamanArduino Based Home Automation System Using Bluetooth Through An Android Mobile PDFsaigdv197859% (17)

- Ramachandra College of EngineeringDokumen1 halamanRamachandra College of Engineeringsaigdv1978Belum ada peringkat

- Switching Theory and Logic DesignDokumen2 halamanSwitching Theory and Logic Designsaigdv1978Belum ada peringkat

- Ramachandra College of EngineeringDokumen1 halamanRamachandra College of Engineeringsaigdv1978Belum ada peringkat

- Microprosser 8085Dokumen15 halamanMicroprosser 8085saigdv1978Belum ada peringkat

- Simulink Support Package For ArduinoDokumen4 halamanSimulink Support Package For ArduinofredBelum ada peringkat

- Cobol Programming Language: Hello, WorldDokumen5 halamanCobol Programming Language: Hello, WorldKarl Juno TernateBelum ada peringkat

- Design of Absolute LoaderDokumen3 halamanDesign of Absolute Loaderakbisoi160% (5)

- CPP SlidesDokumen231 halamanCPP Slidesapi-3711149Belum ada peringkat

- CS201 Latest Solved MCQsDokumen27 halamanCS201 Latest Solved MCQscs619finalproject.com91% (11)

- Input and Output Functions in CDokumen10 halamanInput and Output Functions in Capi-19417993Belum ada peringkat

- Test Bank For Introduction To Java Programming Comprehensive Version 10Th Edition Liang 0133761312 9780133761313 Full Chapter PDFDokumen36 halamanTest Bank For Introduction To Java Programming Comprehensive Version 10Th Edition Liang 0133761312 9780133761313 Full Chapter PDFjessica.talaga212100% (10)

- Exam 1 QuestionsDokumen10 halamanExam 1 Questionsanand.pasunooriBelum ada peringkat

- Exercises On CollectionsDokumen5 halamanExercises On CollectionsKamal WaliaBelum ada peringkat

- OpenFOAM Developer Course GuideDokumen105 halamanOpenFOAM Developer Course GuideAnonymous x2QqBMq2Belum ada peringkat

- Asynchronous Programming Patterns PDFDokumen151 halamanAsynchronous Programming Patterns PDFTrueKwasirBelum ada peringkat

- Airplane Automation SystemDokumen34 halamanAirplane Automation SystemmohdaqiBelum ada peringkat

- First TestDokumen14 halamanFirst TestNeha VermaBelum ada peringkat

- MSP430™ FRAMTechnology - HowTo and BestPracticesDokumen21 halamanMSP430™ FRAMTechnology - HowTo and BestPractices呂柏勳Belum ada peringkat

- 2010 First Yr First I Sem SyllabusDokumen36 halaman2010 First Yr First I Sem SyllabusNarayana SwamyBelum ada peringkat

- Subprogram (Robert Text)Dokumen109 halamanSubprogram (Robert Text)Lini IckappanBelum ada peringkat

- Operating Systems (MCQ)Dokumen26 halamanOperating Systems (MCQ)Mian Hasham Azhar AZHARBelum ada peringkat

- R11 Extension TablesDokumen16 halamanR11 Extension TablesManikumar KollaBelum ada peringkat

- Systemverilog Systemverilog Dpi: (Direct Programming Interface)Dokumen63 halamanSystemverilog Systemverilog Dpi: (Direct Programming Interface)LiudeBelum ada peringkat

- USB 4671 ManualDokumen118 halamanUSB 4671 ManualJulio OcampoBelum ada peringkat

- DevGuru VBScript QuickrefDokumen307 halamanDevGuru VBScript QuickrefMugurel AnghelBelum ada peringkat

- Open Bravo 1Dokumen3 halamanOpen Bravo 1MD ABUL KHAYERBelum ada peringkat

- C Interview QuestionsDokumen5 halamanC Interview QuestionsVignesh GuruBelum ada peringkat

- Genre AnalysisDokumen8 halamanGenre Analysisapi-302324538Belum ada peringkat

- GIS Assignment OneDokumen3 halamanGIS Assignment OnejhankarBelum ada peringkat

- DB2 Stored ProceduresDokumen8 halamanDB2 Stored Proceduresshwetamande5Belum ada peringkat

- Global Edge Software - Intimation Circular PDFDokumen1 halamanGlobal Edge Software - Intimation Circular PDFSIVAKUMAR REDDY GOTIKEBelum ada peringkat

- Hundred Sap HR FaqDokumen3 halamanHundred Sap HR FaqjaveedsamdaniBelum ada peringkat

- Unix and Linux Programming FileDokumen20 halamanUnix and Linux Programming FilejfkajlfjBelum ada peringkat