Lecture 11 COMP2611 Processor Part3

Diunggah oleh

jnfzHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Lecture 11 COMP2611 Processor Part3

Diunggah oleh

jnfzHak Cipta:

Format Tersedia

1

4. Pipeline Hazards

COMP2611 CSE HKUST The Processor: Datapath & Control

Dependences in Programs 2

Data dependence

Example: lw $1, 200($2)

add $3, $4, $1

add can’t do ID (i.e., read register $1) until lw updates $1

Control dependence

Example: bne $1, $2, target

add $3, $4, $5

next IF can’t start until bne completes the comparison

These dependences may cause the pipeline not be fully filled

Execution stops to wait for data or control to be produced

next instruction cannot be executed in next cycle

COMP2611 CSE HKUST The Processor: Datapath & Control

Pipeline Hazards 3

Hazards are situations in pipelining when the next instruction cannot

be executed in the following clock cycle.

Three types of pipelined hazards

Structural hazards: A required resource is busy

Data hazards: Need to wait for previous instruction to complete

its data read/write

Control hazards: Deciding on control action depends on previous

instruction

Hazards can always be resolved by waiting. But this slows down

the pipeline.

COMP2611 CSE HKUST The Processor: Datapath & Control

Structural Hazards: Memory 4

Instruction order

instr #1 IF ID EXE MEM WB

instr #2 IF ID EXE MEM WB

instr #3 IF ID EXE MEM WB

instr #4 IF ID EXE MEM WB

instr #5 IF ID EXE MEM WB

Conflict for use of memory

In MIPS pipeline with a single memory

Load/store requires data access

Instruction fetch would have to stall for that cycle

Would cause a pipeline “bubble”

Hence, pipelined datapaths require separate instruction/data memories

Or separate instruction/data caches

COMP2611 CSE HKUST The Processor: Datapath & Control

Structural Hazards: Registers 5

Instruction order instr #1 IF ID EXE MEM WB

instr #2 IF ID EXE MEM WB

instr #3 IF ID EXE MEM WB

instr #4 IF ID EXE MEM WB

instr #5 IF ID EXE MEM WB

Fact: Register access VERY fast. Takes half the time of ALU stage or less

always Write to registers during 1st half of each clock cycle

always Read from Registers during 2nd half of each clock cycle

Register file supports Write and Read during same clock cycle (in this

order)

COMP2611 CSE HKUST The Processor: Datapath & Control

Data Hazard 6

An instruction depends on completion of data access by a previous

instruction

add $s0, $t0, $t1

sub $t2, $s0, $t3

a bubble or pipeline stall is a delay in execution of an instruction in

an instruction pipeline in order to resolve a hazard.

COMP2611 CSE HKUST The Processor: Datapath & Control

Forwarding(aka Bypassing) 7

Forwarding partially solves the data hazard problem

Use result when it is computed

Don’t wait for it to be stored in a register

Requires extra connections in the datapath

COMP2611 CSE HKUST The Processor: Datapath & Control

Load-Use Data Hazard 8

Can’t always avoid stalls by forwarding

If value not computed when needed

Can’t forward backward in time!

lw $s0, 20($t1)

sub $t2, $s0, $t3

COMP2611 CSE HKUST The Processor: Datapath & Control

Code Scheduling to Avoid Stalls 9

Consider this code sequence

a = b + c;

d = b + e;

Assume a to e are stored in memory address 0($t0), 4($t0),

8($t0),12($t0)and 16($t0)respectively. Assume forwarding is

used.

lw $t1, 0($t0) lw $t1, 0($t0)

lw $t2, 4($t0) lw $t2, 4($t0)

stall add $t3, $t1, $t2 lw $t4, 8($t0)

sw $t3, 12($t0) add $t3, $t1, $t2

lw $t4, 8($t0) sw $t3, 12($t0)

stall add $t5, $t1, $t4 add $t5, $t1, $t4

sw $t5, 16($t0) sw $t5, 16($t0)

13 cycles 11 cycles

COMP2611 CSE HKUST The Processor: Datapath & Control

Control Hazards 10

Branch determines flow of control

Fetching next instruction depends on branch outcome

Pipeline can’t always fetch correct instruction

Still working on ID stage of branch

In MIPS pipeline

Need to compare registers and compute target early in the

pipeline

Add hardware to do it in ID stage

COMP2611 CSE HKUST The Processor: Datapath & Control

Stall on Branch 11

Wait until branch outcome determined before fetching

next instruction

COMP2611 CSE HKUST The Processor: Datapath & Control

Branch Prediction 12

Longer pipelines can’t readily determine branch outcome

early

Stall penalty becomes unacceptable

Predict outcome of branch

Only stall if prediction is wrong

In MIPS pipeline

Can predict branches not taken

Fetch instruction after branch, with no delay

COMP2611 CSE HKUST The Processor: Datapath & Control

MIPS with Static Branch Prediction (Not Taken) 13

Prediction

correct

Prediction

incorrect

COMP2611 CSE HKUST The Processor: Datapath & Control

Pipeline Summary 14

The BIG Picture

Pipelining improves performance by increasing instruction

throughput

Executes multiple instructions in parallel

Each instruction has the same latency

Subject to hazards

Structure, data, control

Instruction set design affects complexity of pipeline

implementation

COMP2611 CSE HKUST The Processor: Datapath & Control

15

5. Pipeline Datapath with Hazards

COMP2611 CSE HKUST The Processor: Datapath & Control

Data Hazards in ALU Instructions 16

Consider this sequence:

sub $2, $1,$3

and $12,$2,$5

or $13,$6,$2

add $14,$2,$2

sw $15,100($2)

We can resolve hazards with forwarding

How do we detect when to forward?

COMP2611 CSE HKUST The Processor: Datapath & Control

Dependencies and Forwarding 17

From the figure the decision is simple (required “forwardings” are

represented by the two red lines):

COMP2611 CSE HKUST The Processor: Datapath & Control

Detecting the Need to Forward 18

Pass register numbers along pipeline

e.g., ID/EX.RegisterRs = register number for Rs sitting

in ID/EX pipeline register

ALU operand register numbers in EX stage are

given by

ID/EX.RegisterRs, ID/EX.RegisterRt

Data hazards when

1a. EX/MEM.RegisterRd = ID/EX.RegisterRs Fwd from

EX/MEM

1b. EX/MEM.RegisterRd = ID/EX.RegisterRt pipeline reg

2a. MEM/WB.RegisterRd = ID/EX.RegisterRs Fwd from

2b. MEM/WB.RegisterRd = ID/EX.RegisterRt MEM/WB

pipeline reg

COMP2611 CSE HKUST The Processor: Datapath & Control

Detecting the Need to Forward (cont.) 19

But only if forwarding instruction will write to a register!

EX/MEM.RegWrite, MEM/WB.RegWrite

And only if Rd for that instruction is not $zero

EX/MEM.RegisterRd≠ 0,

MEM/WB.RegisterRd ≠ 0

COMP2611 CSE HKUST The Processor: Datapath & Control

Forwarding Paths 20

Forwarding always takes place to EX stage

❍ Implementing these conditions in a forwarding control unit

❍ Using two multiplexers to decide what is the input of operands A and B

of the ALU

COMP2611 CSE HKUST The Processor: Datapath & Control

Forwarding Conditions 21

EX hazard

if (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0)

and (EX/MEM.RegisterRd = ID/EX.RegisterRs))

ForwardA = 10

if (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0)

and (EX/MEM.RegisterRd = ID/EX.RegisterRt))

ForwardB = 10

MEM hazard

if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)

and (MEM/WB.RegisterRd = ID/EX.RegisterRs))

ForwardA = 01

if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)

and (MEM/WB.RegisterRd = ID/EX.RegisterRt))

ForwardB = 01

COMP2611 CSE HKUST The Processor: Datapath & Control

Double Data Hazard 22

Consider the sequence:

add $1,$1,$2

add $1,$1,$3

add $1,$1,$4

Both hazards occur

Want to use the most recent

Revise MEM hazard condition

Only fwd if EX hazard condition isn’t true

COMP2611 CSE HKUST The Processor: Datapath & Control

Revised Forwarding Condition 23

MEM hazard

if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)

and not (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0)

and (EX/MEM.RegisterRd = ID/EX.RegisterRs))

and (MEM/WB.RegisterRd = ID/EX.RegisterRs))

ForwardA = 01

if (MEM/WB.RegWrite and (MEM/WB.RegisterRd ≠ 0)

and not (EX/MEM.RegWrite and (EX/MEM.RegisterRd ≠ 0)

and (EX/MEM.RegisterRd = ID/EX.RegisterRt))

and (MEM/WB.RegisterRd = ID/EX.RegisterRt))

ForwardB = 01

COMP2611 CSE HKUST The Processor: Datapath & Control

Datapath with Forwarding 24

COMP2611 CSE HKUST The Processor: Datapath & Control

Load-Use Data Hazard 25

Need to stall

for one cycle

COMP2611 CSE HKUST The Processor: Datapath & Control

Load-Use Hazard Detection 26

Check when using instruction is decoded in ID stage

ALU operand register numbers in ID stage are given by

IF/ID.RegisterRs, IF/ID.RegisterRt

Load-use hazard when

ID/EX.MemRead and

((ID/EX.RegisterRt = IF/ID.RegisterRs) or

(ID/EX.RegisterRt = IF/ID.RegisterRt))

If detected, stall and insert bubble

COMP2611 CSE HKUST The Processor: Datapath & Control

How to Stall the Pipeline 27

Force control values in ID/EX register to 0

EX, MEM and WB do nop (no-operation)

Prevent update of PC and IF/ID register

Using instruction is decoded again

Following instruction is fetched again

1-cycle stall allows MEM to read data for lw

Can subsequently forward to EX stage

COMP2611 CSE HKUST The Processor: Datapath & Control

Stall/Bubble in the Pipeline 28

Stall inserted

here

COMP2611 CSE HKUST The Processor: Datapath & Control

Stall/Bubble in the Pipeline (cont.) 29

Or, more

accurately…

COMP2611 CSE HKUST The Processor: Datapath & Control

Datapath with Hazard Detection 30

Zero input

to create a

nop

operation

COMP2611 CSE HKUST The Processor: Datapath & Control

Stalls and Performance 31

The BIG Picture

Stalls reduce performance

But are required to get correct results

Compiler can arrange code to avoid hazards and stalls

Requires knowledge of the pipeline structure

COMP2611 CSE HKUST The Processor: Datapath & Control

Branch Hazards 32

If branch outcome determined in MEM

Flush these

instructions

(Set control

values to 0)

PC

COMP2611 CSE HKUST The Processor: Datapath & Control

Reducing Branch Delay 33

Add hardware to the MIPS pipeline to determine the branch result in

the ID stage

Target address calculation requires an adder

Register comparator

An example (assume branch taken)

36: sub $10, $4, $8

40: beq $1, $3, 7 #PC relative branch to

44: and $12, $2, $5 40+4+4*7=72

48: or $13, $2, $6

52: add $14, $4, $2

56: slt $15, $6, $7

...

72: lw $4, 50($7)

COMP2611 CSE HKUST The Processor: Datapath & Control

Example: Branch Taken 34

Target address

calculator and

Register

comparator

COMP2611 CSE HKUST The Processor: Datapath & Control

Example: Branch Taken (cont.) 35

IF.Flush flushes

the “and”

instruction.

COMP2611 CSE HKUST The Processor: Datapath & Control

Data Hazards for Branches: Example 1 36

Branch instruction depends on data value (in register) to

make decision, therefore it is prone to data hazards.

If a comparison register is a destination of 2nd or 3rd

preceding ALU instruction

add $1, $2, $3 IF ID EX MEM WB

add $4, $5, $6 IF ID EX MEM WB

… IF ID EX MEM WB

beq $1, $4, target IF ID EX MEM WB

Can resolve using forwarding

COMP2611 CSE HKUST The Processor: Datapath & Control

Data hazards for branches: Example 2 37

add $1, $2, $3 IF ID EX MEM WB

add $4, $5, $6 IF ID EX MEM WB

beq stalled IF ID

beq $1, $4, target ID EX MEM WB

If a comparison register is a destination of preceding ALU instruction

or 2nd preceding load instruction

Need 1 stall cycle

COMP2611 CSE HKUST The Processor: Datapath & Control

Data Hazards for Branches: Example 3 38

lw $1, addr IF ID EX MEM WB

beq stalled IF ID

beq stalled ID

beq $1, $0, target ID EX MEM WB

If a comparison register is a destination of immediately preceding load

instruction

Need 2 stall cycles

COMP2611 CSE HKUST The Processor: Datapath & Control

Dynamic Branch Prediction 39

In deeper and superscalar pipelines, branch

penalty is more significant

Use dynamic prediction

Branch prediction buffer (aka branch history table)

Indexed by recent branch instruction addresses

Stores outcome (taken/not taken)

To execute a branch

Check table, expect the same outcome

Start fetching from fall-through or target

If wrong, flush pipeline and flip prediction

COMP2611 CSE HKUST The Processor: Datapath & Control

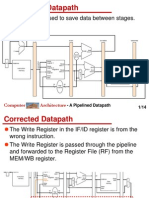

Concluding Remarks 40

Pipelining improves the throughput by allowing reuse of functional

units by different instructions

Pipelining allows an instruction to complete in each clock cycle,

but it requires a very careful design and additional registers to store

intermediate results between pipeline stages

Pipelined Control is implemented like single cycle control with needed

control signals are forwarded down the pipeline

Concurrence between instructions in the pipeline may cause

Data Hazard: data is needed by an instruction before it is produced

by a previous one

Structural Hazard: a hardware unit is needed by an instruction

while another is still using it

Control Hazard: the next instruction cannot be determined in the

next clock cycle

Hazards can always be solved by delaying (inserting bubbles)

COMP2611 CSE HKUST Introduction

Concluding Remarks (cont.) 41

Structural hazard is solved by:

Separating the instruction memory from the data memory

Writing to the register file in the first half of the clock cycle and

reading from it in the second half

Data hazard is solved by:

Forwarding/Bypassing

Inserting bubbles

Control hazards are solved by:

Hardware: add comparator to complete the comparison earlier

Speculation: guess if the branch is taken or not

Delay the branch: fill the bubbles with useful work that is

independent of the branch

COMP2611 CSE HKUST Introduction

Anda mungkin juga menyukai

- Data HazardsDokumen15 halamanData HazardsPetreMaziluBelum ada peringkat

- A Pipelined Datapath: Resisters Are Used To Save Data Between StagesDokumen14 halamanA Pipelined Datapath: Resisters Are Used To Save Data Between StagesJohnDaGRTBelum ada peringkat

- Data Hazards: Cs6303 Computer ArchitectureDokumen16 halamanData Hazards: Cs6303 Computer ArchitectureJeya Sheeba ABelum ada peringkat

- Data HazardDokumen8 halamanData HazardJeya Sheeba ABelum ada peringkat

- Pipeline HazardsDokumen39 halamanPipeline HazardsPranidhi RajvanshiBelum ada peringkat

- COE301 Lab 13 Pipelined CPU Design With Data ForwardingDokumen8 halamanCOE301 Lab 13 Pipelined CPU Design With Data ForwardingItz Sami UddinBelum ada peringkat

- Table 1: Control Signals and OpcodesDokumen6 halamanTable 1: Control Signals and Opcodesxzlosx1999Belum ada peringkat

- Enhancing Performance With PipeliningDokumen71 halamanEnhancing Performance With Pipeliningapi-26072581Belum ada peringkat

- Computer Organization Hamacher Instructor Manual Solution - Chapter 4Dokumen13 halamanComputer Organization Hamacher Instructor Manual Solution - Chapter 4suduku007Belum ada peringkat

- Data Hazards in ALU Instructions: Consider This SequenceDokumen14 halamanData Hazards in ALU Instructions: Consider This Sequencesivakumarb92Belum ada peringkat

- Microcomputer Organization and OperationDokumen18 halamanMicrocomputer Organization and OperationBillyBelum ada peringkat

- IT 209 Lecture 7 2021Dokumen47 halamanIT 209 Lecture 7 2021Jill chaudharyBelum ada peringkat

- Chapter 4B: The Processor, Part B: Mary Jane IrwinDokumen56 halamanChapter 4B: The Processor, Part B: Mary Jane IrwinAdip ChyBelum ada peringkat

- AppendixCDokumen26 halamanAppendixCmandriloquaiBelum ada peringkat

- Lecture 9 COMP2611 Processor Part1Dokumen39 halamanLecture 9 COMP2611 Processor Part1jnfzBelum ada peringkat

- Computer Science 37 Lecture 22Dokumen14 halamanComputer Science 37 Lecture 22Alexander TaylorBelum ada peringkat

- Lectures Section 3 ModifiedDokumen73 halamanLectures Section 3 ModifiedcoventryUkBelum ada peringkat

- Dms Axe Level1Dokumen28 halamanDms Axe Level1Arpit Shah100% (1)

- MULTIcycle OPERATIONSDokumen24 halamanMULTIcycle OPERATIONSi_2loveu3235Belum ada peringkat

- UNIT-5: Pipeline and Vector ProcessingDokumen63 halamanUNIT-5: Pipeline and Vector ProcessingAkash KankariaBelum ada peringkat

- Cad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationDokumen10 halamanCad For Vlsi 2 Pro Ject - Superscalar Processor ImplementationkbkkrBelum ada peringkat

- Ca Assignment: Syeda Haima Batool Naqvi CS-18022Dokumen11 halamanCa Assignment: Syeda Haima Batool Naqvi CS-18022Haima NaqviBelum ada peringkat

- CA Lab Manual 6Dokumen4 halamanCA Lab Manual 6Sourab SomasundarBelum ada peringkat

- ECE 366 Computer Architecture: Shantanu Dutt (HTTP://WWW - Ece.uic - Edu/ Dutt)Dokumen13 halamanECE 366 Computer Architecture: Shantanu Dutt (HTTP://WWW - Ece.uic - Edu/ Dutt)ahsanliaqat426Belum ada peringkat

- Controlling A Pipelined DatapathDokumen17 halamanControlling A Pipelined DatapathAlexander TaylorBelum ada peringkat

- The Pipelined RiSC-16 ComputerDokumen9 halamanThe Pipelined RiSC-16 Computerkb_lu232Belum ada peringkat

- Lecture-11 Dynamic Scheduling ADokumen18 halamanLecture-11 Dynamic Scheduling AYumna ShahzadBelum ada peringkat

- Computer Architecture: Pipelining: Dr. Ashok Kumar TurukDokumen136 halamanComputer Architecture: Pipelining: Dr. Ashok Kumar TurukkoottyBelum ada peringkat

- MIPS Pipeline Hazards and ExceptionsDokumen42 halamanMIPS Pipeline Hazards and ExceptionsNguyễn Trường GiangBelum ada peringkat

- Coa AppliedDokumen13 halamanCoa AppliedIshanBelum ada peringkat

- Assignment 3Dokumen3 halamanAssignment 3bugyourselfBelum ada peringkat

- System On Chip: Inside Processor Pipeline StallsDokumen12 halamanSystem On Chip: Inside Processor Pipeline StallsPinagani SurajBelum ada peringkat

- BER MeterDokumen8 halamanBER Metersakti prasad nandaBelum ada peringkat

- Internal Architecture of 8085 Microprocessor: A. Control UnitDokumen17 halamanInternal Architecture of 8085 Microprocessor: A. Control Unitmech mech1Belum ada peringkat

- RISC Hardware Pipeline PerformanceDokumen12 halamanRISC Hardware Pipeline PerformanceAmrendra Kumar MishraBelum ada peringkat

- Ca07 2014 PDFDokumen56 halamanCa07 2014 PDFPance CvetkovskiBelum ada peringkat

- Pipelining and Instruction Level Parallelism: 5 Steps of MIPS DatapathDokumen12 halamanPipelining and Instruction Level Parallelism: 5 Steps of MIPS DatapathNgat SkyBelum ada peringkat

- Device Information: Investigating The CAMDokumen4 halamanDevice Information: Investigating The CAMКирилл ГулякевичBelum ada peringkat

- ParaphraseDokumen51 halamanParaphrasevincent tekeyBelum ada peringkat

- Tuesday, October 31, 2023 10:53 PM: Discuss, The Schemes For Dealing With The Pipeline Stalls Caused by Branch HazardsDokumen7 halamanTuesday, October 31, 2023 10:53 PM: Discuss, The Schemes For Dealing With The Pipeline Stalls Caused by Branch Hazardskrahul74714Belum ada peringkat

- Coaa Lab Assignment: Name-Dhiraj Kurhade Roll No. - 68 GR No. - 12011151 Div - CS-B Batch - B3Dokumen20 halamanCoaa Lab Assignment: Name-Dhiraj Kurhade Roll No. - 68 GR No. - 12011151 Div - CS-B Batch - B3dhirajBelum ada peringkat

- Troubleshooting STP IssuesDokumen6 halamanTroubleshooting STP IssuesTrending DuniyaBelum ada peringkat

- Microprocessor and Micro Controller Lecture NotesDokumen118 halamanMicroprocessor and Micro Controller Lecture NotesSivanesh SK50% (2)

- Step Replace Module Flexi BSC NokiaDokumen19 halamanStep Replace Module Flexi BSC Nokiarudibenget0% (1)

- Troubleshooting L2VPN ASR900Dokumen52 halamanTroubleshooting L2VPN ASR900ws_595Belum ada peringkat

- Trouble mds9148 00Dokumen21 halamanTrouble mds9148 00Pavan NavBelum ada peringkat

- Troubleshoot and configure PPP authenticationDokumen16 halamanTroubleshoot and configure PPP authenticationMar Jara Cruz100% (1)

- Asynchronous FIFODokumen21 halamanAsynchronous FIFOMarium Mazhar50% (2)

- Microcontroller Peripheral Interfacing GuideDokumen5 halamanMicrocontroller Peripheral Interfacing Guideatmroo9Belum ada peringkat

- Cisco Security Troubleshooting: Part III - Intrusion Prevention SystemsDokumen14 halamanCisco Security Troubleshooting: Part III - Intrusion Prevention SystemshoadiBelum ada peringkat

- Pipeline HazardsDokumen94 halamanPipeline HazardsManasa RavelaBelum ada peringkat

- Explain Datapath in Pipeline or Pipelined Datapath?Dokumen4 halamanExplain Datapath in Pipeline or Pipelined Datapath?Loganathan RmBelum ada peringkat

- STM32F10xxx I2C Optimized ExamplesDokumen16 halamanSTM32F10xxx I2C Optimized ExamplescansuBelum ada peringkat

- Instruction-Level Parallelism via Pipelining and Multiple IssueDokumen21 halamanInstruction-Level Parallelism via Pipelining and Multiple IssuedanielBelum ada peringkat

- PIC18F8720/8620/6720/6620: PIC18F8720/8620/6720/6620 Rev. A4 Silicon/Data Sheet ErrataDokumen8 halamanPIC18F8720/8620/6720/6620: PIC18F8720/8620/6720/6620 Rev. A4 Silicon/Data Sheet ErrataTeboho Nelson MakeketaBelum ada peringkat

- Pipelining HazardousDokumen7 halamanPipelining HazardousAshi RanaBelum ada peringkat

- WAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksDari EverandWAN TECHNOLOGY FRAME-RELAY: An Expert's Handbook of Navigating Frame Relay NetworksBelum ada peringkat

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDari EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationBelum ada peringkat

- CISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkDari EverandCISCO PACKET TRACER LABS: Best practice of configuring or troubleshooting NetworkBelum ada peringkat

- How To Start A Research in EconomicsDokumen3 halamanHow To Start A Research in EconomicsSaswata SarkarBelum ada peringkat

- E07 Indexing IntroDokumen8 halamanE07 Indexing IntrojnfzBelum ada peringkat

- COMP 4332, RMBI 4330 Advanced Data Mining (Spring 2012) : Qiang YangDokumen9 halamanCOMP 4332, RMBI 4330 Advanced Data Mining (Spring 2012) : Qiang YangjnfzBelum ada peringkat

- The Hong Kong University of Science and Technology Calendar Dates in The 2018-19 Academic YearDokumen2 halamanThe Hong Kong University of Science and Technology Calendar Dates in The 2018-19 Academic YearjnfzBelum ada peringkat

- Session 20-SCM I - v1Dokumen27 halamanSession 20-SCM I - v1jnfzBelum ada peringkat

- Macroeconomics - Econ202A: Hall, (1978)Dokumen3 halamanMacroeconomics - Econ202A: Hall, (1978)jnfzBelum ada peringkat

- CSIT5300: SQL – Part 1 – ExercisesDokumen11 halamanCSIT5300: SQL – Part 1 – ExercisesjnfzBelum ada peringkat

- Case S02 01Dokumen5 halamanCase S02 01jnfzBelum ada peringkat

- EnsembleDokumen30 halamanEnsemblejnfzBelum ada peringkat

- L1 Financial Institutions and Markets - NewDokumen28 halamanL1 Financial Institutions and Markets - NewjnfzBelum ada peringkat

- Learn Python file processing, strings, lists and object conceptsDokumen39 halamanLearn Python file processing, strings, lists and object conceptsjnfzBelum ada peringkat

- Session 18-Revenue Management II - v2Dokumen28 halamanSession 18-Revenue Management II - v2jnfz100% (1)

- Session 9 v1Dokumen24 halamanSession 9 v1jnfzBelum ada peringkat

- L14 Communication SDokumen22 halamanL14 Communication SjnfzBelum ada peringkat

- Session 16-Inventory Demand Management v1Dokumen43 halamanSession 16-Inventory Demand Management v1jnfzBelum ada peringkat

- L15 Conflict Management SDokumen18 halamanL15 Conflict Management SjnfzBelum ada peringkat

- Measuring Forecast Accuracy and Revenue Management Techniques for McDonald'sDokumen37 halamanMeasuring Forecast Accuracy and Revenue Management Techniques for McDonald'sjnfzBelum ada peringkat

- L17 Influence S UpdatedDokumen29 halamanL17 Influence S UpdatedjnfzBelum ada peringkat

- L17 Influence S UpdatedDokumen29 halamanL17 Influence S UpdatedjnfzBelum ada peringkat

- L7 - Emotions, Attitudes, and Stress - SDokumen51 halamanL7 - Emotions, Attitudes, and Stress - SjnfzBelum ada peringkat

- L16 Leadership Power SDokumen32 halamanL16 Leadership Power Sjnfz100% (1)

- L2 - Intro To OB - SDokumen42 halamanL2 - Intro To OB - SjnfzBelum ada peringkat

- L13 TeamDynamics II S UpdatedDokumen40 halamanL13 TeamDynamics II S UpdatedjnfzBelum ada peringkat

- L4 Perception I SDokumen34 halamanL4 Perception I SjnfzBelum ada peringkat

- IEDA 3230: Engineering EconomyDokumen10 halamanIEDA 3230: Engineering EconomyjnfzBelum ada peringkat

- MGMT 2110 Mid-term ReviewDokumen15 halamanMGMT 2110 Mid-term ReviewjnfzBelum ada peringkat

- L3 Personality and Values SDokumen35 halamanL3 Personality and Values SjnfzBelum ada peringkat

- Chap1&2 PDFDokumen5 halamanChap1&2 PDFjnfzBelum ada peringkat

- 0 IntroductionDokumen43 halaman0 IntroductionjnfzBelum ada peringkat

- 02 - Moment For Morricone (For Concert Band) - Soprano (Choir)Dokumen3 halaman02 - Moment For Morricone (For Concert Band) - Soprano (Choir)Neuromante3223100% (1)

- Evaluation Test 6-Unit IDokumen2 halamanEvaluation Test 6-Unit IРотари ДианаBelum ada peringkat

- Bhatt, Mehrotra - Buddhist Epistemology PDFDokumen149 halamanBhatt, Mehrotra - Buddhist Epistemology PDFNathalie67% (3)

- Positions by Derrida, Jacques - OpenTrolley Bookstore IndonesiaDokumen2 halamanPositions by Derrida, Jacques - OpenTrolley Bookstore IndonesiaRiko Piliang0% (1)

- Eng101 Final Term Solved PaperDokumen13 halamanEng101 Final Term Solved PaperNaveed ul IslamBelum ada peringkat

- MYLASTDUCHESSDokumen6 halamanMYLASTDUCHESSHarvinPopatBelum ada peringkat

- DCP ManualDokumen96 halamanDCP ManualSiva KumarBelum ada peringkat

- 24AA512/24LC512/24FC512: 512K I C Serial EEPROMDokumen36 halaman24AA512/24LC512/24FC512: 512K I C Serial EEPROMJoseBelum ada peringkat

- 5 3-6 EALD Progression by Mode SpeakingDokumen1 halaman5 3-6 EALD Progression by Mode SpeakingS TANCREDBelum ada peringkat

- Shopping list corrections and determiner practiceDokumen2 halamanShopping list corrections and determiner practiceJonatan Muñoz VaraBelum ada peringkat

- Cucumber BDDDokumen46 halamanCucumber BDDRahul JaiswalBelum ada peringkat

- How To Get A High Score in IELTS WritingDokumen16 halamanHow To Get A High Score in IELTS Writingpuji4nggr4eniBelum ada peringkat

- Sa Aking Mga KabataDokumen2 halamanSa Aking Mga KabataCassandra ColigadoBelum ada peringkat

- The Ugly TruthDokumen94 halamanThe Ugly Truthgeetkumar1843% (7)

- The Word Essay Derives From The French Infinitive Essayer, 'To Try' or 'To Attempt'. Generally, ADokumen3 halamanThe Word Essay Derives From The French Infinitive Essayer, 'To Try' or 'To Attempt'. Generally, ASo FarBelum ada peringkat

- Worksheet 10 Conversational Maxims EtcDokumen5 halamanWorksheet 10 Conversational Maxims EtcDiana RBelum ada peringkat

- Saoc67 PDFDokumen496 halamanSaoc67 PDFantonio regueraBelum ada peringkat

- Manuel S. Enverga University Foundation Lucena City Granted Autonomous Status CHED CEB Res. 076-2009 College of Arts and SciencesDokumen3 halamanManuel S. Enverga University Foundation Lucena City Granted Autonomous Status CHED CEB Res. 076-2009 College of Arts and SciencesLaika MerleBelum ada peringkat

- Mcqs With Answers-Class 12-MathDokumen19 halamanMcqs With Answers-Class 12-MathziyaBelum ada peringkat

- Self Review CommentaryDokumen3 halamanSelf Review CommentaryAdlinBelum ada peringkat

- Sharah Aqeeda-E-Tahawiyyah - Shaykh Muhammad Bin Yahya NinowyDokumen205 halamanSharah Aqeeda-E-Tahawiyyah - Shaykh Muhammad Bin Yahya NinowyAtif Hussain Khan100% (2)

- Basic Japanese Textbooks and Preparation 2020Dokumen3 halamanBasic Japanese Textbooks and Preparation 2020Omar AshrafBelum ada peringkat

- The Critical Thread: The Symmetric Group in Galois Theory, Representation Theory, Representations of Lie Algebras, Combinatorics, and TopologyDokumen200 halamanThe Critical Thread: The Symmetric Group in Galois Theory, Representation Theory, Representations of Lie Algebras, Combinatorics, and Topologymathematics2x2lifeBelum ada peringkat

- Humility in Prayer 2Dokumen80 halamanHumility in Prayer 2Malik Saan BayramBelum ada peringkat

- IMS 7.4 Custom Postprocessor InstallationDokumen2 halamanIMS 7.4 Custom Postprocessor InstallationZixi FongBelum ada peringkat

- Lessonplan Writing MenusDokumen2 halamanLessonplan Writing Menusapi-134423826Belum ada peringkat

- Verbs in Present Simple and ContinuousDokumen1 halamanVerbs in Present Simple and ContinuousDerry RiccardoBelum ada peringkat

- Session No. 5: Growing in The SpiritDokumen6 halamanSession No. 5: Growing in The SpiritRaymond De OcampoBelum ada peringkat

- Vsphere Esxi Vcenter Server 60 Host Profiles GuideDokumen20 halamanVsphere Esxi Vcenter Server 60 Host Profiles Guideพูลพิพัฒน์ สุขเกษมBelum ada peringkat

- Islamic StudiesDokumen7 halamanIslamic StudiesShafeeq HakeemBelum ada peringkat