ID Perancangan Dan Simulasi Ic Cmos Inverte

Diunggah oleh

Hide AnakbangsaJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

ID Perancangan Dan Simulasi Ic Cmos Inverte

Diunggah oleh

Hide AnakbangsaHak Cipta:

Format Tersedia

107

Perancangan dan Simulasi IC CMOS Inverter

Schmitt Trigger

Ari Permana L, D. J. Djoko H. S, Wijono, dan M. Julius

antarmuka yang terbatas, impedansi input rendah dan

Abstrak–- Penelitian ini untuk mendesain dan karakteristik output tidak seimbang. Schmitt Trigger

menganalisis rancangan IC CMOS Inverter Schmitt bisa dibangun dari perangkat diskrit untuk memenuhi

Trigger sehingga dihasilkan efisiensi kerja sistem berupa parameter tertentu, Schmitt Trigger CMOS

disipasi daya rendah dan propagation delay yang kecil mengoptimalkan desain karakteristik yang meliputi:

sehingga kecepatan sistem meningkat. Teknologi yang interfacing dengan op amp dan jalur transmisi, konversi

digunakan dalam perancangan ini adalah teknologi 0.12 tingkat logika, linear operation, dan desain khusus

µm dengan tegangan supply V DD 1.2 V dan tegangan input

bergantung pada karakteristik CMOS. Schmitt Trigger

yang diberikan sebesar 1.2 V. Berdasarkan analisis

perhitungan tegangan histerisis yang simetris tergantung CMOS memiliki keuntungan sebagai berikut: Impedansi

pada rasio perbandingan transkonduktansi NMOS β 1 masukan yang tinggi (1012 Ω), keseimbang

(W/L =0.12 µm / 0.12 µm)dan β 3 (W/L =0.22 µm / 0.12 µm) karakteristirk input dan output meliputi (Ambang batas

untuk rasio perbandingan transkonduktansi PMOS β 5 simetris, biasanya untuk ½ VCC, Pengendali jalan

(W/L =0.30 µm / 0.12) dan β 6 (W/L =0.55 µm / 0.12 µm). keluaran). Ambang positif dan negatif menunjukkan

Desain Schmitt Trigger berdasarkan hasil analisis variasi yang rendah sehubungan dengan suhu, batas

perhitungan dan hasil analisis simulasi bahwa dengan tegangan (2V - 6V), Komsumsi daya rendah, Kebal

teknologi 0.12 µm, propagation delay yang dihasilkan terhadap noise.

dengan beban kapasitor ≤ 5 pF, K’ N = 713 μA/V2 dan K’ P =

288 uA/V2 sebesar 12,5 ns dimana ini adalah nilai

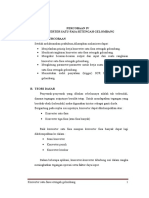

propagasi delay yang memungkinkan digunakan untuk II. LANDASAN TEORI

perancangan IC schmitt tigger inverter dengan teknologi A. Schmitt Trigger

0,12 µm. Berdasarkan hasil analisis perhitungan, semakin

besar beban kapasitor dan frekuensi yang digunakan

maka semakin besar pula power disipation (P D ) dan power

disipation product (PDP) dimana pada analisis perhitungan

dengan beban 5 pF bekerja pada frekuansi 15 mHz

diperoleh disipasi daya 108 µW dan Power delay Product

1.35

Kata Kunci : Schmitt Trigger, Hysterisis, Propagation

Delay, Power Disipation

I. PENDAHULUAN

D ESAIN Integrated circuit (IC) dapat dibagi ke

dalam dua kategori, yaitu: digital dan analog.

Desain IC digital digunakan dalam komponen seperti

Gb. 1. Karakteristik Schmitt Trigger

Mikroprosesor, Field-Programmable Gate Array

(FPGA), Random-Acces Memory (RAM), Read Only

Memory (ROM), Flash dan Application-Specific

Integrated Circuit (ASICs). Desain digital berfokus

pada kebenaran logis, memaksimalkan kepadatan dan

menempatan sirkuit sehingga clock dan sinyal waktu

yang diarahkan efisien. Desain IC Analog juga memiliki

spesialisasi dalam desain Operational Amplifier (Op-

Amp), regulator linier, osilator dan filter aktif.

Fleksibilitas dari Schmitt Trigger Transistor

Transistor Logic (TTL) terhambat oleh kemampuan

Ari Permana L adalah dosen Politeknik Negeri Ambon yang Gb. 2 Skema Schmitt Trigger

sedang tugas belajar di Program Magister Teknik Elektro, Program

Magister dan Doktor Fakultas Teknik Universitas Brawijaya (e-mail:

aripermana002@@yahoo.co.id). Schmitt Trigger sangat berguna dalam menghasilkan

D. J. Djoko H. S, Wijono, dan M Julius merupakan staf pengajar pulsa bersih dari noise sinyal masukan atau dalam

Jurusan Teknik Elektro Fakultas Teknik Universitas Brawijaya

Malang (e-mail: dsantjojo@ub.ac.id; wijono@ub.ac.id; desain sirkuit osilator. Selanjutnya. Simbol skematis

m.julius.st@ub.ac.id ).

Jurnal EECCIS Vol.6, No.2, Desember 2012

108

𝛽𝑛3

dari schmitt trigger ditunjukkan dalam Gb. 1, bersama = [𝑉𝐷𝐷 − (𝑉 + − 𝑉𝑇𝑁 ) − 𝑉𝑇𝑁 ]2

2

dengan kurva pengalihan (transfer curves). 𝛽𝑛3

Skema dasar dari Schmitt trigger ditunjukkan dalam = (𝑉𝐷𝐷 − 𝑉 + )2 (4)

2

Gb. 2, dapat dibagi rangkaian menjadi dua bagian, Sehingga tegangan swicthing maju V+ sebagai

tergantung pada apakah output tinggi atau rendah. Jika berikut:

output rendah, maka M 6 dalam keadaan on dan M 3 β N1

(V DD + VTN ) x

dalam keadaan off, maka pada bagian kanal-p +

β N3

V =

menunjukkan titik tegangan switching, sedangkan jika β N1

1+

output tinggi, M 3 dalam keadaan on dan M 6 dalam β 3N

(5)

keadaa off maka pada bagian kanal-n menunjukkan titik Tegangan swicthing balik V- karena aksi kerja dari

tegangan switching. Dimana M 4 dan M 5 juga berada M 4 , M 5 dan M 6 , khususnya M 6 yang merupakan

dalam keadaan on yang langsung terhubung ke V DD . perangkat umpan balik dalam persilangan M 4 . Analisis

Untuk menganalisis rangkaian, kita asumsikan bahwa rangkaian menjadi

output dalam keadaan tinggi (V DD ) dan input dalam

β P5

keadaan rendah (0 V), Gb. 1 menunjukkan bagian (VDD − VTP ) x

β P6

bawah dari schmitt trigger yang digunakan dalam V− =

β P5

menghitung titik atas tegangan switching V SPH , 1+

β P6

MOSFET M 1 dan M 2 dalam keadaa off, dengan V in = 0 (6)

V M 3 dalam keadaan on. pada. Sumber dari M 3 dalam Tegangan swicthing balik diatur dengan

keadaan mengambang (floating) dimana V DD – V THN perbandingan (βp 5 / βp 6 ). Schmitt trigger simetris dapat

atau sekitar 4V untuk V DD = 5V. Potensial V x , dinyatakan dengan Persamaan (5) dan (6).

ditunjukkan dalam Gb. 3. 1

𝑉 + = � � 𝑉𝐷𝐷 + ∆𝑉 (7)

2

1

𝑉 − = � � 𝑉𝐷𝐷 − ∆𝑉 (8)

2

+ -

yang menempatkan tegangan V dan V berjarak

sama dan setengah tegangan V DD , sesuai dengan

tegangan histerisis

Gb. 3. Bagian dari skema pemicu Schmitt digunakan untuk

menghitung titik atas tegangan switching. V H =2.ΔV (9)

Dengan V in kurang dari tegangan ambang M 1 , V x B. Propagation Delay

tetap di V DD - V THN3 sedangakan V in naik, tegangan M 1 Kecepatan operasi gerbang digital diukur melalui tiga

mulai on, tegangan V x, mulai jatuh ke tanah (ground). parameter yaitu rise time (waktu naik), fall time (waktu

titik tegangan switching yang tinggi didefinisikan dalam turun) dan propagation delay. Parameter ini

Persamaan 1. mempengaruhi keseluruhan waktu delay yang

V in = V SPH = V THN2 + V x (1) dihasilkan ketika gerbang melakukan transisi dari

atau ketika M 2 mulai aktif (on), maka output mulai keadaan satu ke lainnya. Delay terjadi karena terdapat

bergerak ke ground, menyebabkan M 3 mulai off ini efek kapasitansi yang terdapat pada gerbang masukan

pada gilirannya menyebabkan V x jatuh lebih jauh, M 2 dan keluaran. Selain itu, efek kapasitansi juga timbul

mulai on, ini terus berlanjut sampai M 3 adalah benar- pada jalur koneksi antar gerbang. Propagation delay

benar dalam keadaan off dan dimana keadaan M 2 dan ditunjukkan pada Gb. 4.

M 1 dalam kondisi on. umpan balik positif menyebabkan

titik tegangan switching menjadi sangat baik.

Persamaan (2.20) berlaku arus yang mengalir di M 1 dan

M 3 pada dasarnya sama. Penyamaan arus ini

memberikan Persamaan 2.

𝛽1 𝛽

= (𝑉𝑆𝑃𝐻 − 𝑉𝑇𝐻𝑁 )2 = 3 = (𝑉𝐷𝐷 − 𝑉𝑋 − 𝑉𝑇𝐻𝑁3 )2 (2)

2 2

dimana sumber sama dengan M 2 dan M 3 , maka V THN2

= V THN3 terjadi peningkatan tegangan ambang dari efek

body untuk setiap MOSFET. Kombinasi Persamaan

(1) dan Persamaan (2) menghasilkan Persamaan (3).

Gb. 4. Definisi Delay dalam Gerbang Digital

𝛽1 𝑊1 .𝐿3 𝑉𝐷𝐷−𝑉𝑆𝑃𝐻 3

= =� � (3) in v er t er CM O S ya n g s i me tr is d e n ga n b eb a n

𝛽3 𝐿1 .𝑊1 𝑉𝑆𝑃𝐻 −𝑉𝑇𝐻𝑁

Pernyataan bentuk lebih dekat untuk V+ diperoleh kap as it i f bertujuan untuk mengetahui waktu tunda

dengan mengabaikan efek body bias dan menganggap (propagation delay), dengan asumsi transisi tegangan

semua tegangan threshold sama V T1 = V T2 = V T3 = V TN . pada masukan. Pertama, waktu propagasi delay high to

Dengan menganggap M 1 jenuh menghasilkan low t PHL , transisi tegangan input dari 0V naik ke

Persamaan arus (4). tegangan V DD dimana t = 0, transistor NMOS dalam

𝛽𝑛1 𝛽𝑛3 keadaan jenuh (saturated) t = 0+ sampai tegangan

= (𝑉 + − 𝑉𝑇𝑁 )2 = (𝑉𝐷𝐷 − 𝑉𝑥 − 𝑉𝑇𝑁 )2

2 2 output V out turun sampai V DD – V T. Selama interval

Jurnal EECCIS Vol.6, No.2, Desember 2012

109

waktu ini, arus konstan mengalir dalam transistor ditunjukkan dalam Gb. 5.

NMOS adalah:

DD K(V T −V )2

IDN = (10)

2

Transistor NMOS menjadi linear pada saat V out = V DD –

V T , dimana t = t D1

2VT CL

t D1 = 2 (11)

K(VDD −VT )

Sampai tegangan V out turun di bawah tegangan V DD –

V T , transistor NMOS bergerak ke daerah operasi linear,

pendekatan pertama untuk transistor NMOS linear

adalah

V

IDN = out (12)

RDN Gb. 5. Pengaruh Nilai kR pada Grafik Vin terhadap Vout

dimana

1

= nilai rata − rata dari �

∂IDN

� (13) Wn Wn

RDN ∂Vout µ n C ox µ n C ox

Untuk NMOS linear, arus drain yang mengalir

kR = Ln

⇒1= Ln

memberikan persamaan Wp Wp (25)

IDN = K �(VDD − VT ). Vout − � (14)

Vout 2 µ p C ox µ p C ox

2 L p L p

Turunan parsial dari arus drain yang mengalir

sehubungan dengan tegangan output

Wn

ϑIDN

= K[(VDD − VT ) − Vout ] (15) K 'n = μ n .C ox .

ϑVout Ln

Nilai rata-rata dari turunan parsial dapat diperkirakan (26)

dengan menggantikannya dalam nilai rata-rata tegangan ε ox

keluaran V out , menghasilkan C ox =

1 K(VDD −VT ) t ox

= (16) (27)

RDN 2

dengan menggunakan pendekatan ohmik untuk NMOS C. Disipasi Daya

linear, rangkaian dapat diperlakukan sebagai kombinasi Disipasi daya (power dissipation) merupakan daya

RC sederhana. dengan demikian, yang dikonsumsi oleh suatu gerbang. Disipasi daya

(t−tD1

Vout ≈ (VDD − VT )exp �− � (17) dalam sistem CMOS dapat diklasifikasikan ke dalam

RDN .CL

Tegangan output mencapai 50% pada t = t D1 + t D2 , tiga kategori, yaitu: disipasi daya statis, daya

dimana pensaklaran (switching) DC yang terjadi pada saat

V −V kedua transistor menghantarkan secara bersamaan

t D2 = R DN CL ln � DD T � (19)

VDD /2 dalam waktu yang sangat singkat dan daya pensaklaran

Propagasi Delay dari tinggi ke rendah adalah jumlah AC yang terjadi ketika kapasitansi total pada gerbang

dari t D1 dan t D2 : menyimpan dan melepaskan muatan.

t PHL = t D1 + t D2 ≈

P = C LVDD f

2

C 2.V 2 V −V

≈ L �(V T )2 + (V )

. Ln � DD ⁄ T �� (20) (28)

K DD −VT DD −VT VDD 2

Suatu gerbang logika yang ideal haruslah cepat dan

Hal yang sama dilakukan untuk analisis t PHL , untuk

membutuhkan daya minimum. Salah satu parameter

inverter CMOS yang simetris, waktu tunda

yang dipergunakan untuk menunjukkan ukuran

(propagation delay) adalah sama, oleh karena itu,

kecepatan dan daya minimum sebuah gerbang adalah

t PHL = t PLH = t PD (21)

Power Delay Product (PDP). Semakin kecil nilai P DP ,

dimana

PDP didefinisikan sebagai hasil kali antara propagation

CL 2.VT 2 VDD −VT delay dengan disipasi daya rata-rata seperti

t PD ≈ �(V 2 + (V . Ln � �� (22)

K DD −VT ) DD −VT ) VDD ⁄2 ditunjukkan dalam Persamaan (29).

Rise time (t r) didefinisikan sebagai waktu yang PDP = t dly . .P (29)

diperlukan untuk berubah dari 10% V DD ke 90% V DD

untuk gerbang dengan tegangan “LOW” 0V dan III. KERANGKA KONSEP PENELITIAN

tegangan “HIGH” V DD nilai t r ditunjukkan dalam Penelitian dimulai dengan mendesain rangkaian

Persamaan (23). Fall time (t f ) didefinisikan sebagai digital schmitt trigger dan menentukan parameter W/L.

waktu yang dibutuhkan untuk berubah dari 90% V DD ke Penentuan W/L bertujuan untuk meminimalkan

10% V DD , nilai t f ditunjukkan dalam Persamaan (24). tegangan histerisis, Semakin kecil tegangan histerisis

t r , (t TLH ) = 2 × t PLH (23) berarti semakin cepat waktu propogation delay. Desain

rule menggunakan teknologi CMOS 0.12µm, parameter

t f , (tTHL ) = 2 × t PHL (24) proses dari Microwind dan DSCH. Tahap selanjutnya

melakukan simulasi dengan menggunakan program

Suatu gerbang dikatakann memiliki grafik

Pspice untuk menentukan grafik VTC dan Unit Step

karakteristik alih tegangan yang simetris apabila nilai

sebagai dasar untuk menentukan output berupa t PHL ,

K R = 1. Pada saat ini berlaku hubungan yang

t PLH , t PD dan disipasi daya P D . Pengujian dilakukan

Jurnal EECCIS Vol.6, No.2, Desember 2012

110

secara bertahap hingga menghasilkan grafik yang sesuai (V+). Jika tegangan input diawali pada tegangan V DD ke

dengan keinginan yaitu kecepatan yang tinggi dan daya 0V maka transisi switching tegangan alih balik (V-).

rendah. Jika penelitian belum sesuai maka dilakukan Tegangan histerisis memberikan pemisahan antara 2

pengujian ulang pada nilai W/L. Setelah output yang (dua) titik switching. dimana tegangan histerisis (V+)

dihasilkan sesuai maka dibuat layout dengan program dapat diketahui dengan menggunakan Persamaan 5 dan

Microwind. Gb. 6. Menunjukan diagram alir kerangka 6.

penelitian. 0.12

(1.2 + 0.35) x

+ 0.22 1.2 + 0.35 x0.738

Schmitt Trigger V = = = 0.84V

0.12 1.738

1+

0.22

0.30

x(1.2 − 0,35)

− 0.55 0.738 x1.2 − 0.35

Digital Mixed Signal Analog V = = = 0.36V

0.30 1.738

1+

0.55

Desain Rangkaian Schmitt Trigger

(Spesifikasi Input & Output)

TABEL I

Analisis Data Perhitungan PARAMETER DASAR TRANSISTOR

Analisis Skematik

Simbol NMOS PMOS Keterangan

Simulasi Rangkaian VDD 1.2V Tegangan Catu Daya

(Cadence, DSCH, Microwind)

620

Uo 250 cm2/V.s Carrier Mobility

cm2/V.s

Parameter

Pengujian KP 713 μA/V2 288 μA/V2

Tidak Transkonduktansi

(Histerisis, tPHL, tPLH, tPD,) Tegangan ambang

Ya VT 0.35 V -0.35 V

NMOS dan PMOS

Layout PHI, Surface potential

Keseluruhan Sistem 2фF 0.3 V

atsrong invertion

Gb. 6. Diagram Alir Kerangka Penelitian GAMMA, Bulk

γ 0.4 √V

thershold parameter

Ketebalan oksidasi

IV. HASIL DAN DISKUSI tox 3 nm

gerbang

Konstanta dielektrik

Tahap awal dalam perancangan IC CMOS schmitt εOX 3.45 x 10-13 F/cm

polisilikon

trigger meliputi penentuan spesifikasi rangkaian IC

yang akan dirancang, perancangan rangkaian logika

Schmitt Trigger Langkah selanjutnya merancang ukuran

komponen W/L berdasarkan parameter proses transistor TABEL II

DESAIN W/L TRANSISTOR SCHMITT TRIGGER

NMOS dan PMOS yang akan digunakan dalam

Teknologi CMOS (0.12 μm)

perhitungan. Dari hasil perbandingan nilai W/L yang

Transistor NMOS PMOS

digunakan, selanjutnya menentukan nilai VTC,

W L W L

propagation delay dan penggambaran layout pada

M1 0.12 0.12 - -

microwind

M2 0.60 0.12 - -

Spesifikasi Teknis rangkaian schmitt trigger M3 0.22 0.12 - -

ditentukan sebagai berikut: M4 - - 1.5 0.12

1. High Speed Operation : t pd = 13 ns. M5 - - 0.30 0.12

2. Wide Supply Voltage : V DD = 2V to 6 V M6 - - 0.55 0.12

3. Power Disipation : Dual-In-Line = 700 mw, Small

Outline = 500 mw

4. Hysterisis : V T + = 0.9V dan V DD = 4.5V Data hasil analisis perhitungan ditunjukkan dalam

Dalam rancangan ini mengacu pada parameter proses. (Tabel III).

Penggunaan parameter tipikal ini untuk lebih mendekati

TABEL III

pada karakteristik devais dan mempermudah dalam ANALISIS PERHITUNGAN PROPAGASI DELAY

proses analisis

CL tPHL tPLH tPD tf

Penentuan W dan L didasari oleh analisis yang tr (ns)

(pF) (ns) (ns) (ns) (ns)

dilakukan pada nilai K R = 1. Nilai µ p dan µ n dapat 0.5 1.25 1.25 1.25 2.5 2.5

mempengaruhi nilai W dan L yang dihasilkan, VTC 1 2.5 2.5 2.5 5 5

yang simetris akan didapat dengan memasukkan nilai µ p 5 12.5 12.5 12.5 25 25

= 250 cm2/V.s dan µ n = 620 cm2/V.s 10 25 25 25 50 50

Schmitt trigger merupakan rangkaian yang memiliki

karakteristik alih tegangan VTC histerisis, dimana Hasil perhitungan untuk frekuensi 5 MHz, 10 MHz,

karakteristik alih tegangan maju (V+) dan karakteristik dan 15 MHz, serta dengan kombinasi beban kapasitor,

alih tegangan balik (V-). Bila tegangan input dinaikan hasil analisis perhitungan disipasi daya ditunjukkan

dari 0V ke V DD , transisi swicthing tegangan alih maju dalam (Tabel IV).

Jurnal EECCIS Vol.6, No.2, Desember 2012

111

TABEL IV Simulasi schmitt trigger untuk beban kapasitor C L = 1 pF

ANALISIS PERHITUNGAN DISIPASI DAYA

Frekuensi

CL 1 MHz 5 MHz 10 MHz 15 MHz

(pF) PD PDP PD PDP PD PDP PD PDP

(µW) (fJ) (µW) (fJ) (µW) (fJ) (µW) (fJ)

0.5 0.72 0.9 3.6 4.5 7.2 9 10.8 13.5

1 1.44 3,6 7.2 18.1 14.4 36 21.6 54.2

5 7.2 90 36 0.45 72 0.9 108 1.35

10 14.4 0.36 72 1.8 144 3.6 216 5.42

Hasil simulasi histerisis maju (V+) schmitt trigger Gb. 9. Grafik propagation delay schmitt trigger pada CL = 1 pF

inverter terjadi saat tegangan input berada pada 0.83V t PHL = (13.333 – 10.050) ns = 3.3 ns

dan tegangan output 0.83V. hal ini menunjukkan bahwa t PLH = (31.848 – 30.150) ns = 1.7 ns

tegangan histerisis maju simetris, dimana pada analisis (3.3 + 1.7) ns (5) ns

t PD = = = 2.5 ns

2 2

perhitungan sebesar 0.84V dan hasil simulasi tegangan

tr = (34.425 - 30.455) ns = 3.9 ns

histerisis balik terjadi saat tegangan input berada pada tf = (17.184 – 10.805) ns = 6.4 ns

0.36V dan tegangan output 0.36V. hal ini menunjukkan

bahwa tegangan histerisis balik simetris, pada analisis Simulasi schmitt trigger untuk beban kapasitor C L = 5 pF

perhitungan sebesar 0.36V. Gb. 7. menunjukkan grafik

histerisis schmitt trigger.

Gb. 8. Grafik propagation delay Schmitt trigger pada CL = 0.5 pF

Gb. 7. Grafik histerisis Schmitt Trigger

(Tabel V) menunjukak perbandingan histerisis hasil

perhitungan dan hasil simulasi.

TABEL V

PERBANDINGAN HISTERISIS HASIL PERHITUNGAN DAN SIMULASI

Histerisis Balik (V-) Histerisis Maju (V+)

Kriteria Gb. 10. Grafik propagation delay schmitt trigger pada CL = 5 pF

Input Output Input Output

Perhitungan 0.36 V 0.36 V 0.84 V 0.84 V t PHL = (116.212 – 100.050) ns = 16.162 ns

Simulasi 0.36 V 0.36 V 0.83 V 0.83 V t PLH = (308.675 – 300.050) ns = 8.625 ns

(16.162 + 8.625) ns (24.787) ns

t PD = = = 12.39 ns

2 2

Simulasi unit step dilakukan untuk mendapatkan nilai tr = (321.839 - 301.947) ns = 19.89 ns

propagation delay. Masukan yang diberikan berupa tf = (135.632 - 103.704) ns = 31.93 ns

gelombang pulsa (step). Nilai propagation delay

diperoleh dari sinyal output yang berupa nilai t PLH , t PHL , Simulasi schmitt trigger untuk beban kapasitor C L = 10 pF

rise time (t r ) dan fall time (t f ). Dalam simulasi unit step

diberikan variasi kapasitor pada keluaran untuk

mengatahui respon waktu rangkaian IC schmitt trigger

yaitu 0.5pF, 1pF, 5pF, 10pF Selain itu digunakan variasi

frekuensi yang berbeda yaitu 1MHz, 5MHz, 10MHz

dan 15MHz pada suhu normal 27o C.

Simulasi schmitt trigger untuk beban kapasitor C L = 0.5 pF

Gb. 11. Grafik propagation delay schmitt trigger pada CL = 10 pF

t PHL = (11.726 – 10.050) ns = 1.68 ns t PHL = (132.023 – 100.050) ns = 31.97 ns

t PLH = (21.073 – 20.150) ns = 0.92 ns t PLH = (317.228 – 300.050) ns = 17.18 ns

(1.68 + 0.92) ns (2.60) ns

t PD = = = 1.3 ns t PD =

(31.97 + 17.18) ns

=

(49.15) ns

= 24.57 ns

2 2

2 2

tr = (22.397 – 20.369) ns = 2.03 ns tr = (343.820 - 303.933) ns = 39.89 ns

tf = (13.664 – 10.445) ns = 3.22 ns tf = (170.225 - 107.303) ns = 62.92 ns

Jurnal EECCIS Vol.6, No.2, Desember 2012

112

(Tabel VI) menunjukan perbandingan propagation Penggambaran layout dilakukan dengan

delay hasil perhitungan dan hasil simulasi. menggunakan default process Microwind (0.12 µm

Analisis propoagation delay yang dilakukan dalam CMOS Process) dengan λ = 0.12 µm/2 = 0.06 µm.

perancangan schmitt trigger baik analisis perhitungan Layout IC Schmitt Trigger Inverter CMOS ditunjukkan

maupun analisis simulasi terdapat perbedaan pada dalam Gb. 12.

waktu transisi high to low (t PHL ) dan waktu transisi dari

low to high (t PLH ), Hasil analisis perhitungan maupun V. KESIMPULAN

hasil simulasi untuk teknologi 0.12 µm, beban yang Kesimpulan yang dapat diambil dari penelitian ini

dianjurkan ≤ 5 pF, pada beban 5 pF propagation delay sebagai berikut

yang diperoleh 12.5 ns lebih kecil dibanding dengan 1. Berdasarakan hasil analisis perhitungan dan

spesifikasi rangkaian 13 ns. simulasi dalam penentuan tegangan histerisis,

TABEL V maka harus diperhatikan rasio perbandingan

PERBANDINGAN HISTERISIS HASIL PERHITUNGAN DAN SIMULASI transkonduktansi W/L transistor M 3 dan M 6 , dari

CL

Propagasi Delay rasio perbandingan transkonduktansi maka akan

Kriteria tPHL tPLH tPD tr tf menghasilkan tegangan histerisis yang bervariasi.

(pF)

(ns) (ns) (ns) (ns) (ns)

2. Untuk mendapatkan hasil schmitt trigger inverter

Perhitungan 1.25 1.25 1.25 2.5 2.5

0.5 yang simetris, dua penundaan propagasi t PHL, t PLH

Simulasi 1.68 0.92 1.3 2.03 3.22

Perhitungan 2.5 2.5 2.5 5 5 dan t PD adalah sama. Hasil ini menunjukkan

1

Simulasi 3.3 1.7 2.5 3.9 6.4 bahwa penundaan propagasi sebanding dengan

Perhitungan 12.5 12.5 12.5 25 25

5

Simulasi 16.16 8.63 12.39 19.89 31.93

kapasitansi beban dan berbanding terbalik dengan

Perhitungan 25 25 25 50 50 parameter transkonduktansi. Kecepatan yang lebih

10 tinggi dapat diperoleh dengan mengurangi

Simulasi 31.97 17.18 24.57 39.89 62.92

kapasitansi beban atau dengan meningkatkan nilai-

nilai K. Selain itu, ada ketergantungan pada

tegangan catu daya.

3. Berdasarkan hasil analisis perhitungan, semakin

besar beban kapasitor dan frekuensi yang

digunakan maka semakin besar pula power

disipation (P D ) dan power disipation product

(PDP).

DAFTAR PUSTAKA

[1] Ayers, J. E. 2004. Digital Integreted Circuit Analysis and

Design. CRC Press, New York Washington DC.

[2] Baker, R. 2010. CMOS Circuit design Layout and Simulations.

Third Edition. Jhon Wiley and Sons, INC. Canada.

Gb. 12. Tata letak IC CMOS Schmitt Trigger Inverter [3] [3] Jaeger, R. 1997. Microelectronic Circuit Design. Auburn

University. The McGraw-Hill Companies, Inc.USA.

[4] [4] Geiger, R. L., Allen, P. E and Strader, N. R. 1990. VLSI

Design Techniques For Analog and Digital Circuits. The

McGraw-Hill Companies, Inc.USA.

[5] [5] Kang, S. M and Leblebici, Y. 2003. Analysis and Design

CMOS Digital Integreted Circuit. The McGraw-Hill Companies,

Inc.USA.

Ari permana L, lahir di Jakarta, 23 Februari 1979 sebagai anak ke

pertama dari tiga bersaudara, pasangan Sulaiaman Launuru dan Sri

Retno Pujiwati. Tahun 1985 bersekolah di SDN 2 Sidangoli dan lulus

tahun 1991. SMPN 4 Ternate lulus tahun 1994. SMK 2 Ternate lulus

tahun 1997. Sarjana Teknik Elektro Univerrsitas Muslim Indonesia

lulus tahun 2002. Tahun 2006 sampai sekarang, bekerja sebagai dosen

di Politeknik Negeri Ambon Provinsi Maluku.

Gb. 13. Layout Rangkaian Schmitt Trigger inverter

teknologi 0.12 µm

Jurnal EECCIS Vol.6, No.2, Desember 2012

Anda mungkin juga menyukai

- Ira Palupi 022000021 Laporan Penguat Kelas BDokumen25 halamanIra Palupi 022000021 Laporan Penguat Kelas BIra PalupiBelum ada peringkat

- Job 5Dokumen21 halamanJob 5uli ajni khatiBelum ada peringkat

- Rangkaian ClamperDokumen15 halamanRangkaian ClamperHutami Gumilang Satriyani100% (1)

- FM ModulatorsDokumen11 halamanFM ModulatorsSanty Sweetta TampubolonBelum ada peringkat

- Konverter Satu-Fasa Setengah Gelombang (Pers-Ass5)Dokumen41 halamanKonverter Satu-Fasa Setengah Gelombang (Pers-Ass5)AdelBelum ada peringkat

- DIFFERENSIATORDokumen12 halamanDIFFERENSIATORMuhamad Akmal DzakwanBelum ada peringkat

- Rangkaian Elektrik 2 - Parameter Jaringan Dua PortDokumen29 halamanRangkaian Elektrik 2 - Parameter Jaringan Dua PortFerdinandus SipangkarBelum ada peringkat

- Job 6Dokumen22 halamanJob 6uli ajni khatiBelum ada peringkat

- Cycloconverter Tiga Fase ke Frekuensi RendahDokumen9 halamanCycloconverter Tiga Fase ke Frekuensi RendahHeri setiawanBelum ada peringkat

- Modul 4 - Peny Terkendali 1 Fasa Gel Penuh Simetris - OkDokumen6 halamanModul 4 - Peny Terkendali 1 Fasa Gel Penuh Simetris - OkIlhammnBelum ada peringkat

- FM MODULATORS PrihtDokumen13 halamanFM MODULATORS PrihtFaisal Nanda UtamaBelum ada peringkat

- Modul 3 - Peny Terkendali 1 Fasa Gel Penuh Asimetris - OkDokumen6 halamanModul 3 - Peny Terkendali 1 Fasa Gel Penuh Asimetris - OkIlhammnBelum ada peringkat

- Transformer ArusDokumen6 halamanTransformer Aruszulchargeman100% (4)

- Bab 3 Penyearah Terkontrol (Pertemuan Ke Empat)Dokumen9 halamanBab 3 Penyearah Terkontrol (Pertemuan Ke Empat)JordiBelum ada peringkat

- Perc - 3 Rangkaian Penguat Common SourceDokumen6 halamanPerc - 3 Rangkaian Penguat Common SourceBimo DwyeyasBelum ada peringkat

- Bab 10Dokumen54 halamanBab 10Zev B'Yond D GraveBelum ada peringkat

- Ne 555Dokumen8 halamanNe 555Yahya NurrohmanBelum ada peringkat

- PT2123 05 Osilator PDFDokumen38 halamanPT2123 05 Osilator PDFRizki PrasetyoBelum ada peringkat

- Laporan Elektronika Digital 1Dokumen6 halamanLaporan Elektronika Digital 1alfren dwijayaBelum ada peringkat

- Kelompok 2Dokumen20 halamanKelompok 2Yusi YosepBelum ada peringkat

- TRANSISTOR LOGICDokumen7 halamanTRANSISTOR LOGICReza MutaqinBelum ada peringkat

- F-9 01 Aulia Raden Puteh 118130106 Alif Fauzan.Dokumen12 halamanF-9 01 Aulia Raden Puteh 118130106 Alif Fauzan.ya yaBelum ada peringkat

- III. Bahan Ajar MK Analisis Transien s1 Sem Vii-2 Sks (Bab I)Dokumen21 halamanIII. Bahan Ajar MK Analisis Transien s1 Sem Vii-2 Sks (Bab I)Ittox MautinhoBelum ada peringkat

- Cara Kerja Rangkaian Touch Switch Menggunakan IC NE555 dan 7474Dokumen17 halamanCara Kerja Rangkaian Touch Switch Menggunakan IC NE555 dan 7474Rafi SuryatamaBelum ada peringkat

- Gerbang LogikaDokumen15 halamanGerbang LogikaI2O13OO96 Ryan SyehanBelum ada peringkat

- LVDT GETARANDokumen4 halamanLVDT GETARANMuhammad Afdhal0% (1)

- Laporan Karaktersitik BJTDokumen11 halamanLaporan Karaktersitik BJTPrillyaBelum ada peringkat

- Linearitas PenguatDokumen26 halamanLinearitas Penguattirta kusumahBelum ada peringkat

- DM DemodDokumen24 halamanDM DemodMiftakhul RohmahBelum ada peringkat

- Laporan Paramater Gerbang LogikaDokumen33 halamanLaporan Paramater Gerbang LogikaYayubaPutraBelum ada peringkat

- CMOS GERBANGDokumen11 halamanCMOS GERBANGDitaBelum ada peringkat

- Zero dan SpanDokumen5 halamanZero dan SpanregaBelum ada peringkat

- TOUCH SWITCHDokumen9 halamanTOUCH SWITCHAditiya Why100% (1)

- PWM MODULASIDokumen39 halamanPWM MODULASIfaridaBelum ada peringkat

- Laporan Paramater Gerbang LogikaDokumen12 halamanLaporan Paramater Gerbang LogikaBayyu PutraBelum ada peringkat

- Elektronika Daya (Soal Dan Jawaban)Dokumen14 halamanElektronika Daya (Soal Dan Jawaban)Siti Marwah Syarif93% (14)

- DifferensiatorDokumen9 halamanDifferensiatorArdiBelum ada peringkat

- 03 TK2A Percobaan2 Penguat Dengan OpampDokumen19 halaman03 TK2A Percobaan2 Penguat Dengan OpampCrowBelum ada peringkat

- Dasar Sistem ProteksiDokumen29 halamanDasar Sistem ProteksiMuhammad Irwan R.Belum ada peringkat

- Karakteristik Arus-Tegangan Pada DiodaDokumen5 halamanKarakteristik Arus-Tegangan Pada DiodaFavianBelum ada peringkat

- DELTA DemodDokumen12 halamanDELTA DemoddevinBelum ada peringkat

- FSK MODULASI LAPORANDokumen19 halamanFSK MODULASI LAPORANDewi Sekar PutihBelum ada peringkat

- Laporan Praktikum Mesin Mesin Listrik PDFDokumen26 halamanLaporan Praktikum Mesin Mesin Listrik PDFwajid oktoryBelum ada peringkat

- 100 - Parameter Dari Elemen Pt2Dokumen4 halaman100 - Parameter Dari Elemen Pt2Rizki Tri PutraBelum ada peringkat

- El2102 1 13213060Dokumen8 halamanEl2102 1 13213060Rosana Dewi AmelindaBelum ada peringkat

- Rangkaian-RCDokumen7 halamanRangkaian-RCSinar MsaBelum ada peringkat

- Modul V PewaktuanDokumen10 halamanModul V PewaktuanAldi FachrurroziBelum ada peringkat

- Bab Ii Op Amp 3Dokumen4 halamanBab Ii Op Amp 3jasminesudibyoBelum ada peringkat

- MODUL L2Dokumen6 halamanMODUL L2Robby AgustianBelum ada peringkat

- IMPEDANSI MATCHINGDokumen7 halamanIMPEDANSI MATCHINGpradanaBelum ada peringkat

- Berkas ELKA 2014 PDFDokumen40 halamanBerkas ELKA 2014 PDFArnoldus Janssen Krisma PambudiBelum ada peringkat

- Analisis Stabilitas Sistem Kelistrikan 6 BusDokumen5 halamanAnalisis Stabilitas Sistem Kelistrikan 6 BusReiza PrasetyaBelum ada peringkat

- C-7 - 01 - Faqih Ahmad Hamami - 120130109 - EL2014 - Akbar Izza M. S PDFDokumen8 halamanC-7 - 01 - Faqih Ahmad Hamami - 120130109 - EL2014 - Akbar Izza M. S PDFCookienamiBelum ada peringkat

- Manual Pemasangan HXE320&HXT300Dokumen3 halamanManual Pemasangan HXE320&HXT300abbotBelum ada peringkat

- 880 1744 1 PBDokumen4 halaman880 1744 1 PBHide AnakbangsaBelum ada peringkat

- Skripsi KedokteranDokumen58 halamanSkripsi KedokteranHide AnakbangsaBelum ada peringkat

- Skripsi Tanpa Bab Pembahasan PDFDokumen77 halamanSkripsi Tanpa Bab Pembahasan PDFFahrian AzhariBelum ada peringkat

- PDF Spek-Produk MUDokumen23 halamanPDF Spek-Produk MUAgusfitriyadi Home100% (2)

- MosfetDokumen173 halamanMosfetBaithul HamdyBelum ada peringkat

- Kupas Tuntas Office 2010 PDFDokumen232 halamanKupas Tuntas Office 2010 PDFHide Anakbangsa100% (1)

- Bab III Atenuasi Dan DistorsiDokumen13 halamanBab III Atenuasi Dan DistorsiRestiBelum ada peringkat

- Panduan Penyusunan Tugas AkhirDokumen52 halamanPanduan Penyusunan Tugas AkhirIman Sii Nambaso75% (8)

- PDF Spek-Produk MUDokumen23 halamanPDF Spek-Produk MUAgusfitriyadi Home100% (2)

- Makalah Etika Profesi Teknik Listrik Pengukuran IsolatorDokumen9 halamanMakalah Etika Profesi Teknik Listrik Pengukuran IsolatortosaanharBelum ada peringkat

- Ebook Gratis - Arduino Untuk Pemula V1Dokumen113 halamanEbook Gratis - Arduino Untuk Pemula V1Sambas Cahyana80% (5)

- Elektronika AnalogDokumen35 halamanElektronika AnalogHide AnakbangsaBelum ada peringkat

- Bab III Atenuasi Dan DistorsiDokumen13 halamanBab III Atenuasi Dan DistorsiRestiBelum ada peringkat

- SISTEM_PENERIMA_TVDokumen56 halamanSISTEM_PENERIMA_TV3riBelum ada peringkat

- Makalah Membuat Usaha BaruDokumen15 halamanMakalah Membuat Usaha Barujayantipratiwi996100% (1)

- Elektronika Analog A PDFDokumen113 halamanElektronika Analog A PDFDimas Darma PambudiBelum ada peringkat

- Pertemuan 4 5 SinyalDokumen49 halamanPertemuan 4 5 SinyalQuinta Nadya MadraBelum ada peringkat

- Pertemuan 4 5 SinyalDokumen49 halamanPertemuan 4 5 SinyalQuinta Nadya MadraBelum ada peringkat

- Perspektif Wirausaha Sikap Dan Mental WiDokumen26 halamanPerspektif Wirausaha Sikap Dan Mental WiDevikaBelum ada peringkat

- VLSI Percobaan 2Dokumen11 halamanVLSI Percobaan 2Neas GintingBelum ada peringkat

- VLSI Percobaan 2Dokumen11 halamanVLSI Percobaan 2Neas GintingBelum ada peringkat

- Bab35 Noise Dan DistorsiDokumen25 halamanBab35 Noise Dan DistorsiBagus FatkhurroziBelum ada peringkat

- IC 4017B SINCRONUS COUNTERDokumen32 halamanIC 4017B SINCRONUS COUNTERHide AnakbangsaBelum ada peringkat

- Analisis Sistem PengendalianDokumen4 halamanAnalisis Sistem PengendalianAlif AriyadiBelum ada peringkat