Aoz1212ai PDF

Diunggah oleh

060279Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Aoz1212ai PDF

Diunggah oleh

060279Hak Cipta:

Format Tersedia

AOZ1212

EZBuck™ 3A Simple Buck Regulator

General Description Features

The AOZ1212 is a high efficiency, simple to use, 3A buck ● 4.5V to 27V operating input voltage range

regulator flexible enough to be optimized for a variety of ● 70mΩ internal NFET, efficiency: up to 95%

applications. The AOZ1212 works from a 4.5V to 27V

● Internal soft start

input voltage range, and provides up to 3A of continuous

output current on each buck regulator output. The output ● Output voltage adjustable down to 0.8V

voltage is adjustable down to 0.8V. ● 3A continuous output current

● Fixed 370kHz PWM operation

The AOZ1212 comes in an SO-8 or DFN-8 package and

is rated over a -40°C to +85°C ambient temperature ● Cycle-by-cycle current limit

range. ● Short-circuit protection

● Thermal shutdown

● Small size SO-8 or DFN-8 package

Applications

● Point of load DC/DC conversion

● Set top boxes

● DVD drives and HDD

● LCD monitors and TVs

● Cable modems

● Telecom/networking/datacom equipment

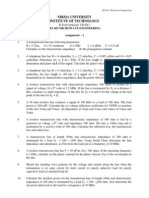

Typical Application

C7

VIN

C1

22µF

VIN BS L1

6.8µH

VOUT

EN LX

AOZ1212 R1

VBIAS FB C2, C3

22µF

C4 R2

COMP GND

RC

CC

Figure 1. 3.3V/3A Buck Regulator

Rev. 1.7 November 2010 www.aosmd.com Page 1 of 18

AOZ1212

Ordering Information

Part Number Ambient Temperature Range Package Environmental

AOZ1212AI -40°C to +85°C SO-8 RoHS Compliant

AOZ1212DI -40°C to +85°C 5 x 4 DFN-8 Green Product

AOS Green Products use reduced levels of Halogens, and are also RoHS compliant.

Please visit www.aosmd.com/web/quality/rohs_compliant.jsp for additional information.

Pin Configuration

LX 1 8 VBIAS LX 1 8 VBIAS

BST 2 7 VIN VIN

BST 2 7 VIN

GND 3 6 EN GND 3 6 EN

GND

FB 4 5 COMP FB 4 5 COMP

SO-8 DFN-8

(Top View) (Top Thru View)

Pin Description

Pin Number Pin Name Pin Function

1 LX PWM output connection to inductor. LX pin needs to be connected externally. Thermal connection

for output stage.

2 BST Bootstrap voltage input. High side driver supply. Connected to 0.1µF capacitor between BST and

LX.

3 GND Ground.

4 FB Feedback input. It is regulated to 0.8V. The FB pin is used to determine the PWM output voltage

via a resistor divider between the output and GND.

5 COMP External loop compensation. Output of internal error amplifier. Connect a series RC network to

GND for control loop compensation.

6 EN Enable pin. The enable pin is active HIGH. Connect EN pin to VIN if not used. Do not leave the EN

pin floating.

7 VIN Supply voltage input. Range from 4.5V to 27V. When VIN rises above the UVLO threshold the

device starts up. All VIN pins need to be connected externally.

8 VBIAS Compensation pin of internal linear regulator. Place put a 1µF capacitor between this pin and

ground.

Rev. 1.7 November 2010 www.aosmd.com Page 2 of 18

AOZ1212

Block Diagram

VIN

+5V

VBIAS

EN UVLO 5V LDO OTP

& POR Regulator

+

ISen

–

Reference Softstart

& Bias BST

ILimit

Q1

GM = 200µA/V +

0.8V + PWM

EAmp –

PWM

Control

FB – Comp

Logic

+

LX

COMP

Frequency 370kHz/24kHz Q2

Foldback Oscillator

Comparator

+

0.2V –

GND

Absolute Maximum Ratings Recommended Operating Conditions

Exceeding the Absolute Maximum Ratings may damage the device. The device is not guaranteed to operate beyond the Recom-

mended Operating Conditions.

Parameter Rating

Parameter Rating

Supply Voltage (VIN) 30V

LX to GND -0.7V to VIN+0.3V Supply Voltage (VIN) 4.5V to 27V

EN to GND -0.3V to VIN+0.3V Output Voltage Range 0.8V to 0.85*VIN

FB to GND -0.3V to 6V Ambient Temperature (TA) -40°C to +85°C

COMP to GND -0.3V to 6V Package Thermal Resistance (ΘJA)(2)

BST to GND VLX+6V SO-8 105°C/W

VBIAS to GND -0.3V to 6V

DFN-8 53°C/W

Junction Temperature (TJ) +150°C Note:

2. The value of ΘJA is measured with the device mounted on 1-in2

Storage Temperature (TS) -65°C to +150°C FR-4 board with 2oz. Copper, in a still air environment with TA =

ESD Rating: Human Body Model(1) 2kV 25°C. The value in any given application depends on the user's spe-

cific board design.

Note:

1. Devices are inherently ESD sensitive, handling precautions are

required. Human body model rating: 1.5kΩ in series with 100pF.

Rev. 1.7 November 2010 www.aosmd.com Page 3 of 18

AOZ1212

Electrical Characteristics

TA = 25°C, VIN = VEN = 12V, VOUT = 3.3V unless otherwise specified(3)

Symbol Parameter Conditions Min. Typ. Max. Units

VIN Supply Voltage 4.5 27 V

VUVLO Input Under-Voltage Lockout Threshold VIN Rising 4.3

V

VIN Falling 4.1

IIN Supply Current (Quiescent) IOUT = 0, VFB = 1.2V, VEN > 2V 2 3 mA

IOFF Shutdown Supply Current VEN = 0V 3 20 µA

VFB Feedback Voltage 0.782 0.8 0.818 V

Load Regulation 0.5 %

Line Regulation 0.08 %/V

IFB Feedback Voltage Input Current 200 nA

ENABLE

VEN EN Input Threshold Off Threshold 0.6

V

On Threshold 2.5

VHYS EN Input Hysteresis 200 mV

IEN Enable Sink/Source Current 50 nA

MODULATOR

fO Frequency 315 370 425 kHz

DMAX Maximum Duty Cycle 85 %

DMIN Minimum Duty Cycle 6 %

GVEA Error Amplifier Voltage Gain 500 V/ V

GEA Error Amplifier Transconductance 200 µA / V

PROTECTION

ILIM Current Limit 4.0 6.0 A

Over-Temperature Shutdown Limit TJ Rising 145

°C

TJ Falling 100

fSC Short Circuit Hiccup Frequency VFB = 0V 24 kHz

tSS Soft Start Interval 6 ms

PWM OUTPUT STAGE

RDS(ON) High-Side Switch On-Resistance 70 100 mΩ

High-Side Switch Leakage VEN = 0V, VLX = 0V 10 µA

Note:

3. Specification in BOLD indicate an ambient temperature range of -40°C to +85°C. These specifications are guaranteed by design.

Rev. 1.7 November 2010 www.aosmd.com Page 4 of 18

AOZ1212

Typical Performance Characteristics

Circuit of Figure 1. TA = 25°C, VIN = VEN = 24V, VOUT = 3.3V unless otherwise specified.

Light Load (DCM) Operation Full Load (CCM) Operation

Vin ripple Vin ripple

0.1V/div 0.1V/div

Vo ripple Vo ripple

20mV/div 20mV/div

IL IL

1A/div 1A/div

VLX VLX

20V/div 20V/div

1μs/div 1μs/div

Startup to Full Load Short Circuit Protection

Vo Vo

2V/div 2V/div

lL

lin 2A/div

0.5A/div

2ms/div 200μs/div

50% to 100% Load Transient Short Circuit Recovery

Vo Ripple Vo

200mV/div 2V/div

lo

IL

1A/div

2A/div

200μs/div 2ms/div

Rev. 1.7 November 2010 www.aosmd.com Page 5 of 18

AOZ1212

Efficiency Curves

Efficiency Efficiency

VIN = 5V VIN = 12V

100 100

8.0V OUTPUT

95 95

3.3V OUTPUT

Efficieny (%)

Efficieny (%)

5.0V OUTPUT

90 90

3.3V OUTPUT

1.8V OUTPUT

85 85

80 80

75 75

0.2 0.5 0.8 1.1 1.4 1.7 2.0 2.3 2.6 2.9 3.2 0.2 0.5 0.8 1.1 1.4 1.7 2.0 2.3 2.6 2.9 3.2

Current (A) Current (A)

Efficiency

VIN = 24V

100

95

8.0V OUTPUT

Efficieny (%)

90

5.0V OUTPUT

85

3.3V OUTPUT

80

75

0.2 0.5 0.8 1.1 1.4 1.7 2.0 2.3 2.6 2.9 3.2

Current (A)

Rev. 1.7 November 2010 www.aosmd.com Page 6 of 18

AOZ1212

Detailed Description high-side switch is off. The inductor current is free-

wheeling through the Schottky diode to the output.

The AOZ1212 is a current-mode step down regulator

with integrated high side NMOS switch. It operates from

a 4.5V to 27V input voltage range and supplies up to 3A Switching Frequency

of load current. The duty cycle can be adjusted from 6% The AOZ1212 switching frequency is fixed and set by

to 85% allowing a wide range of output voltages. Fea- an internal oscillator. The switching frequency is set to

tures include enable control, Power-On Reset, input 370kHz.

under voltage lockout, fixed internal soft-start and ther-

mal shut down. Output Voltage Programming

The AOZ1212 is available in an SO-8 or DFN-8 package. Output voltage can be set by feeding back the output to

the FB pin with a resistor divider network. In the applica-

Enable and Soft Start tion circuit shown in Figure 1. The resistor divider

network includes R1 and R2. Typically, a design is started

The AOZ1212 has an internal soft start feature to limit

by picking a fixed R2 value and calculating the required

in-rush current and ensure the output voltage ramps up

smoothly to the regulation voltage. A soft start process R1 value with equation below.

begins when the input voltage rises to 4.1V and voltage ⎛ R 1⎞

on EN pin is HIGH. In the soft start process, the output V O = 0.8 × ⎜ 1 + -------⎟

voltage is typically ramped to regulation voltage in 6.8ms. ⎝ R 2⎠

The 6.8ms soft start time is set internally.

Some standard values for R1 and R2 for the most

If the enable function is not used, connect the EN pin to commonly used output voltages are listed in Table 1.

VIN. Pulling EN to ground will disable the AOZ1212. Do

not leave EN open. The voltage on the EN pin must be Table 1.

above 2.5 V to enable the AOZ1212. When voltage on

VO (V) R1 (kΩ) R2 (kΩ)

EN pin falls below 0.6V, the AOZ1212 is disabled. If an

application circuit requires the AOZ1212 to be disabled, 0.8 1.0 Open

an open drain or open collector circuit should be used to 1.2 4.99 10

interface with the EN pin.

1.5 10 11.5

Steady-State Operation 1.8 12.7 10.2

2.5 21.5 10

Under steady-state conditions, the converter operates in

fixed frequency and Continuous-Conduction Mode 3.3 31.6 10

(CCM). 5.0 52.3 10

The AOZ1212 integrates an internal N-MOSFET as the

high-side switch. Inductor current is sensed by amplifying The combination of R1 and R2 should be large enough to

the voltage drop across the drain to source of the high avoid drawing excessive current from the output, which

side power MOSFET. Since the N-MOSFET requires a will cause power loss.

gate voltage higher than the input voltage, a boost

capacitor connected between the LX and BST pins drives Protection Features

the gate. The boost capacitor is charged while LX is low. The AOZ1212 has multiple protection features to prevent

An internal 10Ω switch from LX to GND is used to ensure system circuit damage under abnormal conditions.

that LX is pulled to GND even in the light load. Output

voltage is divided down by the external voltage divider at Over Current Protection (OCP)

the FB pin. The difference of the FB pin voltage and The sensed inductor current signal is also used for over

reference is amplified by the internal transconductance current protection. Since the AOZ1212 employs peak

error amplifier. The error voltage, which shows on the current mode control, the COMP pin voltage is propor-

COMP pin, is compared against the current signal. The tional to the peak inductor current. The COMP pin volt-

current signal is the sum of inductor current signal and age is limited to be between 0.4V and 2.5V internally.

ramp compensation signal, at the PWM comparator The peak inductor current is automatically limited cycle

input. If the current signal is less than the error voltage, by cycle.

the internal high-side switch is on. The inductor current

flows from the input through the inductor to the output. The cycle-by-cycle current limit threshold is internally set.

When the current signal exceeds the error voltage, the When the load current reaches the current limit thresh-

old, the cycle-by-cycle current limit circuit turns off the

Rev. 1.7 November 2010 www.aosmd.com Page 7 of 18

AOZ1212

high side switch immediately to terminate the current another concern when selecting the capacitor. For a buck

duty cycle. The inductor current stops rising. The cycle- circuit, the RMS value of input capacitor current can be

by-cycle current limit protection directly limits inductor calculated by:

peak current. The average inductor current is also limited

due to the limitation on the peak inductor current. When VO ⎛ VO ⎞

cycle-by-cycle current limit circuit is triggered, the output I CIN_RMS = I O × --------- ⎜ 1 – ---------⎟

V IN ⎝ V IN⎠

voltage drops as the duty cycle decreases.

The AOZ1212 has internal short circuit protection to if let m equal the conversion ratio:

protect itself from catastrophic failure under output short VO

circuit conditions. The FB pin voltage is proportional to --------

- = m

the output voltage. Whenever the FB pin voltage is below V IN

0.2V, the short circuit protection circuit is triggered. To

prevent current limit running away when the comp pin The relationship between the input capacitor RMS

voltage is higher than 2.1V, the short circuit protection is current and voltage conversion ratio is calculated and

also triggered. As a result, the converter is shut down shown in Figure 2. It can be seen that when VO is half of

and hiccups at a frequency equals to 1/16 of normal VIN, CIN is under the worst current stress. The worst

switching frequency. The converter will start up via a soft current stress on CIN is 0.5 x IO.

start once the short circuit condition is resolved. In short

0.5

circuit protection mode, the inductor average current is

greatly reduced because of the low hiccup frequency. 0.4

Power-On Reset (POR)

ICIN_RMS(m) 0.3

A power-on reset circuit monitors the input voltage. IO

When the input voltage exceeds 4.3V, the converter 0.2

starts operation. When input voltage falls below 4.1V,

the converter will stop switching. 0.1

Thermal Protection 0

0 0.5 1

An internal temperature sensor monitors the junction m

temperature. It shuts down the internal control circuit and Figure 2. ICIN vs. Voltage Conversion Ratio

high side NMOS if the junction temperature exceeds For reliable operation and best performance, the input

145°C. The regulator will restart automatically under the capacitors must have a current rating higher than

control of soft-start circuit when the junction temperature ICIN_RMS at the worst operating conditions. Ceramic

decreases to 100°C. capacitors are preferred for input capacitors because of

their low ESR and high ripple current rating. Depending

Application Information on the application circuits, other low ESR tantalum

The basic AOZ1212 application circuit is shown in capacitor or aluminum electrolytic capacitor may also be

Figure 1. Component selection is explained below. used. When selecting ceramic capacitors, X5R or X7R

type dielectric ceramic capacitors are preferred for their

Input Capacitor better temperature and voltage characteristics. Note that

The input capacitor (C1 in Figure 1) must be connected to the ripple current rating from capacitor manufactures is

the VIN pin and GND pin of the AOZ1212 to maintain based on certain amount of life time. Further de-rating

steady input voltage and filter out the pulsing input may be necessary for practical design requirement.

current. The voltage rating of the input capacitor must be

Inductor

greater than maximum input voltage + ripple voltage.

The inductor is used to supply constant current to output

The input ripple voltage can be approximated by equa- when it is driven by a switching voltage. For given input

tion below: and output voltage, inductance and switching frequency

IO ⎛ VO ⎞ VO together decide the inductor ripple current, which is,

ΔV IN = ----------------- × ⎜ 1 – ---------⎟ × ---------

f × C IN ⎝ V IN⎠ V IN VO ⎛ VO ⎞

ΔI L = ----------- × ⎜ 1 – ---------⎟

f×L ⎝ V IN⎠

Since the input current is discontinuous in a buck

converter, the current stress on the input capacitor is

Rev. 1.7 November 2010 www.aosmd.com Page 8 of 18

AOZ1212

The peak inductor current is:

ΔI L If the impedance of ESR at switching frequency

I Lpeak = I O + -------- dominates, the output ripple voltage is mainly decided by

2 capacitor ESR and inductor ripple current. The output

ripple voltage calculation can be further simplified to:

High inductance gives low inductor ripple current but

requires larger size inductor to avoid saturation. Low ΔV O = ΔI L × ESR CO

ripple current reduces inductor core losses. It also

reduces RMS current through inductor and switches, For lower output ripple voltage across the entire operat-

which results in less conduction loss. ing temperature range, X5R or X7R dielectric type of

When selecting the inductor, make sure it is able to ceramic, or other low ESR tantalum capacitor or

handle the peak current without saturation even at the aluminum electrolytic capacitor may also be used as out-

highest operating temperature. put capacitors.

The inductor takes the highest current in a buck circuit. In a buck converter, output capacitor current is continu-

The conduction loss on inductor needs to be checked for ous. The RMS current of output capacitor is decided by

thermal and efficiency requirements. the peak to peak inductor ripple current. It can be calcu-

lated by:

Surface mount inductors in different shape and styles are

available from Coilcraft, Elytone and Murata. Shielded ΔI L

I CO_RMS = ----------

inductors are small and radiate less EMI noise. But they 12

cost more than unshielded inductors. The choice

depends on EMI requirement, price and size. Usually, the ripple current rating of the output capacitor is

a smaller issue because of the low current stress. When

Output Capacitor the buck inductor is selected to be very small and induc-

The output capacitor is selected based on the DC output tor ripple current is high, output capacitor could be over-

voltage rating, output ripple voltage specification and stressed.

ripple current rating.

Schottky Diode Selection

The selected output capacitor must have a higher rated

The external freewheeling diode supplies the current to

voltage specification than the maximum desired output

the inductor when the high side NMOS switch is off. To

voltage including ripple. De-rating needs to be consid-

reduce the losses due to the forward voltage drop and

ered for long term reliability.

recovery of diode, a Schottky diode is recommended.

Output ripple voltage specification is another important The maximum reverse voltage rating of the chosen

factor for selecting the output capacitor. In a buck con- Schottky diode should be greater than the maximum

verter circuit, output ripple voltage is determined by input voltage, and the current rating should be greater

inductor value, switching frequency, output capacitor than the maximum load current.

value and ESR. It can be calculated by the equation

below: Loop Compensation

1

ΔV O = ΔI L × ⎛ ESR CO + -------------------------⎞ The AOZ1212 employs peak current mode control for

⎝ 8×f×C ⎠ easy use and fast transient response. Peak current mode

O

control eliminates the double pole effect of the output

where; L&C filter. It greatly simplifies the compensation loop

CO is output capacitor value and design.

ESRCO is the Equivalent Series Resistor of output capacitor. With peak current mode control, the buck power stage

can be simplified to be a one-pole and one-zero system

When low ESR ceramic capacitor is used as output in frequency domain. The pole is the dominant pole and

capacitor, the impedance of the capacitor at the switch- can be calculated by:

ing frequency dominates. Output ripple is mainly caused

by capacitor value and inductor ripple current. The output 1

f p1 = -----------------------------------

ripple voltage calculation can be simplified to: 2π × C O × R L

1

ΔV O = ΔI L × ⎛ -------------------------⎞

⎝8 × f × C ⎠

O

Rev. 1.7 November 2010 www.aosmd.com Page 9 of 18

AOZ1212

The zero is a ESR zero due to output capacitor and its The strategy for choosing RC and CC is to set the cross

ESR. It is can be calculated by: over frequency with RC and set the compensator zero

with CC. Using selected crossover frequency, fC, to

1

f Z1 = ------------------------------------------------ calculate RC:

2π × C O × ESR CO

VO 2π × C O

where; R C = f C × ---------- × ------------------------------

V G ×G

FB EA CS

CO is the output filter capacitor,

RL is load resistor value, and where;

ESRCO is the equivalent series resistance of output capacitor. fC is desired crossover frequency,

VFB is 0.8V,

The compensation design is actually to shape the

converter close loop transfer function to get desired gain GEA is the error amplifier transconductance, which is 200x10-6

A/V, and

and phase. Several different types of compensation

network can be used for AOZ1212. For most cases, a GCS is the current sense circuit transconductance, which is

series capacitor and resistor network connected to the 5.64 A/V

COMP pin sets the pole-zero and is adequate for a stable The compensation capacitor CC and resistor RC together

high-bandwidth control loop. make a zero. This zero is put somewhere close to the

In the AOZ1212, FB pin and COMP pin are the inverting dominate pole fp1 but lower than 1/5 of the selected

input and the output of internal transconductance error crossover frequency. CC can is selected by:

amplifier. A series R and C compensation network

1.5

connected to COMP provides one pole and one zero. C C = -----------------------------------

The pole is: 2π × R C × f p1

G EA The equation above can also be simplified to:

f p2 = -------------------------------------------

2π × C C × G VEA

CO × RL

where; C C = ---------------------

RC

GEA is the error amplifier transconductance, which is 200 x 10-6

A/V, An easy-to-use application software which helps to

GVEA is the error amplifier voltage design and simulate the compensation loop can be found

at www.aosmd.com.

The zero given by the external compensation network,

capacitor CC (C5 in Figure 1) and resistor RC (R1 in Thermal Management and Layout

Figure 1), is located at: Consideration

1 In the AOZ1212 buck regulator circuit, high pulsing

f Z2 = ----------------------------------- current flows through two circuit loops. The first loop

2π × C C × R C

starts from the input capacitors, to the VIN pin, to the LX

To design the compensation circuit, a target crossover pins, to the filter inductor, to the output capacitor and

frequency fC for close loop must be selected. The system load, and then returns to the input capacitor through

crossover frequency is where the control loop has unity ground. Current flows in the first loop when the high side

gain. The crossover frequency is also called the switch is on. The second loop starts from inductor, to the

converter bandwidth. Generally a higher bandwidth output capacitors and load, to the GND pin of the

means faster response to load transient. However, the AOZ1212, to the LX pins of the AZO1212. Current flows

bandwidth should not be too high due to system stability in the second loop when the low side diode is on.

concern. When designing the compensation loop, In PCB layout, minimizing the two loops area reduces the

converter stability under all line and load condition must noise of this circuit and improves efficiency. A ground

be considered. plane is recommended to connect input capacitor, output

Usually, it is recommended to set the bandwidth to be capacitor, and GND pin of the AOZ1212.

less than 1/10 of switching frequency. It is recommended In the AOZ1212 buck regulator circuit, the three major

to choose a crossover frequency less than 30kHz. power dissipating components are the AOZ1212,

f C = 30kHz external diode and output inductor. The total power

Rev. 1.7 November 2010 www.aosmd.com Page 10 of 18

AOZ1212

dissipation of converter circuit can be measured by input Several layout tips are listed below for the best electric

power minus output power. and thermal performance. Figure 3a and Figure 3b show

layout examples for the AOZ1212A and AOZ1212D

P total_loss = V IN × I IN – V O × I O respectively.

The power dissipation of inductor can be approximately 1. Do not use thermal relief connection to the VIN and

calculated by output current and DCR of the inductor. the GND pin. Pour a maximized copper area to the

GND pin and the VIN pin to help thermal dissipation.

P inductor_loss = IO2 × R inductor × 1.1

2. Input capacitor should be connected as close as

possible to the VIN and GND pins.

The power dissipation of the diode is:

3. Make the current trace from LX pins to L to CO to

⎛ VO ⎞ GND as short as possible.

P diode_loss = I O × V F × ⎜ 1 – ---------⎟

⎝ V IN⎠ 4. Pour copper plane on all unused board area and

connect it to stable DC nodes, like VIN, GND or

The actual AOZ1212 junction temperature can be VOUT.

calculated with power dissipation in the AOZ1212 and 5. Keep sensitive signal traces such as the trace

thermal impedance from junction to ambient. connecting FB and COMP pins away from the

T junction = ( P total_loss – P inductor_loss ) × Θ JA LX pins.

+ + T ambient

The maximum junction temperature of AOZ1212 is

145°C, which limits the maximum load current capability.

The thermal performance of the AOZ1212 is strongly

affected by the PCB layout. Care should be taken by

users during design process to ensure that the IC will

operate under the recommended environmental

conditions.

Rev. 1.7 November 2010 www.aosmd.com Page 11 of 18

AOZ1212

R2

Cc Rc

C1 5 COMP 4 FB

AOZ1210 /2

R1

VIN 6 EN 3 GND

7 Vin 2 BST

Cb

8 VBIAS 1 LX

C4

L1

Vo

C

C2

2

Figure 3a. Layout Example for AOZ1212AI

R2

Cc Rc

COMP 5 4 FB

R1

GND

EN 6 3 GND

Vin 7 2 BST

Vin

Cb

C1

VBIAS LX

8 1

C4

Vo

L1

C

C2

2

Figure 3b. Layout Example for AOZ1212DI

Rev. 1.7 November 2010 www.aosmd.com Page 12 of 18

AOZ1212

Package Dimensions, SO-8

D Gauge Plane Seating Plane

e 0.25

8

L

E E1

h x 45°

1 C

θ

7° (4x)

A2 A

0.1

b A1

Dimensions in millimeters Dimensions in inches

Symbols Min. Nom. Max. Symbols Min. Nom. Max.

2.20

A 1.35 1.65 1.75 A 0.053 0.065 0.069

A1 0.10 — 0.25 A1 0.004 — 0.010

A2 1.25 1.50 1.65 A2 0.049 0.059 0.065

b 0.31 — 0.51 b 0.012 — 0.020

5.74 c 0.17 — 0.25 c 0.007 — 0.010

D 4.80 4.90 5.00 D 0.189 0.193 0.197

E1 3.80 3.90 4.00 E1 0.150 0.154 0.157

1.27 e 1.27 BSC e 0.050 BSC

E 5.80 6.00 6.20 E 0.228 0.236 0.244

h 0.25 — 0.50 h 0.010 — 0.020

L 0.40 — 1.27 L 0.016 — 0.050

0.80

Unit: mm θ 0° — 8° θ 0° — 8°

Notes:

1. All dimensions are in millimeters.

2. Dimensions are inclusive of plating

3. Package body sizes exclude mold flash and gate burrs. Mold flash at the non-lead sides should be less than 6 mils.

4. Dimension L is measured in gauge plane.

5. Controlling dimension is millimeter, converted inch dimensions are not necessarily exact.

Rev. 1.7 November 2010 www.aosmd.com Page 13 of 18

AOZ1212

Tape and Reel Dimensions, SO-8

SO-8 Carrier Tape P1 See Note 3

D1

P2

T

See Note 5

E1

E2 E

See Note 3

B0

K0 D0

A0 P0 Feeding Direction

Unit: mm

Package A0 B0 K0 D0 D1 E E1 E2 P0 P1 P2 T

SO-8 6.40 5.20 2.10 1.60 1.50 12.00 1.75 5.50 8.00 4.00 2.00 0.25

(12mm) ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10 ±0.10

SO-8 Reel

W1

S

G

N K

M

V

R

H

Tape Size Reel Size M N W W1 H K S G R V

12mm ø330 ø330.00 ø97.00 13.00 17.40 ø13.00 10.60 2.00 — — —

±0.50 ±0.10 ±0.30 ±1.00 +0.50/-0.20 ±0.50

SO-8 Tape

Leader/Trailer

& Orientation

Trailer Tape Components Tape Leader Tape

300mm min. or Orientation in Pocket 500mm min. or

75 empty pockets 125 empty pockets

Rev. 1.7 November 2010 www.aosmd.com Page 14 of 18

AOZ1212

Package Dimensions, 5x4A DFN-8

e

L3*

L

D

Index Area

(D/2 x E/2) D/2 L2* L1 E2

Pin #1 IDA

E/2 Option 1

E

L2*

D3 D2 Chamfer 0.30

BOTTOM VIEW

TOP VIEW

A3

Pin #1 IDA

A Seating Option 2

Plane

b R

BOTTOM VIEW

FRONT VIEW

Dimensions in millimeters Dimensions in inches

RECOMMENDED LAND PATTERN Symbols Min. Nom. Max. Symbols Min. Nom. Max.

A 0.70 0.75 0.80 A 0.028 0.30 0.032

0.50 Typ.

A3 0.20 Ref. A3 0.008 Ref.

0.95 Typ.

b 0.40 0.45 0.50 b 0.016 0.018 0.020

0.285

D 4.90 5.00 5.10 D 0.190 0.200 0.201

D2 2.05 2.15 2.25 D2 0.080 0.085 0.089

D3 1.66 1.76 1.86 D3 0.064 0.070 0.074

2.25 1.86

0.65 E 3.90 4.00 4.10 E 0.154 0.157 0.161

1.165

4.20 2.33 E2 2.23 2.33 2.43 E2 0.088 0.092 0.096

0.40 e 0.95 BSC e 0.037 BSC

L 0.50 0.55 0.60 L 0.020 0.022 0.024

L1 — 0.40 — L1 — 0.016 —

0.285 L2 0.285 Ref. L2 0.011 Ref.

L3 0.835 Ref. L3 0.033 Ref.

4.51 R 0.30 Ref. R 0.012 Ref.

aaa 0.15 aaa 0.006

bbb 0.10 bbb 0.004

ccc 0.10 ccc 0.004

Notes:

ddd 0.08 ddd 0.003

1. Dimensions and tolerancing conform to ASME Y14.5M-1994.

eee 0.05 eee 0.002

2. All dimensions are in millimeters.

3. The location of the terminal #1 identifier and terminal numbering convention conforms to JEDEC publication 95 SP-002.

4. Dimension b applies to metallized terminal and is measured between 0.15mm and 0.30mm from the terminal tip. If the terminal has the

optional radius on the other end of the terminal, the dimension b should not be measured in that radius area.

5. Coplanarity applies to the terminals and all other bottom surface metallization.

6. Drawing shown are for illustration only.

7. The dimensions with * are just for reference

8. Pin #3 and Pin #7 are fused to DAP.

Rev. 1.7 November 2010 www.aosmd.com Page 15 of 18

AOZ1212

Tape and Reel Dimensions, 5x4A DFN-8

Tape

R0

.40

0.

T

20

D1

E1

E2 D0

E

B0

Feeding

Direction

K0 P0 A0

UNIT: mm

Package A0 B0 K0 D0 D1 E E1 E2 P0 P1 P2 T

DFN 5x4 5.30 4.30 1.20 1.50 1.50 12.00 1.75 5.50 8.00 4.00 2.00 0.30

(12 mm) ±0.10 ±0.10 ±0.10 Min. +0.10 / –0 ±0.30 ±0.10 ±0.10 ±0.10 ±0.20 ±0.10 ±0.05

Typ.

Leader/Trailer and Orientation

Trailer Tape Components Tape Leader Tape

300mm Min. Orientation in Pocket 500mm Min.

Rev. 1.7 November 2010 www.aosmd.com Page 16 of 18

AOZ1212

Reel

59

R1

II I

R1 6.0±1

M 21

R1 I

27

Zoom In

R1

R6

P

R5

B

5

W1

III

Zoom In

Tape Size Reel Size M W1 B P 3-1.8

0.05

ø330 12.40 2.40 0.5

12mm ø330 +0.3 +2.0 ±0.3

-4.0 -0.0

II

Zoom In

A

/8"

3-

ø2

"

3-ø1

/4

.9

ø1

±0 N=ø100±2

A A

3-

. 05

0.2

6±

ø9

1.8

6.0

6.45±0.05

1.8

0.00

6.2 8.00 -0.05

R1

ø2 2.20

0

8.9±0.1

1.

20 ø90.0 2.00

14 REF

5.0

0

ø17.0 ø13.0

C

R1.10

1.8

R3.10

11.90 12 REF

ø86 46.0±0.1

.0±0 R0.5

.1

10°

44.5±0.1

41.5 REF

43.00 3.3

44.5±0.1

.95

6.50 4.0

R3

6.10 38°

40°

10.0

F

RE

VIEW: C 2.5

A 0.80

8

R4

3- 3.00 1.80

ø3 8.0±0.1

6"

/1

/1

+0.05

2.00 6"

ø3

8.000.00

3-

6.50

10.71

6°

Rev. 1.7 November 2010 www.aosmd.com Page 17 of 18

AOZ1212

Part Marking

AOZ1212AI

Z1212AI

Part Number

FAYWLT

Fab & Assembly Location Assembly Lot Code

Year & Week Code

AOZ1212DI

Z1212DI

Part Number

FAYWLT

Fab & Assembly Location Assembly Lot Code

Year & Week Code

This data sheet contains preliminary data; supplementary data may be published at a later date.

Alpha & Omega Semiconductor reserves the right to make changes at any time without notice.

LIFE SUPPORT POLICY

ALPHA & OMEGA SEMICONDUCTOR PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL

COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS.

As used herein:

1. Life support devices or systems are devices or 2. A critical component in any component of a life

systems which, (a) are intended for surgical implant into support, device, or system whose failure to perform can

the body or (b) support or sustain life, and (c) whose be reasonably expected to cause the failure of the life

failure to perform when properly used in accordance support device or system, or to affect its safety or

with instructions for use provided in the labeling, can be effectiveness.

reasonably expected to result in a significant injury of

the user.

Rev. 1.7 November 2010 www.aosmd.com Page 18 of 18

Anda mungkin juga menyukai

- Viper22a Equivalent PDFDokumen16 halamanViper22a Equivalent PDFXande Nane Silveira0% (1)

- Acopos PDFDokumen19 halamanAcopos PDFHoàng Mỹ NguyễnBelum ada peringkat

- Leaflet Delem Profile-W enDokumen2 halamanLeaflet Delem Profile-W enTanvon MalikBelum ada peringkat

- Manual OmbiraDokumen16 halamanManual Ombirazz2nktBelum ada peringkat

- PL Ga800 01 PDFDokumen50 halamanPL Ga800 01 PDFBock DharmaBelum ada peringkat

- Esquema La-E993pDokumen78 halamanEsquema La-E993pc4rl0slinuxBelum ada peringkat

- Valmet IQ Total Ash Measurement: Safety and PrinciplesDokumen7 halamanValmet IQ Total Ash Measurement: Safety and PrinciplesRandika SudarmaBelum ada peringkat

- EPower 029669 5 PDFDokumen14 halamanEPower 029669 5 PDFrajabharath12Belum ada peringkat

- PDF 6ES7422 1BH10 0AA0Dokumen3 halamanPDF 6ES7422 1BH10 0AA0sadeghBelum ada peringkat

- SEKO Kompact PDFDokumen4 halamanSEKO Kompact PDFRuber TorresBelum ada peringkat

- Electrocraft Reliance Servo Drive Repair ServiceDokumen1 halamanElectrocraft Reliance Servo Drive Repair ServiceBanu Chandar0% (1)

- Pws 5610 TDokumen2 halamanPws 5610 Tapi-283278192Belum ada peringkat

- KQ330Dokumen20 halamanKQ330Darlin LizcanoBelum ada peringkat

- Catalogo GeralDokumen12 halamanCatalogo GeralAnderson De Souza JesusBelum ada peringkat

- CFW11 EtherNetIP RSLogixDokumen13 halamanCFW11 EtherNetIP RSLogixPatricio DíazBelum ada peringkat

- Prowirl 72 Operating InstructionsDokumen120 halamanProwirl 72 Operating Instructionsangrypepper100% (1)

- MT6070iH Spec Eng 110607Dokumen2 halamanMT6070iH Spec Eng 110607rmorenodx4587Belum ada peringkat

- Toshiba Satellite M300 M305 Quanta TE1 Laptop SchematicsDokumen40 halamanToshiba Satellite M300 M305 Quanta TE1 Laptop SchematicsErick RodriguezBelum ada peringkat

- Semp Toshiba Manual de Servico PDFDokumen49 halamanSemp Toshiba Manual de Servico PDFAnildo Eldivar De Oliveira SarmentoBelum ada peringkat

- Analog Input Module 6ES7 331-7NF00-0AB0Dokumen9 halamanAnalog Input Module 6ES7 331-7NF00-0AB0Trần Quang LinhBelum ada peringkat

- Datasheet LD7523 PDFDokumen18 halamanDatasheet LD7523 PDFIvica ConićBelum ada peringkat

- Ic 693 Cpu 313Dokumen5 halamanIc 693 Cpu 313mubashersaeedBelum ada peringkat

- NDS3542 Encoder Modulator GuideDokumen6 halamanNDS3542 Encoder Modulator GuideBoezall SiamBelum ada peringkat

- Gefran GTF Xtra ManualDokumen29 halamanGefran GTF Xtra ManualjilfBelum ada peringkat

- Jj-Crc-I11 Userguide: Z Frequency 433.92Mhz Z Indicator Light Blue Led Z Working Voltage DC 12VDokumen1 halamanJj-Crc-I11 Userguide: Z Frequency 433.92Mhz Z Indicator Light Blue Led Z Working Voltage DC 12VMishaCvele100% (1)

- D2M004 Bridge Inverter Motor Programming GuideDokumen1 halamanD2M004 Bridge Inverter Motor Programming GuideEricBelum ada peringkat

- LineTroll - 3500 - Fault IndicatorDokumen6 halamanLineTroll - 3500 - Fault IndicatorKristopher HicksBelum ada peringkat

- 11E66919 A HAL2 User GuideDokumen20 halaman11E66919 A HAL2 User GuideElias SantosBelum ada peringkat

- Omron CablesDokumen13 halamanOmron CablescomantonioBelum ada peringkat

- Delta Manual DVP Portugues PDF Parte2Dokumen100 halamanDelta Manual DVP Portugues PDF Parte2Maria JosefaBelum ada peringkat

- Communication All Cables PLC Pinout (Pinagem de Todos Os Cabos de Comunicação PLC)Dokumen3 halamanCommunication All Cables PLC Pinout (Pinagem de Todos Os Cabos de Comunicação PLC)Jaziel CabralBelum ada peringkat

- SIMOTICS S-1FK7 Servomotors: &Rpsdfw6/Qfkurqrxv0Rwruviru0Rwlrq&Rqwuro$SsolfdwlrqvDokumen6 halamanSIMOTICS S-1FK7 Servomotors: &Rpsdfw6/Qfkurqrxv0Rwruviru0Rwlrq&Rqwuro$SsolfdwlrqvDaniel FernándezBelum ada peringkat

- HI311DSB DriverDokumen7 halamanHI311DSB DriverWesley de AlmeidaBelum ada peringkat

- Manual de Variador de Velocidad WEG VECTORDokumen32 halamanManual de Variador de Velocidad WEG VECTORSamuel Miranda PintoBelum ada peringkat

- WEG CFW 11 Variable Speed Drives1Dokumen32 halamanWEG CFW 11 Variable Speed Drives1Marco PosadaBelum ada peringkat

- Teknovus EPON DBA Technical NoteDokumen8 halamanTeknovus EPON DBA Technical Note박철민Belum ada peringkat

- LG 50pa4500-Sf - Ch. Pb21a PDFDokumen48 halamanLG 50pa4500-Sf - Ch. Pb21a PDFJuliano ZanchiBelum ada peringkat

- ABB - ACS850 DriveStudio PDFDokumen2 halamanABB - ACS850 DriveStudio PDFavijit dasBelum ada peringkat

- LG 50PB560B Chassis PU41A PDFDokumen47 halamanLG 50PB560B Chassis PU41A PDFCesar Guzman100% (1)

- LE3U PLC Analog and PIDDokumen3 halamanLE3U PLC Analog and PIDsplinter incBelum ada peringkat

- MT506TV46 DatasheetDokumen2 halamanMT506TV46 DatasheetJederVieiraBelum ada peringkat

- Panasonic Tc-L32e5 CH La35 PDFDokumen69 halamanPanasonic Tc-L32e5 CH La35 PDFAnonymous h80fVW100% (1)

- EM 231 TC 8AI eDokumen4 halamanEM 231 TC 8AI eJaime Saldias0% (1)

- Apostila Completa CodesysDokumen34 halamanApostila Completa CodesysJhony AlvesBelum ada peringkat

- JVC UX-g6s Diagrama EsquematicoDokumen14 halamanJVC UX-g6s Diagrama EsquematicoDjalma MoreiraBelum ada peringkat

- Qirox V7.10eDokumen442 halamanQirox V7.10estorekeyBelum ada peringkat

- Samsung 633nw Ls16cmy SCHDokumen10 halamanSamsung 633nw Ls16cmy SCHrenanBelum ada peringkat

- Pe 194802B Philips Manual DatasheetDokumen14 halamanPe 194802B Philips Manual DatasheetMárcio FernandesBelum ada peringkat

- Andover Continuum Software Compatibility Matrix Versions 1.94Dokumen14 halamanAndover Continuum Software Compatibility Matrix Versions 1.94johnatanflorezBelum ada peringkat

- SR-MT Maximum Power Point Tracking Series Solar charge controller User ManualDokumen16 halamanSR-MT Maximum Power Point Tracking Series Solar charge controller User ManualCarlos LehmanBelum ada peringkat

- Omron CablesDokumen13 halamanOmron CablesRogelio FelixBelum ada peringkat

- Axioo Neon CNC c14 (CZC CPL s01 r48)Dokumen54 halamanAxioo Neon CNC c14 (CZC CPL s01 r48)z3xa5347100% (1)

- Datasheet - Aoz1280 Simple Buck RegulatorDokumen13 halamanDatasheet - Aoz1280 Simple Buck RegulatorCesar ServidoneBelum ada peringkat

- AOZ1282CIDokumen13 halamanAOZ1282CIBelalang TempurBelum ada peringkat

- Ezbuck™ 3A Synchronous Buck Regulator: General Description FeaturesDokumen15 halamanEzbuck™ 3A Synchronous Buck Regulator: General Description FeaturesJulio BarrosBelum ada peringkat

- General Description Features: Ezbuck™ 1.5A Non-Synchronous Buck RegulatorDokumen15 halamanGeneral Description Features: Ezbuck™ 1.5A Non-Synchronous Buck RegulatorLuis AntunesBelum ada peringkat

- AOZ2023PIDokumen11 halamanAOZ2023PIjuliocunachiBelum ada peringkat

- Data SheetDokumen16 halamanData SheetHugo BurgosBelum ada peringkat

- Aoz1017ai DC DCDokumen15 halamanAoz1017ai DC DCVukica IvicBelum ada peringkat

- PIC16F628ADokumen178 halamanPIC16F628AEmanuele100% (1)

- Deskripsi IC LM 386 PDFDokumen28 halamanDeskripsi IC LM 386 PDFmade suciBelum ada peringkat

- Create A HID USB DeviceDokumen6 halamanCreate A HID USB DeviceKevin Jacobson100% (1)

- CM8870Dokumen9 halamanCM8870api-3750426100% (1)

- HT12EDokumen13 halamanHT12Eapi-3700809100% (2)

- Esquema Manager II LDokumen1 halamanEsquema Manager II LValdeir AlmeidaBelum ada peringkat

- PIC16F628ADokumen178 halamanPIC16F628AEmanuele100% (1)

- PIC16F628ADokumen178 halamanPIC16F628AEmanuele100% (1)

- LM1358 Dual Op Amp DatasheetDokumen0 halamanLM1358 Dual Op Amp Datasheet060279Belum ada peringkat

- LM1358 Dual Op Amp DatasheetDokumen0 halamanLM1358 Dual Op Amp Datasheet060279Belum ada peringkat

- Keypad Manual v100Dokumen6 halamanKeypad Manual v100KakashiGanzBelum ada peringkat

- Irf3205 PDFDokumen9 halamanIrf3205 PDFJuanito Naxito Jebus ArjonaBelum ada peringkat

- CodecsDokumen12 halamanCodecs060279Belum ada peringkat

- CodecsDokumen12 halamanCodecs060279Belum ada peringkat

- Data Sheet Rectifier PSR327 220VDC PDFDokumen2 halamanData Sheet Rectifier PSR327 220VDC PDFIancu ConstantinBelum ada peringkat

- Ogawa 2000Dokumen10 halamanOgawa 2000Sarly FebrianaBelum ada peringkat

- Electronics Engineering Course OverviewDokumen143 halamanElectronics Engineering Course OverviewPrakash ManikandanBelum ada peringkat

- Satellite P55-B Detailed Product SpecificationDokumen4 halamanSatellite P55-B Detailed Product Specificationobiwan2009Belum ada peringkat

- Ferroresonance ReportDokumen18 halamanFerroresonance ReportDoydoy Merida100% (1)

- GAIL UPS System Data SheetDokumen7 halamanGAIL UPS System Data SheetPrakash SinhaBelum ada peringkat

- Assignment 01Dokumen1 halamanAssignment 01Karan Jhaveri100% (1)

- Daewoo Dtl-2950 K GB Chassis Cp-650Dokumen74 halamanDaewoo Dtl-2950 K GB Chassis Cp-650eduscribd18Belum ada peringkat

- Operation & Maintenance Training (Rev2.1) Part 1.2Dokumen110 halamanOperation & Maintenance Training (Rev2.1) Part 1.2bbiswajit88eceBelum ada peringkat

- Test Certificate For HT TransformersDokumen1 halamanTest Certificate For HT TransformersRajeev babbarBelum ada peringkat

- Keil C - Embedded C Programming Tutorial - Pointers - 8051 Micro Controller Projects AVR PIC Projects Tutorials Ebooks LibrariesDokumen2 halamanKeil C - Embedded C Programming Tutorial - Pointers - 8051 Micro Controller Projects AVR PIC Projects Tutorials Ebooks LibrariesSameer SharmaBelum ada peringkat

- Irf1404 HEXFET (R) Power MOSFET DatasheetDokumen8 halamanIrf1404 HEXFET (R) Power MOSFET DatasheetMeatheadMerlinBelum ada peringkat

- Avr Ice200 Incircuit EmulatorDokumen2 halamanAvr Ice200 Incircuit Emulatorcarlos augusto do carmo braiaBelum ada peringkat

- Tecnica 100-140Dokumen12 halamanTecnica 100-140Georgel PalBelum ada peringkat

- 20NC60VD STMicroelectronicsDokumen11 halaman20NC60VD STMicroelectronicscristianBelum ada peringkat

- MARCUS Transformers - DatasheetsDokumen30 halamanMARCUS Transformers - DatasheetsTGhareebBelum ada peringkat

- Bsimsoiv4.4 Mosfet Model Users' Manual: Bsim Group December 2010Dokumen128 halamanBsimsoiv4.4 Mosfet Model Users' Manual: Bsim Group December 2010Arun Dev Dhar DwivediBelum ada peringkat

- XMAX TechnologyDokumen22 halamanXMAX TechnologyVijay Krishna0% (1)

- MOSFET Power SpecificationsDokumen8 halamanMOSFET Power SpecificationsЛехаBelum ada peringkat

- Power Electronics: HistoryDokumen1 halamanPower Electronics: HistoryIrma SotoBelum ada peringkat

- System Information ReportDokumen37 halamanSystem Information ReportMurat KaBelum ada peringkat

- PSG College of Technology, Coimbatore - 641 004 Semester Examinations, SemesterDokumen4 halamanPSG College of Technology, Coimbatore - 641 004 Semester Examinations, SemestermahesBelum ada peringkat

- Digital Telephony and The Use of Multiplexing in ItDokumen9 halamanDigital Telephony and The Use of Multiplexing in ItSri LavanyaBelum ada peringkat

- ELM339 Infrared Remote Control: Description FeaturesDokumen4 halamanELM339 Infrared Remote Control: Description FeaturesYacine MARICHEBelum ada peringkat

- Introduction to Wireless Communication BasicsDokumen21 halamanIntroduction to Wireless Communication Basicsashokyadav7390% (2)

- Computer Archiecture 1 D3804a15Dokumen5 halamanComputer Archiecture 1 D3804a15Surendra Singh ChauhanBelum ada peringkat

- 7812CT MCCDokumen3 halaman7812CT MCCxablauBelum ada peringkat

- RS-232 Communications wiring DiagramDokumen1 halamanRS-232 Communications wiring DiagramwarwarBelum ada peringkat

- Error CodeDokumen411 halamanError CodeTRIQUERE100% (2)