An Ultra Low Power 5 - Phase Ring Oscillator Using Lector Technique

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

An Ultra Low Power 5 - Phase Ring Oscillator Using Lector Technique

Hak Cipta:

Format Tersedia

Volume 3, Issue 10, October – 2018 International Journal of Innovative Science and Research Technology

ISSN No:-2456-2165

An Ultra Low Power 5 – Phase Ring Oscillator using

Lector Technique

Suraj Singh Bhadouria1, Nikhil Saxena2

PG Scolar1, Assistant professor 2

Department of Electronics & Communication Engineering, ITM Gwalior

Abstract:- In this current article 5- stage ring oscillator communications, musical instruments etc. which are

designed with lector technique for reduction in leakage especially designed [3]. They can be made from the cascaded

power without increasing the propagation delay. a lector stages of inverter along with the LC tank circuits which

technique to used two LCT transistor in which one of p- depends over the frequency range which is essential and

type and another one is n-type at each stage of ring required. The main function of a conventional ring oscillator is

oscillator and LCT is manage by source of second LCT producing oscillations varying from MHz range of frequency

transistor. In this current article is simulate and compare oscillation can be changed by adding stages number to it.

the various parameter are power dissipation, frequency, Although the adding number of levels affects the oscillation

average power of 5- stage ring oscillator based CMOS as frequency as enhancing the number of levels increases the

well as CNT at 32nm transistor based technology with the circuit’s propagation delay [4]. The practical acceptance of the

help of lector technique then comparison CNT based addition of stages beyond 9 is negligible as the dissipation of

transistor better result display as compare to the CMOS the power is enhanced in the circuits and if the oscillations are

based transistor using SPICE simulation tools. being added in several hundreds of inverter stages then the

oscillations of the frequency obtained is low whose further

Keywords:- CMOS, carbon nano tube (CNT), lector, leakage application is impractical and its fabrication and designing is

power, leakage current. not possible [5]. The best future nano-electric circuit is

CNTFET circuit. This is the best and possible transistor for the

I. INTRODUCTION future purposes. The conventional technology of CMOS

approaches its physical limits which are fundamental whilst

From the former two decades the electronic industries the downscaling as reported by Moore’s law for the digital

have acquired an exceptional excellent growth. This rapid electronic is performed and done by CNTFET. In today’s

change in the market exists because of the quick and the rapid world as the significance and the consequence of the system-

advancement in the technologies which are integrated because on-chips is increased therefore for the verification of the

of the VLSI advent. In the current scenario the market has digital circuit performance, the only parameter to verify and

been captured via wireless devices being computers, GPS, cell check it should not only be the digital performance. CNTFET

phone, Wi-Fi, Bluetooth etc. these aforementioned devices are functions over transistor which is based on single carbon. This

compact and they also make the wireless data available to CNTFET was first introduced in 1998, since then there have

other devices. There are certain frequencies which are to be been disparate alterations and changes done in it and if

worked upon for the transmittance and the receiving of the counted or developed according to the Moore’s law each year

data [1]. There is a common circuit which is being used as a the transistor should be double [6].

key for the modern communication is VCO. In any of the RF

transceivers, CMOS VCO which is integrated completely II. LITERATURE REVIEW

exhibits a significant block. The main function of an oscillator

is generating an analog and periodic signal whose frequency is Mahani et.al (2017) reported a new fault tolerant delay

stable and predictable. The output frequency provides AC cell for ring oscillators. In the phased and delayed locked loop

waveform depends over the input voltage. A controllable and the clock data recovery, RO is considered as better crucial

frequency from a clock is generated by VCO. In this circuits blocks, if discovered at faults they should be stuck for harsh

to be used phase locked loop for the generation of clock VCO environments and shouldn’t be tolerated against SET (single

[2]. event transient). ). Hybrid tolerant fault topology to be design

of delay cell whose is dependent and based over the role of

Regarding the ring oscillators, there are several sensitivity of each transistor. The mixture of three and four

applications of oscillators which form the vital building blocks transistors redundancy forms hybrid tolerant fault topology.

in the circuits of RF and various mixed signals. The targeted The software used by them is Cadence; their simulation results

field of applications varies along with the frequency of exhibit the fault tolerant delay cell dissipation of 34.34 µW

oscillators. It ranges and varies from Hz to MHz. Like all power occupying the chip area of 127.2 µm2. This technology

those oscillators pursuing high frequencies are utilized in which was proposed by them exhibited decrease in the power

phase locked loops, cyclotrons etc and there are various consumption when compared to the current fault tolerant delay

oscillators pursuing low frequency are utilized in radio cells. Simultaneously, they depicted more reliability against

IJISRT18OC374 www.ijisrt.com 684

Volume 3, Issue 10, October – 2018 International Journal of Innovative Science and Research Technology

ISSN No:-2456-2165

single and multiple stuck faults along with SETs. If this input. The path resistance is increased to ground and therefore

proposed reliable delay cell was used in the ring oscillators, the leakage current is decreased. First net-listing to the gate

the acquired dissipation of power and the phase noise were level is converted to complex gate implementation in the given

about 249 µW and -96dBc/Hz respectively. Their higher CMOS circuit, after this the introduction of the LCTs take

reliability was to be acquired when they were compared to place to attain a circuit which is leakage controlled. The

non-redundant ring oscillators [9]. importance of LECTOR technique is that it efficiently works

in active as well as idle circuit state and when the results are

Wu et.al (2017) stated the design ring oscillator which compared they found that the leakage reduction was better in

was applied using a pseudo-CMOS inverter; this was realized LECTOR than other techniques. The limitations which were

by n type transistors. They compared 11 stages using the exhibited by several other existing methods regarding the

conventional as well as proposed ring oscillator but both of reduction of leakage were overcome by their proposed

them were fabricated by thin film metal oxide transistors method. The average leakage reduction found in their

comprising of the structure of etch stop layer. The results and experimental results were 79.4% in MCNC benchmarks

the investigations depicted the delay product of power more circuits [7].

than 50% by the proposed technology using the same supply

voltage value. Oscillation frequency is increased the III. RESEARCH METHODOLOGY

consumption of the power is reduced by 18% over the similar

oscillation frequency. At the supply voltage a full swing can In the family of oscillator, a ring oscillator circuit is a

be received by acme voltage using their proposed ring simple way of scheme to reducing power dissipation. Ring

oscillators [10]. oscillator also called the relaxation oscillator so that the old

number of inverter are connected in series connection and to

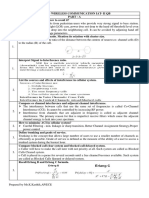

Dhakad et.al (2017) stated VCO design in which the obtain a natural oscillation as shown in a figure (1) CMOS

technique used was injection locking. The software used based transistor to be used for design 5 stage ring oscillator. In

through which all the simulations were performed was this circuit input of first inverter are connected to the output of

Virtuoso Cadence Analog Design Environment using the SCL final inverter. Therefore the name of this circuit is ring

180 nm CMOS process. The simulation results exhibited oscillator.

150% tuning range was achieved by VCO over the range of

508 MHz to 3.56 GHz with phase noise of -126 dBc/Hz at 1

MHz offset frequency. When the voltage supply was 1.8V

then the dissipation of the power of the circuit as an output

was obtained to be 110.4µW [11].

Balaji et.al (2016) reported a novel method for designing

low frequency CMOS ring oscillator producing the range of 1

Hz. The oscillator is designed in such a way that it comprises

of structure of CMOS thyristor which was designed with the

current mirror producing low frequency oscillations attaining

less space of device comparing to conventional N stage ring Fig 1:- 5- stage ring oscillator with CMOS technology

oscillators. To achieve oscillations to the desired aspect ratios

as well as the device parameters are designed with 90 nm Now design 5- stage ring oscillator with carbon nanotube

technology. For analyzing the oscillator performance they transistor based technology because CNT reduce leakage

investigated variation effect of voltage and temperature over power due to smaller and shorter channel length and CNT

frequency and the results of the simulations are exhibited [8]. made of rolded sheet of grapheme so that it is like a

cylindrical shape as showing in a figure (2).

Hanchate (2004) reported the enhancement of the

leakage current sub-threshold along with increase in power

dissipation to be statics which takes place due to the decrease

in the threshold voltage because of the scaling of the voltage

in the CMOS circuits. They proposed a LECTOR technique

for CMOS gates designing, as these gates without enhancing

the dynamic power consumption to be decreases leakage

current. In their technique they have introduced two LCT

transistors within the reach of the logic gates. In these logic

gates the terminal of the gate of each control transistor is not Fig 2:- five stage ring oscillator with CNT technology

controlled by itself they are controlled by the other sources.

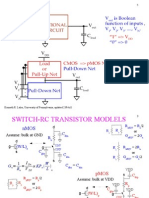

The arrangement is made in such a way that one of the LCT is Lector technique to apply in CMOS based 5 stage ring

always “near its cutoff voltage” regarding the combinations of oscillator as showing in a figure (3). In this circuit (a) is the

IJISRT18OC374 www.ijisrt.com 685

Volume 3, Issue 10, October – 2018 International Journal of Innovative Science and Research Technology

ISSN No:-2456-2165

input/output node, five inverter is connected in parallel at each lector CNT. The transient retaliation of lector CMOS are

inverter has made of one PMOS and other one NMOS captured in the figure (5).

transistor in that circuit.

Fig 5:- Transient retaliation of lector CMOS

Fig 3:- 5 stage ring oscillator design with CMOS technology

with lector technique Now transient retaliation of lector CNT is captured in the

figure (6). The transient retaliation of CMOS lector is

In the control box, Leakage controlled transistor (LCT) simulated using the spice tools with 32nm channel length at

is attached in series connection of each five inverter M2 1V and the transient

(PMOS) and M3 (NMOS) which are LCT. Leakage controlled

transistor are join among pull up and pull down network. Gate

terminal M2 is connect to the source of M3 and gate M3 is

connect to the source M2. Similarly design CNT transistor

based ring oscillator operates lector technique as showing in a

figure (4).

Fig 6:- Transient analysis of lector CNT

response of CMOS and CNT without lector technique

generates oscillation frequency to 335MHz to 365MHz with

110% truing where as the transient response of CMOS and

Fig 4:- CNT transistor based ring oscillator circuit applying CNT with lector technique is simulated using spice tools with

lector technique 32nm channel length at 1V then transient response of CMOS

and CNT with lector technique is generate more oscillation

IV. SIMULATION AND RESULT frequency to 335MHz to 365MHz with 160% turning and the

number of oscillation is more than the CMOS and CNT with

The proposed design is simulated using spice tool at

lector technique.

32nm. The length and width are taken as L=32nm and

W=32nm at 1V supply is applied. First of all 5-stage ring

oscillator is simulation with CMOS and CNT technology.

Then second rig oscillator simulates with lector CMOS and

Performance LECTOR LECTOR

parameter CMOS CNT CMOS CNT

Technology 32nm 32nm 32nm 32nm

Supply voltage 1V 1V 1V 1V

Frequency 300MHz 340MHz 335MHz 365MHz

Leakage power 29.01E-10W 5.579E-10W 1.517E-10W 6.085E-05W

Leakage current 29.01E-10A 5.579E-10A 1.517E-10A 6.085E-05A

Table 1:- comparison with CMOS, CNT, lector CMOS, and lector CNT with spice tools.

IJISRT18OC374 www.ijisrt.com 686

Volume 3, Issue 10, October – 2018 International Journal of Innovative Science and Research Technology

ISSN No:-2456-2165

The result are simulated of proposed circuit with application in 65 nm CMOS technology, IET Circuits

pervious work are shown in table (1). In this table determine Devices Syst., 2018, Vol. 12 Iss. 3, pp. 233-241.

the four parameter using spice tools with 32nm such as [10]. Jian-Dong Wu, Fan Zhan, Lei Zhou, Wei-Jing Wu ,

leakage power, leakage current, frequency, average power at Member, IEEE, Miao Xu, A Low-Power Ring Oscillator

1V. Using Pull-Up Control Scheme Integrated by Metal–

Oxide TFTs, IEEE Transactions On Electron Devices,

V. CONCLUSION Vol. 64, No. 12, December 2017.

[11]. Narendra Singh Dhakad, R. C. Gurjar, A Wide Tuning

A 5- stage ring oscillator was successfully designed and Range Voltage Controlled Ring Oscillator Using

simulated using spice tools at 32nm channel length. The main Injection Locking, Proceeding International conference

target of this paper is to be reduced the power dissipation and on Recent Innovations is Signal Processing and

leakage power. We create the previous paper work by Embedded Systems (RISE-2017) 27-29 October, 2017.

reducing voltage and using CNT technology and the result in

the table (1) presently comparison between CMOS and CNT.

According to the acquired simulation results we judge that the

proposed 5- stage ring oscillator with lector technique perform

better result in the term of power dissipation and leakage

current is reduce 23% at 1V. thus this lector technique to

control leakage power for the circuit designers.

REFERENCE

[1]. Ahmet Tekin, Mehmet R. Yuce, and Wentai Liu,

“Integrated VCO Design for MICS Transceivers”, IEEE

Custom Integrated Circuits Conference (CICC) 2006.

[2]. S.L. Jang, Y.H. Chuang, S.H. Lee, L.R. Chi, and C.F.

Lee, “An Integrated 5–2.5 GHz Direct-Injection Locked

Quadrature LC VCO”, IEEE Microwave And Wireless

Components Letters, vol. 17, no. 2, February 2007.

[3]. Ajay Kumar Mahato, “Ultra Low Frequency CMOS

Ring Oscillator Design,” Proceedings of RAECS UIET

Panjab University Chandigarh, 06 – 08 March, 978-1-

4799-2291-8/14,” IEEE2014.

[4]. Shruti Suman, Monika. Bharadwaj, and B.P. Singh, “An

Improved Performance Ring Oscllator Design,” IEEE

Computer Society, pp. 236-239, 2012.

[5]. Piyush Keshri, Biplab Deka, "CMOS Thyristor based

Low FrequencyRing Oscillator," Indian Institute of

Technology, Kanpur.

[6]. Chandramohan K, Nikhil Saxena, Sapna Navre, Sonal

Soni, Carbon Nanotube Transistor Based Novel Ring

Oscillator with Minimum Power Consumption at 32 nm

Technology Node , JoVDTT (2017) 51-54.

[7]. Narender Hanchate, LECTOR: A Technique for Leakage

Reduction in CMOS Circuits, IEEE Transactions On

Very Large Scale Integration (Vlsi) Systems, Vol. 12,

No. 2, February 2004.

[8]. Balaji Ramakrishna S., Shivananda Yalpi, Nithin Kumar

L, Ravindra H.B, Chaina Ram, Frequency CMOS Ring

Oscillator Using 90nm Technology, IEEE International

Conference On Recent Trends In Electronics

Information Communication Technology, May 20-21,

2016, India.

[9]. Sanaz Salem, Hamed Zandevakili, Ali Mahani , Mohsen

Saneei, Fault-tolerant delay cell for ring oscillator

IJISRT18OC374 www.ijisrt.com 687

Anda mungkin juga menyukai

- An Ultra-Low Power ISM-band Integer-N Frequency Synthesizer Dedicated To Implantable Medical MicrosystemsDokumen10 halamanAn Ultra-Low Power ISM-band Integer-N Frequency Synthesizer Dedicated To Implantable Medical MicrosystemsJakrawat BudBelum ada peringkat

- Article 140Dokumen6 halamanArticle 140Azizur RahmanBelum ada peringkat

- A Study On Active Inductor Based VCO To Implement PLL Frequency Synthesizer For Zigbee StandardDokumen6 halamanA Study On Active Inductor Based VCO To Implement PLL Frequency Synthesizer For Zigbee StandardAzizur RahmanBelum ada peringkat

- A Review Paper On CNTFET Technology and Circuit Designing Using CNTFETDokumen3 halamanA Review Paper On CNTFET Technology and Circuit Designing Using CNTFETGopi Reddy RanabothuBelum ada peringkat

- Ale Imran Trans 2012Dokumen10 halamanAle Imran Trans 2012Mohd YasirBelum ada peringkat

- Vco 3Dokumen6 halamanVco 3anon_701088587Belum ada peringkat

- Square Root Domain Filter Design and PerformanceDokumen13 halamanSquare Root Domain Filter Design and Performanceaakriti chhabraBelum ada peringkat

- A Low-Jitter Phase-Locked Loop Architecture For Clock Generation in Analog To Digital ConvertersDokumen4 halamanA Low-Jitter Phase-Locked Loop Architecture For Clock Generation in Analog To Digital ConvertersMadhavi PokuriBelum ada peringkat

- An Improved Performance Ring Oscillator Design: Abstract-This Paper Presents A New Technique To ImproveDokumen4 halamanAn Improved Performance Ring Oscillator Design: Abstract-This Paper Presents A New Technique To ImproveRam MBelum ada peringkat

- A Fully Integrated CMOS DCS-1800 Frequency Synthesizer: Jan Craninckx,, and Michel S. J. SteyaertDokumen12 halamanA Fully Integrated CMOS DCS-1800 Frequency Synthesizer: Jan Craninckx,, and Michel S. J. SteyaertgopipatBelum ada peringkat

- Synopsis VCO BDCoEDokumen9 halamanSynopsis VCO BDCoEraymar2kBelum ada peringkat

- Ijetr022661 PDFDokumen3 halamanIjetr022661 PDFerpublicationBelum ada peringkat

- Ring Oscillator ThesisDokumen8 halamanRing Oscillator Thesisafjvbpyki100% (2)

- An Integrator and Schmitt Trigger Based Voltage-ToDokumen6 halamanAn Integrator and Schmitt Trigger Based Voltage-ToCarlos Cárdenas BarbaBelum ada peringkat

- 33ssc07 VaucherDokumen12 halaman33ssc07 VaucherAlooomBelum ada peringkat

- Phase 2 ReportDokumen59 halamanPhase 2 ReportMurugeswariBelum ada peringkat

- Output Filter Design For Grid-Tied Cascaded Multi-Level Inverters Based On Novel Mathematical ExpressionsDokumen12 halamanOutput Filter Design For Grid-Tied Cascaded Multi-Level Inverters Based On Novel Mathematical ExpressionsHùng ĐặngBelum ada peringkat

- 3 Transceiver DesignDokumen6 halaman3 Transceiver DesignUtsav PopliBelum ada peringkat

- High-Frequency VCO Design Using CS AmplifiersDokumen10 halamanHigh-Frequency VCO Design Using CS Amplifiersanon_701088587Belum ada peringkat

- A 2.4 GHZ Fully Integrated LC Vco Design Using 130 NM Cmos TechnologyDokumen9 halamanA 2.4 GHZ Fully Integrated LC Vco Design Using 130 NM Cmos TechnologyAdam HernandezBelum ada peringkat

- Ultra-Low Voltage CMOS Ring Oscillator DesignDokumen10 halamanUltra-Low Voltage CMOS Ring Oscillator DesignMary Jane MalibiranBelum ada peringkat

- CKE - Volume 4 - Issue 1 - Pages 25-34Dokumen10 halamanCKE - Volume 4 - Issue 1 - Pages 25-34balasaravanan0408Belum ada peringkat

- Eken 2004Dokumen4 halamanEken 2004Yến VươngBelum ada peringkat

- Design and Performance Analysis of Low Phase Noise LC-voltage Controlled OscillatorDokumen9 halamanDesign and Performance Analysis of Low Phase Noise LC-voltage Controlled OscillatorTELKOMNIKABelum ada peringkat

- A 1.2 PM Cmos Implementation of Low-Power 900-Mhz Mobile Radio Frequency SynthesizerDokumen4 halamanA 1.2 PM Cmos Implementation of Low-Power 900-Mhz Mobile Radio Frequency SynthesizermanopthamBelum ada peringkat

- Low Power Ring Oscillator at 180nm CMOS Technology: Aman Shivhare M. K. GuptaDokumen4 halamanLow Power Ring Oscillator at 180nm CMOS Technology: Aman Shivhare M. K. GuptaRam MBelum ada peringkat

- Implementation of 2.4 GHZ Phase Locked Loop Using Sigma Delta ModulatorDokumen6 halamanImplementation of 2.4 GHZ Phase Locked Loop Using Sigma Delta ModulatorInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- AnnepuBaburao TSrinivasaRao 62Dokumen5 halamanAnnepuBaburao TSrinivasaRao 62Ahmed HussainBelum ada peringkat

- Analysis and Design of a 5-GHz Low Noise Phase Quadrature VCO Using Varactor DiodeDokumen5 halamanAnalysis and Design of a 5-GHz Low Noise Phase Quadrature VCO Using Varactor DiodenavinrkBelum ada peringkat

- Quadrature Vco ThesisDokumen6 halamanQuadrature Vco Thesisafknowudv100% (2)

- A 0.20 Text mm2 3 NW Signal Acquisition IC For Miniature Sensor Nodes in 65 NM CMOSDokumen9 halamanA 0.20 Text mm2 3 NW Signal Acquisition IC For Miniature Sensor Nodes in 65 NM CMOSzhaohhhengBelum ada peringkat

- Vibrating RF Mems: AbstractDokumen9 halamanVibrating RF Mems: AbstractSrini VasuluBelum ada peringkat

- Vision 2K11: "Trigate Transistors"Dokumen15 halamanVision 2K11: "Trigate Transistors"Amruta PatilBelum ada peringkat

- A CMOS Based Low Power Digitally Controlled OscillDokumen12 halamanA CMOS Based Low Power Digitally Controlled OscillDEEPAK PRAJAPATIBelum ada peringkat

- Question BankDokumen3 halamanQuestion BankREjosh BonifacioBelum ada peringkat

- Simulation Analysis of 10 Stage Delay Line Using CNT Transistor at 32nmDokumen4 halamanSimulation Analysis of 10 Stage Delay Line Using CNT Transistor at 32nmInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- IEEE - 2010 3 - EDL - A20Millimeter Wave20CPW20CMOS20On Chip20Bandpass20Filter20Using20Conductor BackedDokumen4 halamanIEEE - 2010 3 - EDL - A20Millimeter Wave20CPW20CMOS20On Chip20Bandpass20Filter20Using20Conductor BackedThierno Amadou Mouctar BaldeBelum ada peringkat

- A 5.7-Ghz Low-Noise AmplifierDokumen4 halamanA 5.7-Ghz Low-Noise AmplifierHoracio Dorantes ReyesBelum ada peringkat

- ISSCC2018 LO Gen DigestDokumen23 halamanISSCC2018 LO Gen DigestZyad IskandarBelum ada peringkat

- A_low-phase-noise_5-GHz_CMOS_quadrature_VCO_using_superharmonic_couplingDokumen7 halamanA_low-phase-noise_5-GHz_CMOS_quadrature_VCO_using_superharmonic_couplingSai GaganBelum ada peringkat

- Conf Rahma SmacdDokumen4 halamanConf Rahma SmacdRahma AloulouBelum ada peringkat

- 2013 IEEE TCAS-I 130nm CMOS Operational Schmitt Trigger R-to-F Converter For Nanogap-Based Nanosensors Read-OutDokumen14 halaman2013 IEEE TCAS-I 130nm CMOS Operational Schmitt Trigger R-to-F Converter For Nanogap-Based Nanosensors Read-OutMuhammad Sohail Asst. ProfessorBelum ada peringkat

- Nguyen 1998Dokumen13 halamanNguyen 1998joslinBelum ada peringkat

- High Order Programmable and Tunable Analog Filter ICDokumen16 halamanHigh Order Programmable and Tunable Analog Filter ICRahil JainBelum ada peringkat

- Wireless Communication IAT- II QB: Cell Dragging, Co-Channel Reuse Ratio & Signal InterferenceDokumen12 halamanWireless Communication IAT- II QB: Cell Dragging, Co-Channel Reuse Ratio & Signal InterferencekkarthikecBelum ada peringkat

- Amplifier DesignDokumen9 halamanAmplifier Designian neymarBelum ada peringkat

- Tunable Ferroelectric Microwave Bandpass Filters Optimised For System-Level IntegrationDokumen8 halamanTunable Ferroelectric Microwave Bandpass Filters Optimised For System-Level IntegrationyarkinyigitBelum ada peringkat

- A True Single-Phase Clocked Flip-Flop With Leakage Current CompensationDokumen6 halamanA True Single-Phase Clocked Flip-Flop With Leakage Current CompensationRao MallikarjunBelum ada peringkat

- A New Subthreshold Current-Mode Four Quadrant MultiplierDokumen6 halamanA New Subthreshold Current-Mode Four Quadrant MultiplierEditor IJRITCCBelum ada peringkat

- A Low Phase Noise Voltage Controlled Ring Oscillator Using Subharmonic Injection Locking Mechanism in 90nm CMOS ProcessDokumen7 halamanA Low Phase Noise Voltage Controlled Ring Oscillator Using Subharmonic Injection Locking Mechanism in 90nm CMOS ProcessManoj BoraBelum ada peringkat

- Analysis_of_Conventional_CMOS_and_FinFET_based_6-TDokumen7 halamanAnalysis_of_Conventional_CMOS_and_FinFET_based_6-Tswetha sillveriBelum ada peringkat

- A 30-Ghz Power-Efficient PLL Frequency Synthesizer For 60-Ghz ApplicationsDokumen11 halamanA 30-Ghz Power-Efficient PLL Frequency Synthesizer For 60-Ghz Applicationsmohan sardarBelum ada peringkat

- IJEDR1701118Dokumen7 halamanIJEDR1701118kesavanBelum ada peringkat

- FinalDokumen21 halamanFinalYAZHINI CHOLAMUTHUBelum ada peringkat

- 30-100-Ghz Inductors and Transformers For Millimeter-Wave (Bi) Cmos Integrated CircuitsDokumen11 halaman30-100-Ghz Inductors and Transformers For Millimeter-Wave (Bi) Cmos Integrated CircuitsmohamedBelum ada peringkat

- Analysis of AC Gain Using CNTFETDokumen5 halamanAnalysis of AC Gain Using CNTFETAkshay PatharkarBelum ada peringkat

- Leakage Reduction Using Self-Controlled Leakage TransistorsDokumen6 halamanLeakage Reduction Using Self-Controlled Leakage TransistorsAkBelum ada peringkat

- Signal Integrity: From High-Speed to Radiofrequency ApplicationsDari EverandSignal Integrity: From High-Speed to Radiofrequency ApplicationsBelum ada peringkat

- Forensic Evidence Management Using Blockchain TechnologyDokumen6 halamanForensic Evidence Management Using Blockchain TechnologyInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Food habits and food inflation in the US and India; An experience in Covid-19 pandemicDokumen3 halamanFood habits and food inflation in the US and India; An experience in Covid-19 pandemicInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Severe Residual Pulmonary Stenosis after Surgical Repair of Tetralogy of Fallot: What’s Our Next Strategy?Dokumen11 halamanSevere Residual Pulmonary Stenosis after Surgical Repair of Tetralogy of Fallot: What’s Our Next Strategy?International Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Late Presentation of Pulmonary Hypertension Crisis Concurrent with Atrial Arrhythmia after Atrial Septal Defect Device ClosureDokumen12 halamanLate Presentation of Pulmonary Hypertension Crisis Concurrent with Atrial Arrhythmia after Atrial Septal Defect Device ClosureInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Databricks- Data Intelligence Platform for Advanced Data ArchitectureDokumen5 halamanDatabricks- Data Intelligence Platform for Advanced Data ArchitectureInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Design and Development of Controller for Electric VehicleDokumen4 halamanDesign and Development of Controller for Electric VehicleInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- The Experiences of Non-PE Teachers in Teaching First Aid and Emergency Response: A Phenomenological StudyDokumen89 halamanThe Experiences of Non-PE Teachers in Teaching First Aid and Emergency Response: A Phenomenological StudyInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Scrolls, Likes, and Filters: The New Age Factor Causing Body Image IssuesDokumen6 halamanScrolls, Likes, and Filters: The New Age Factor Causing Body Image IssuesInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- The Students’ Assessment of Family Influences on their Academic MotivationDokumen8 halamanThe Students’ Assessment of Family Influences on their Academic MotivationInternational Journal of Innovative Science and Research Technology100% (1)

- Design and Implementation of Homemade Food Delivery Mobile Application Using Flutter-FlowDokumen7 halamanDesign and Implementation of Homemade Food Delivery Mobile Application Using Flutter-FlowInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Targeted Drug Delivery through the Synthesis of Magnetite Nanoparticle by Co-Precipitation Method and Creating a Silica Coating on itDokumen6 halamanTargeted Drug Delivery through the Synthesis of Magnetite Nanoparticle by Co-Precipitation Method and Creating a Silica Coating on itInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Anxiety, Stress and Depression in Overseas Medical Students and its Associated Factors: A Descriptive Cross-Sectional Study at Jalalabad State University, Jalalabad, KyrgyzstanDokumen7 halamanAnxiety, Stress and Depression in Overseas Medical Students and its Associated Factors: A Descriptive Cross-Sectional Study at Jalalabad State University, Jalalabad, KyrgyzstanInternational Journal of Innovative Science and Research Technology90% (10)

- Blockchain-Enabled Security Solutions for Medical Device Integrity and Provenance in Cloud EnvironmentsDokumen13 halamanBlockchain-Enabled Security Solutions for Medical Device Integrity and Provenance in Cloud EnvironmentsInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Quality By Plan Approach-To Explanatory Strategy ApprovalDokumen4 halamanQuality By Plan Approach-To Explanatory Strategy ApprovalInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Enhancing Biometric Attendance Systems for Educational InstitutionsDokumen7 halamanEnhancing Biometric Attendance Systems for Educational InstitutionsInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Investigating the Impact of the Central Agricultural Research Institute's (CARI) Agricultural Extension Services on the Productivity and Livelihoods of Farmers in Bong County, Liberia, from 2013 to 2017Dokumen12 halamanInvestigating the Impact of the Central Agricultural Research Institute's (CARI) Agricultural Extension Services on the Productivity and Livelihoods of Farmers in Bong County, Liberia, from 2013 to 2017International Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Optimizing Sound Quality and Immersion of a Proposed Cinema in Victoria Island, NigeriaDokumen4 halamanOptimizing Sound Quality and Immersion of a Proposed Cinema in Victoria Island, NigeriaInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- A Review on Process Parameter Optimization in Material Extrusion Additive Manufacturing using ThermoplasticDokumen4 halamanA Review on Process Parameter Optimization in Material Extrusion Additive Manufacturing using ThermoplasticInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Comparison of Lateral Cephalograms with Photographs for Assessing Anterior Malar Prominence in Maharashtrian PopulationDokumen8 halamanComparison of Lateral Cephalograms with Photographs for Assessing Anterior Malar Prominence in Maharashtrian PopulationInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Administration Consultancy Administrations, a Survival Methodology for Little and Medium Undertakings (SMEs): The Thailand InvolvementDokumen4 halamanAdministration Consultancy Administrations, a Survival Methodology for Little and Medium Undertakings (SMEs): The Thailand InvolvementInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Development of a Local Government Service Delivery Framework in Zambia: A Case of the Lusaka City Council, Ndola City Council and Kafue Town Council Roads and Storm Drain DepartmentDokumen13 halamanDevelopment of a Local Government Service Delivery Framework in Zambia: A Case of the Lusaka City Council, Ndola City Council and Kafue Town Council Roads and Storm Drain DepartmentInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Digital Pathways to Empowerment: Unraveling Women's Journeys in Atmanirbhar Bharat through ICT - A Qualitative ExplorationDokumen7 halamanDigital Pathways to Empowerment: Unraveling Women's Journeys in Atmanirbhar Bharat through ICT - A Qualitative ExplorationInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Post-Treatment Effects of Multiple Sclerosis (MS) on the Executive and Memory Functions ofCommercial Pilots in the UAEDokumen7 halamanPost-Treatment Effects of Multiple Sclerosis (MS) on the Executive and Memory Functions ofCommercial Pilots in the UAEInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Gardening Business System Using CNN – With Plant Recognition FeatureDokumen4 halamanGardening Business System Using CNN – With Plant Recognition FeatureInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Analysis of Risk Factors Affecting Road Work Construction Failure in Sigi DistrictDokumen11 halamanAnalysis of Risk Factors Affecting Road Work Construction Failure in Sigi DistrictInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Antibacterial Herbal Mouthwash Formulation and Evaluation Against Oral DisordersDokumen10 halamanAntibacterial Herbal Mouthwash Formulation and Evaluation Against Oral DisordersInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Examining the Role of Work-Life Balance Programs in Reducing Burnout among Healthcare Workers: A Case Study of C.B. Dunbar Hospital and the Baptist Clinic in Gbarnga City, Bong County, LiberiaDokumen10 halamanExamining the Role of Work-Life Balance Programs in Reducing Burnout among Healthcare Workers: A Case Study of C.B. Dunbar Hospital and the Baptist Clinic in Gbarnga City, Bong County, LiberiaInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Chemical Farming, Emerging Issues of Chemical FarmingDokumen7 halamanChemical Farming, Emerging Issues of Chemical FarmingInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Work-Life Balance: Women with at Least One Sick or Disabled ChildDokumen10 halamanWork-Life Balance: Women with at Least One Sick or Disabled ChildInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- Harnessing Deep Learning Methods for Detecting Different Retinal Diseases: A Multi-Categorical Classification MethodologyDokumen11 halamanHarnessing Deep Learning Methods for Detecting Different Retinal Diseases: A Multi-Categorical Classification MethodologyInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- UMC 0.18 um Mixed-Mode and RFCMOS 1.8 V/3.3 V Triple-Well Metal Metal Capacitor Process SPICE ModelDokumen10 halamanUMC 0.18 um Mixed-Mode and RFCMOS 1.8 V/3.3 V Triple-Well Metal Metal Capacitor Process SPICE ModelJoseBelum ada peringkat

- Vlsi Unit IIDokumen57 halamanVlsi Unit IIBasava RajuBelum ada peringkat

- Module 3 NAND and NOR LogicDokumen19 halamanModule 3 NAND and NOR LogicleevasusanBelum ada peringkat

- 1 Existence and Uniqueness of Solutions To Differential EquationsDokumen22 halaman1 Existence and Uniqueness of Solutions To Differential EquationsBella ZionBelum ada peringkat

- Characterization of TTLDokumen15 halamanCharacterization of TTLYellasiri SureshBelum ada peringkat

- Stick Diagram & Lambda Based Design RulesDokumen21 halamanStick Diagram & Lambda Based Design Rulesbaraniinst6875100% (1)

- Ee321 Chap01 ReviewDokumen60 halamanEe321 Chap01 ReviewMohamed Ouail CHARAOUIBelum ada peringkat

- Vlsi ManualDokumen62 halamanVlsi ManualIniya IlakkiaBelum ada peringkat

- Sheet 5 PDFDokumen3 halamanSheet 5 PDFMajid HelmyBelum ada peringkat

- Creating An Inverter Layout Using L-EditDokumen9 halamanCreating An Inverter Layout Using L-Editrakheep123Belum ada peringkat

- Field-Effect (FET) Transistors: ECE60L Lecture Notes, Spring 2003Dokumen16 halamanField-Effect (FET) Transistors: ECE60L Lecture Notes, Spring 2003harshBelum ada peringkat

- Microelectronics Lab ReportsDokumen75 halamanMicroelectronics Lab ReportsAmArbir SinghBelum ada peringkat

- DICD Multiple Choice Questions UNIT-1Dokumen5 halamanDICD Multiple Choice Questions UNIT-1TARUN PRASADBelum ada peringkat

- RTL Verilog Navabi PDFDokumen294 halamanRTL Verilog Navabi PDFSiva chowdaryBelum ada peringkat

- ICT Exp 1 - CMOS Inverter Layout & SimulationDokumen2 halamanICT Exp 1 - CMOS Inverter Layout & SimulationShameem ShaikBelum ada peringkat

- Transistor Switching ModelsDokumen56 halamanTransistor Switching Modelspraritlamba25Belum ada peringkat

- CMOS Transmission Gate OperationDokumen15 halamanCMOS Transmission Gate OperationGaurav MehraBelum ada peringkat

- 16EC5704 Verilog HDLDokumen5 halaman16EC5704 Verilog HDLHema Sundar Batta0% (1)

- VLSI TutorialDokumen16 halamanVLSI Tutorialthanos_3333Belum ada peringkat

- Digital Experiment 2Dokumen12 halamanDigital Experiment 2Ravi Tej GunisettyBelum ada peringkat

- CMOS Logic Schematic and Layout LabDokumen2 halamanCMOS Logic Schematic and Layout LabSiam HasanBelum ada peringkat

- Dynamic Logic CircuitsDokumen61 halamanDynamic Logic Circuitsbirla_sBelum ada peringkat

- CMOS Inverter: Push-Pull ArrangementDokumen20 halamanCMOS Inverter: Push-Pull ArrangementsatanBelum ada peringkat

- Adobe Scan 27 Jan 2023Dokumen25 halamanAdobe Scan 27 Jan 2023Swastik BeheraBelum ada peringkat

- Design and Implementation of Sychronous 4-Bit Up Counter Using Cmos 90Nm TechnologyDokumen46 halamanDesign and Implementation of Sychronous 4-Bit Up Counter Using Cmos 90Nm TechnologyManojkumar KalyanapuBelum ada peringkat

- Low Power CMOS Logic DesignDokumen19 halamanLow Power CMOS Logic DesignrakeshBelum ada peringkat

- Introduction To CMOS VLSI DesignDokumen30 halamanIntroduction To CMOS VLSI DesignAbdelrehim SirajBelum ada peringkat

- Digital CMOS Logic CircuitsDokumen84 halamanDigital CMOS Logic CircuitsPulkit AggarwalBelum ada peringkat

- Westeweb FM PDFDokumen67 halamanWesteweb FM PDFhellboytonmoyBelum ada peringkat

- VLSI Lab Report Lab Report On 3-Input NOR Gate (DRC and LVS Check)Dokumen11 halamanVLSI Lab Report Lab Report On 3-Input NOR Gate (DRC and LVS Check)SanjidaBelum ada peringkat