Design and Implementation of Serial Peripheral Interface Protocol Using Verilog HDL

Diunggah oleh

Kartikey SinghJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Design and Implementation of Serial Peripheral Interface Protocol Using Verilog HDL

Diunggah oleh

Kartikey SinghHak Cipta:

Format Tersedia

© 2015 IJEDR | Volume 3, Issue 3 | ISSN: 2321-9939

Design and Implementation of Serial Peripheral

Interface Protocol Using Verilog HDL

Fareha Naqvi 1

1

Student

Department of Electronics and Communication Engineering,

Alfalah School of Engineering & Technology,

Maharishi Dayanand University, Rohtak, Haryana, India

________________________________________________________________________________________________________

Abstract - The objective of this paper is the design and implementation of SPI (serial peripheral interface) master and

slave using verilog HDL. The SPI (serial peripheral interface) is a type of serial communication protocol that transfers

synchronous serial data in full duplex mode. There are two modes of communications in SPI viz., master and slave. While

the master device generates serial clock, the slave devices are allowed with individual slave select lines and the whole

design is simulated and synthesized with Xilinx ISE design suite 13.3.1

Keywords - SPI (serial peripheral interface), Verilog HDL.

________________________________________________________________________________________________________

I. INTRODUCTION

Serial to Peripheral Interface (SPI) is a hardware/firmware communications protocol developed by Motorola and later adopted by

others in the industry. Sometimes SPI is also called a "four wire" serial bus.The Serial Peripheral Interface or SPI-bus is a simple

4-wire serial communications interface used by many microprocessor/microcontroller peripheral chips that enables the controllers

and peripheral devices to communicate with each other. Even though it is developed primarily for the communication between

host processor and peripherals, a connection of two processors via SPI is just as well possible. The SPI bus, which operates at full,

is a synchronous type data link setup with a Master / Slave interface . Both single-master and multi-master protocols are possible

in SPI. The SPI Bus is usually used only on the PCB. The SPI Bus was designed to transfer data between various IC chips, at very

high speeds

II. SERIAL PERIPHERAL INTERFACE DESIGN

The internal architecture of SPI mainly consists of two modules, master module and slave module as shown in figure 1. The SPI

module allows a full duplex, synchronous, serial communication between the MCU and peripheral devices [1]. The main parts of

the SPI are status, control and data registers, shifter logic, baud rate generator, master/slave control logic and port control logic.

Software can poll the SPI status flags or the SPI operation can be interrupt driven. The SPI module has a total of 4 external pins:

• Master out Slave in (MOSI) - Output data from the master to the inputs of the slaves.

• Master in Slave out (MISO) - Output data from a slave to the input of the master.

• Serial Clock (SCLK) - Clock driven by the master to slaves, used to synchronize the data bits.

• Slave Select (SS) - Select signal driven by the master to individual slaves, used to select the target slave [2].

Figure 1: SPI Block Diagram

The main element of the SPI system is the SPI Control Register and the SPI Data Register. The control word written into the

Control Register determines the mode in which the SPI shall be configured. The 8-bit data register in the master and the 8-bit data

register in the slave are linked by the MOSI and MISO pins to form a distributed 16-bit register. When a data transfer operation is

performed, this 16-bit register is serially shifted eight bit positions by the serial clock from the master. Consequently, data is

exchanged between the master and the slave. Data written to the master SPI Data Register becomes the output data for the slave,

and data read from the master SPI Data Register after a transfer operation is the input data from the slave. The SPI system

operates in two modes master and slave.

IJEDR1503092 International Journal of Engineering Development and Research (www.ijedr.org) 1

© 2015 IJEDR | Volume 3, Issue 3 | ISSN: 2321-9939

III. MASTER MODE OPERATION

The SPI operates in master mode when the MSTR control bit is set. The transmission begins by writing to the master SPI

Transmit Data Register. If the shift register is empty, the byte immediately transfers to the shift register. Once the byte is

transferred from the SPI transmit register to the shift register, the SPTE control bit is set indicating that another byte can be

written to the SPI transmit data register. In master mode, before transmission SS pin is connected to VDD if the single slave

module is used. Then the byte begins shifting out a bit at a time on the MOSI pin synchronized with the master serial clock. The

data transmission will continue for 8 clock cycles, transferring all 8-bits. The transmission ends when the whole byte is shifted out

of the master SPI shift register into the slave SPI shift register. The slave shift register is then automatically transferred to the

slave SPI receive data register if it is empty. The SPRF control bit is set indicating that the SPI receive register is full and waiting

to be read [3].

IV. SLAVE MODE OPERATION

The SPI operates in slave mode when the MSTR bit in SPI .In slave mode, SCK is the SPI clock input from the master, the

function of the serial data output pin (MISO) and serial data input pin (MOSI) is determined by the SPC0 bit and BIDIROE bit in

SPI Control Register 2. And the SS pin is the slave select input. Before a data transmission the SS pin is connected to ground if

the single slave module is used. Once the byte is transferred from the SPI transmit register to the shift register, the SPTE control

bit is set indicating that another byte can be written to the SPI transmit data register. The byte of data shifting a bit at time on the

MISO pin synchronized with the master serial clock. The master shift register is then automatically transferred to the master SPI

receive data register if it is empty. The SPRF control bit is set indicating that the SPI receive register is full and waiting to be read.

V. SPI DATA TRANSMISSION

SPI interface allows to transmit and receive data simultaneously on two lines (MOSI and MISO). Clock polarity (CPOL) and

clock phase (CPHA) are the main parameters that define a clock format to be used by the SPI bus. Depending on CPOL

parameter, SPI clock may be inverted or non-inverted. When clock polarity is set to 1, the idle state for SCLK is high [4].CPHA

parameter is used to shift the sampling phase. If CPHA=0 the data are sampled on the leading (first) clock edge. If CPHA=1 the

data are sampled on the trailing (second) clock edge, regardless of whether that clock edge is rising or falling.

Clock polarity = 0, Clock phase = 0

Figure 2: Clock polarity = 0, Clock phase = 0

The data must be available before the first clock signal rising. The clock idle state is zero. The data on MISO and MOSI lines

must be stable while the clock is high and can be changed when the clock is low. The data is captured on the clock's low-to-high

transition and propagated on high-to-low clock transition.

Clock polarity = 0, Clock phase = 1

Figure 3: Clock polarity = 0, Clock phase = 1

The first clock signal rising can be used to prepare the data. The clock idle state is zero. The data on MISO and MOSI lines must

be stable while the clock is low and can be changed when the clock is high. The data is captured on the clock's high-to-low

transition and propagated on low-to-high clock transition.

Clock polarity = 1, Clock phase = 0

IJEDR1503092 International Journal of Engineering Development and Research (www.ijedr.org) 2

© 2015 IJEDR | Volume 3, Issue 3 | ISSN: 2321-9939

Figure 4: Clock polarity = 1, Clock phase = 0

The data must be available before the first clock signal falling. The clock idle state is one. The data on MISO and MOSI lines

must be stable while the clock is low and can be changed when the clock is high. The data is captured on the clock's high-to-low

transition and propagated on low-to-high clock transition.

Clock polarity = 1, Clock phase = 1

Figure 5: Clock polarity = 1, Clock phase = 1

The first clock signal falling can be used to prepare the data. The clock idle state is one. The data on MISO and MOSI lines must

be stable while the clock is high and can be changed when the clock is low. The data is captured on the clock's low-to-high

transition and propagated on high-to-low clock transition.

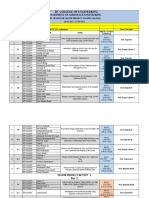

VI. SIMULATION AND RESULTS

The data transmission from master to slave and slave to master has been synthesized using the Xilinx ISE design

suite 13.3.1 and the simulation results are shown in figure respectively.

IJEDR1503092 International Journal of Engineering Development and Research (www.ijedr.org) 3

© 2015 IJEDR | Volume 3, Issue 3 | ISSN: 2321-9939

Figure 6: SPI RTL Schematic of Top Module

Figure 7: SPI Master to Slave Data Transmission

IJEDR1503092 International Journal of Engineering Development and Research (www.ijedr.org) 4

© 2015 IJEDR | Volume 3, Issue 3 | ISSN: 2321-9939

Figure7: SPI Slave to Master Data Transmission

VII. CONCLUSION

The SPI Master and Slave has been implemented using verilog HDL and Xilinx ISE 13.3.1 was used for simulation. The basis of

this paper is the focus on data transmission between master and slave modules. We have verified the data in slave device same as

the data in the master device and various possible cases of clock polarity and clock phase are verified. Further, we have also done

functional verification.

REFERENCES

[1] Motorola Inc., “SPI Block Guide V03.06,” February 2003

[2] Quartus II Handbook version 9.0 volume 5: Embedded Peripherals. Altera SPI core interval time core chapter in

volume 5 of the Quartus II.

[3] Digital DNA from Motorola, “SPI Tutorial introduction”.

[4] F.Leens, “An Introduction to I2C and SPI Protocols,”IEEE Instrumentation & Measurement Magazine, pp. 8-13, February

2009.

[5] A.K. Oudjida et al, “FPGA Implementation of I2C and SPI Protocols: A Comparative Study”. Proceedings of the 16th edition

of the IEEE International Conference on Electronics Circuits and Systems ICECS, pp. 507 -510, ISBN: 978-1-4244-5091-

6,December 13-16 2009, Yasmine Hammamet, Tunisia.

[6] Bhaskar. J, A Verilog HDL Primer, Publisher: Syndicate Publications.

IJEDR1503092 International Journal of Engineering Development and Research (www.ijedr.org) 5

Anda mungkin juga menyukai

- JETIRCD06042Dokumen6 halamanJETIRCD06042Ganesh JallaBelum ada peringkat

- nternational Journal of Computational Engineering Research(IJCER) is an intentional online Journal in English monthly publishing journal. This Journal publish original research work that contributes significantly to further the scientific knowledge in engineering and Technology.Dokumen6 halamannternational Journal of Computational Engineering Research(IJCER) is an intentional online Journal in English monthly publishing journal. This Journal publish original research work that contributes significantly to further the scientific knowledge in engineering and Technology.International Journal of computational Engineering research (IJCER)Belum ada peringkat

- IJEDR1704175Dokumen6 halamanIJEDR1704175Chand1891Belum ada peringkat

- UVM Methodology Based Functional Verification of SPI ProtocolDokumen9 halamanUVM Methodology Based Functional Verification of SPI ProtocolsatyendraBelum ada peringkat

- Serial Peripheral Interface (SPI)Dokumen5 halamanSerial Peripheral Interface (SPI)Benin JacobBelum ada peringkat

- Hello, and Welcome To This Presentation of The STM32 Serial Peripheral InterfaceDokumen31 halamanHello, and Welcome To This Presentation of The STM32 Serial Peripheral InterfacelinkskilBelum ada peringkat

- Application Note EnweiGuDokumen11 halamanApplication Note EnweiGupacoBelum ada peringkat

- Characteristics of Serial Peripheral Interfaces Timing For Optical MouseDokumen7 halamanCharacteristics of Serial Peripheral Interfaces Timing For Optical MouseSantosh MeenaBelum ada peringkat

- Welcome To International Journal of Engineering Research and Development (IJERD)Dokumen7 halamanWelcome To International Journal of Engineering Research and Development (IJERD)IJERDBelum ada peringkat

- Hello, and Welcome To This Presentation of The STM32 Serial Peripheral InterfaceDokumen27 halamanHello, and Welcome To This Presentation of The STM32 Serial Peripheral Interfacecansu100% (1)

- An Implementation of I2C Slave Interface Using Verilog HDL: JournalDokumen6 halamanAn Implementation of I2C Slave Interface Using Verilog HDL: Journalvisu100% (1)

- Design and Verification of Daisy Chain Serial Peripheral Interface Using System Verilog and Universal Verification MethodologyDokumen10 halamanDesign and Verification of Daisy Chain Serial Peripheral Interface Using System Verilog and Universal Verification MethodologyTELKOMNIKABelum ada peringkat

- SPI EmbeddedDokumen16 halamanSPI EmbeddedSrivatsanBelum ada peringkat

- An Implementation of I2C Slave Interface Using Verilog HDLDokumen6 halamanAn Implementation of I2C Slave Interface Using Verilog HDLIJMERBelum ada peringkat

- B0643042212Dokumen12 halamanB0643042212marvel homesBelum ada peringkat

- Mbed BK Ed2 CH 7Dokumen42 halamanMbed BK Ed2 CH 7Pedro Augusto PeresBelum ada peringkat

- MES MODULE 4 Embedded System ComponentsDokumen103 halamanMES MODULE 4 Embedded System Componentsdaniel007workBelum ada peringkat

- Spi ModuleDokumen13 halamanSpi ModuleMuhammadSaeedTahir100% (2)

- I2c Bus Contr ReportDokumen13 halamanI2c Bus Contr ReportSreeshmith Sreedar100% (2)

- Sdic 2marks (Q & A) (Unit 4)Dokumen3 halamanSdic 2marks (Q & A) (Unit 4)Ganapathy RamadossBelum ada peringkat

- Implementation of Spi Master CoreDokumen14 halamanImplementation of Spi Master CoreGanesh JallaBelum ada peringkat

- Register Dan Shif RegisterDokumen15 halamanRegister Dan Shif RegisterTsamarul HizbiBelum ada peringkat

- College of Electronics Technology Bani Walid: Presented By: Mohamed Awad Mohamed AbolobaidhDokumen10 halamanCollege of Electronics Technology Bani Walid: Presented By: Mohamed Awad Mohamed AbolobaidhMohammedAwadAlwarfleBelum ada peringkat

- Spi Final Project 21bee1161Dokumen11 halamanSpi Final Project 21bee1161Abhishek pathakBelum ada peringkat

- SpiDokumen21 halamanSpirockymaxdeemannBelum ada peringkat

- ProtocolsDokumen92 halamanProtocolsdeepakBelum ada peringkat

- SPI Implementation On FPGADokumen3 halamanSPI Implementation On FPGAshivgnitBelum ada peringkat

- Mbed Course Notes - Serial SpiDokumen24 halamanMbed Course Notes - Serial SpizaddlerBelum ada peringkat

- Snake Robot ReportDokumen30 halamanSnake Robot ReportAditya Vidolkar100% (1)

- Unit 2Dokumen27 halamanUnit 2studyexpress12Belum ada peringkat

- Design Alternatives For A 4-Bit Universal Shift Register Using Clock Pulse Sense LatchDokumen10 halamanDesign Alternatives For A 4-Bit Universal Shift Register Using Clock Pulse Sense Latchcreative nprintBelum ada peringkat

- Saha 2014Dokumen7 halamanSaha 2014AMIT VERMABelum ada peringkat

- SPI Final 2022Dokumen47 halamanSPI Final 2022Utsav VedantBelum ada peringkat

- I2CDokumen6 halamanI2CGovinda RaoBelum ada peringkat

- Design of A Micro-Uart For Soc ApplicationDokumen12 halamanDesign of A Micro-Uart For Soc ApplicationUtkarsh Jain100% (1)

- Introduction To Spi CommunicationDokumen5 halamanIntroduction To Spi Communicationjoyal jose100% (2)

- Basics of The Communication ProtocolDokumen19 halamanBasics of The Communication ProtocolNEETHU PRAKASHBelum ada peringkat

- Design and Implementation of I2c Master Controller On FPGA Using VHDLDokumen5 halamanDesign and Implementation of I2c Master Controller On FPGA Using VHDLDorothy FletcherBelum ada peringkat

- 10 2348 Ijset06150601Dokumen3 halaman10 2348 Ijset06150601satyendraBelum ada peringkat

- Design of I2C Protocol: March 2019Dokumen5 halamanDesign of I2C Protocol: March 201921CS185 VISHAL.MBelum ada peringkat

- Serial Communication Protocols and RTCDokumen15 halamanSerial Communication Protocols and RTCMukesh PatidarBelum ada peringkat

- Ijert Ijert: Implementation of Interleaving Switch Based Architecture For System On ChipDokumen7 halamanIjert Ijert: Implementation of Interleaving Switch Based Architecture For System On ChipAkhila ReddyBelum ada peringkat

- Registration For Wiki Conference India 2011Dokumen21 halamanRegistration For Wiki Conference India 2011Nitya SiddagangappaBelum ada peringkat

- Using The SPI Module On 8-Bit PIC® MicrocontrollersDokumen23 halamanUsing The SPI Module On 8-Bit PIC® MicrocontrollersChristian GomezBelum ada peringkat

- Saha 2014Dokumen6 halamanSaha 2014PoojaBelum ada peringkat

- EE325: Microprocessors and Microcontrollers: Serial Peripheral Interface: SPIDokumen13 halamanEE325: Microprocessors and Microcontrollers: Serial Peripheral Interface: SPILedeheBelum ada peringkat

- CENG507 Fall2020 Chap4Dokumen40 halamanCENG507 Fall2020 Chap4Anonymous phisherBelum ada peringkat

- Serial Peripheral Interface Bus - Wikipedia, The Free EncyclopediaDokumen11 halamanSerial Peripheral Interface Bus - Wikipedia, The Free EncyclopediaManit100% (1)

- 2 - Design Task 2012Dokumen5 halaman2 - Design Task 2012ᙢᗅᗁᕢᖱᖺᕦᐺᕱᘘ ᐻᓾᖱᖻᕠᔚᖺᗗᘘᖽᐸᗋᖇBelum ada peringkat

- 8 Design of BISTDokumen54 halaman8 Design of BISTvsangvai26Belum ada peringkat

- Unit - 4: 4.1. Serial Data Communication - BasicsDokumen16 halamanUnit - 4: 4.1. Serial Data Communication - BasicsRAJU VALLEPUBelum ada peringkat

- Speed Detector For HighwaysDokumen29 halamanSpeed Detector For HighwaysShama MahinBelum ada peringkat

- Basics of The Communication ProtocolDokumen19 halamanBasics of The Communication ProtocolNEETHU PRAKASH100% (1)

- cc2500 ConDokumen25 halamancc2500 Conprasad357Belum ada peringkat

- Introduction I2c and SPIDokumen14 halamanIntroduction I2c and SPIHaris Jeelani100% (1)

- Ch17 Spi Protocol and Max7221 Display InterfacingDokumen51 halamanCh17 Spi Protocol and Max7221 Display InterfacingSimple knowledgeBelum ada peringkat

- Serial Peripheral InterfaceDokumen5 halamanSerial Peripheral InterfaceabhinavbitBelum ada peringkat

- Design and Implementation of A 32 Bit RISC Processor On Xilinx FPGADokumen6 halamanDesign and Implementation of A 32 Bit RISC Processor On Xilinx FPGAKartikey SinghBelum ada peringkat

- Assignment-1: Professional Ethics and Human ValuesDokumen18 halamanAssignment-1: Professional Ethics and Human ValuesKartikey SinghBelum ada peringkat

- NLP Sentiment AnalysisDokumen7 halamanNLP Sentiment AnalysisKartikey SinghBelum ada peringkat

- Lecture 6: Combinational AtpgDokumen28 halamanLecture 6: Combinational AtpgKartikey SinghBelum ada peringkat

- Elint Labz - Magnetic Door Sensor Plug ManualDokumen10 halamanElint Labz - Magnetic Door Sensor Plug ManualKartikey SinghBelum ada peringkat

- Elint Labz - Bi-Color LED Plug ManualDokumen10 halamanElint Labz - Bi-Color LED Plug ManualKartikey SinghBelum ada peringkat

- 05 x05 Standard Costing & Variance AnalysisDokumen27 halaman05 x05 Standard Costing & Variance AnalysisMary April MasbangBelum ada peringkat

- Dynamics of Machinery PDFDokumen18 halamanDynamics of Machinery PDFThomas VictorBelum ada peringkat

- Review1 ScheduleDokumen3 halamanReview1 Schedulejayasuryam.ae18Belum ada peringkat

- 1.technical Specifications (Piling)Dokumen15 halaman1.technical Specifications (Piling)Kunal Panchal100% (2)

- ISBN Safe Work Method Statements 2022 03Dokumen8 halamanISBN Safe Work Method Statements 2022 03Tamo Kim ChowBelum ada peringkat

- Psychological Contract Rousseau PDFDokumen9 halamanPsychological Contract Rousseau PDFSandy KhanBelum ada peringkat

- MGMT Audit Report WritingDokumen28 halamanMGMT Audit Report WritingAndrei IulianBelum ada peringkat

- Golf Croquet Refereeing Manual - Croquet AustraliaDokumen78 halamanGolf Croquet Refereeing Manual - Croquet AustraliaSenorSushi100% (1)

- Gods Omnipresence in The World On Possible MeaninDokumen20 halamanGods Omnipresence in The World On Possible MeaninJoan Amanci Casas MuñozBelum ada peringkat

- Article An Incident and Injury Free Culture Changing The Face of Project Operations Terra117 2Dokumen6 halamanArticle An Incident and Injury Free Culture Changing The Face of Project Operations Terra117 2nguyenthanhtuan_ecoBelum ada peringkat

- Checklist & Guideline ISO 22000Dokumen14 halamanChecklist & Guideline ISO 22000Documentos Tecnicos75% (4)

- IEC ShipsDokumen6 halamanIEC ShipsdimitaringBelum ada peringkat

- Huawei R4815N1 DatasheetDokumen2 halamanHuawei R4815N1 DatasheetBysBelum ada peringkat

- Financial Accounting 2 SummaryDokumen10 halamanFinancial Accounting 2 SummaryChoong Xin WeiBelum ada peringkat

- 13 Adsorption of Congo Red A Basic Dye by ZnFe-CO3Dokumen10 halaman13 Adsorption of Congo Red A Basic Dye by ZnFe-CO3Jorellie PetalverBelum ada peringkat

- Blue Prism Data Sheet - Provisioning A Blue Prism Database ServerDokumen5 halamanBlue Prism Data Sheet - Provisioning A Blue Prism Database Serverreddy_vemula_praveenBelum ada peringkat

- Laboratory Manual (CIV 210) Engineering Surveying (2018-19) (For Private Circulation Only)Dokumen76 halamanLaboratory Manual (CIV 210) Engineering Surveying (2018-19) (For Private Circulation Only)gyanendraBelum ada peringkat

- Read While Being Blind.. Braille's Alphabet: Be Aware and Active !Dokumen3 halamanRead While Being Blind.. Braille's Alphabet: Be Aware and Active !bitermanBelum ada peringkat

- Outdoor Air Pollution: Sources, Health Effects and SolutionsDokumen20 halamanOutdoor Air Pollution: Sources, Health Effects and SolutionsCamelia RadulescuBelum ada peringkat

- Famous Russian PianoDokumen10 halamanFamous Russian PianoClara-Schumann-198550% (2)

- MRBR ATR 72 Rev18Dokumen424 halamanMRBR ATR 72 Rev18Juan Forero OrtizBelum ada peringkat

- Appendix - Pcmc2Dokumen8 halamanAppendix - Pcmc2Siva PBelum ada peringkat

- Online Extra: "Economists Suffer From Physics Envy"Dokumen2 halamanOnline Extra: "Economists Suffer From Physics Envy"Bisto MasiloBelum ada peringkat

- Technical Bulletin LXL: No. Subject Release DateDokumen8 halamanTechnical Bulletin LXL: No. Subject Release DateTrunggana AbdulBelum ada peringkat

- DP 2 Human IngenuityDokumen8 halamanDP 2 Human Ingenuityamacodoudiouf02Belum ada peringkat

- 74HC00D 74HC00D 74HC00D 74HC00D: CMOS Digital Integrated Circuits Silicon MonolithicDokumen8 halaman74HC00D 74HC00D 74HC00D 74HC00D: CMOS Digital Integrated Circuits Silicon MonolithicAssistec TecBelum ada peringkat

- Powerpoint Speaker NotesDokumen4 halamanPowerpoint Speaker Notesapi-273554555Belum ada peringkat

- Floating Oil Skimmer Design Using Rotary Disc MethDokumen9 halamanFloating Oil Skimmer Design Using Rotary Disc MethAhmad YaniBelum ada peringkat

- TIMO Final 2020-2021 P3Dokumen5 halamanTIMO Final 2020-2021 P3An Nguyen100% (2)

- Unit 7: Anthropology: Q2e Listening & Speaking 4: Audio ScriptDokumen6 halamanUnit 7: Anthropology: Q2e Listening & Speaking 4: Audio ScriptĐại học Bạc Liêu Truyền thông100% (1)