Introdução A Projeto de Circuitos Integrados Digitais

Diunggah oleh

João Victor0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

62 tayangan3 halamanDescrever o fluxo de projetos de circuitos integrados digitais, proporcionando ao aluno

obter conhecimentos introdutórios de três das quatros principais etapas de

desenvolvimento de um circuito integrado composto por elementos digitais.

Judul Asli

Introdução a Projeto de Circuitos Integrados Digitais

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniDescrever o fluxo de projetos de circuitos integrados digitais, proporcionando ao aluno

obter conhecimentos introdutórios de três das quatros principais etapas de

desenvolvimento de um circuito integrado composto por elementos digitais.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

62 tayangan3 halamanIntrodução A Projeto de Circuitos Integrados Digitais

Diunggah oleh

João VictorDescrever o fluxo de projetos de circuitos integrados digitais, proporcionando ao aluno

obter conhecimentos introdutórios de três das quatros principais etapas de

desenvolvimento de um circuito integrado composto por elementos digitais.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 3

Introdução ao Projeto de Circuitos Integrados Digitais

Coordenador do Centro de Treinamento: Prof. Dr. João Antonio Martino

Objetivo:

Descrever o fluxo de projetos de circuitos integrados digitais, proporcionando ao aluno

obter conhecimentos introdutórios de três das quatros principais etapas de

desenvolvimento de um circuito integrado composto por elementos digitais.

Dados do Curso:

Nome: Introdução a Projeto de Circuitos Integrados Digitais

Carga horária: 32 horas, realizado de terça-feira à sexta-feira (10/07 a 13/07)

Ementa:

Introdução a descrição e simulação de hardware usando a linguagem Verilog

Introdução a extração de cobertura de código

Introdução a síntese lógica

Introdução a prototipação em FPGA

Professores Envolvidos:

• Luciana Montali (Luciana.montali@nscad.org.br)

• Ruy Costa (ruy.costa@nscad.org.br)

• Vinicius Martins (vinicius.martins@nscad.org.br)

Atividades Experimentais:

• Desenvolvimento de um RTL sintetizável utilizando conceitos de máquinas de

estado e de descrição de hardware. (Compiladores de Verilog).

• Instrumentação da descrição hardware para coletado de cobertura de código.

Extração de cobertura de código (Incisive Simulator e Incisive Metrics

Coverage).

• Síntese Lógica Inicial utilizando a tecnologia da XFAB 180 nanômetros (Basic

Static Timing Analysis – BSTA, RTL Compiler e Conformal Equivalence

Checking).

• Prototipação do relógio em FPGA.

Cronograma

Dia 1 – 10/07 (terça-feira)

• Manhã (08:30 às 12:30)

o Introdução / Abertura

Instrutor: Professor Dr. João Antonio Martino

o Fluxo de criação de um circuito integrado digital.

Instrutor: Shiroma Montali

• Tarde (14:00 às 18:00)

o Introdução a Verilog (princípios básicos, verilog como descrição de hardware).

Compilar, Elaborar e Simular (em único passo) Verilog

Instrutores: Ruy Costa e Vinicius Martins

Atividades:

§ Laboratório 1: Design e validação das portas AND e OR

§ Laboratório 2: Design e validação de um Multiplexador

Dia 2 - 11/07 (quarta-feira)

• Manhã (08:30 às 12:30)

o Introdução a Verilog (princípios básicos, verilog como descrição de hardware).

Compilar, Elaborar e Simular (em único passo) Verilog

Instrutores: Ruy Costa e Vinicius Martins

Atividades:

§ Laboratório 3: Design e validação de um Contador

§ Laboratório 4: Design e validação de um Decodificador para BCD

• Tarde (14:00 às 18:00)

o Laboratório de Verilog (Verilog + Testbench)

Instrutores: Vinicius Martins e Ruy Costa

Atividades:

§ Laboratório 1: Design do Black Jack

§ Laboratório 2: Validação do Black Jack (Testbench)

Dia 3 – 12/07 (quinta-feira)

• Manhã (08:30 às 12:30)

o Instrumentação e extração de cobertura de código para o Black Jack.

Instrutores: Vinicius Martins e Ruy Costa

Atividades:

§ Laboratório 1: Instrumentação do Design.

§ Laboratório 2: Extração e análise da cobertura de código.

§ Laboratório 3: Aperfeiçoar o testbench para obter uma cobertura de

código mais elevada.

• Tarde (14:00 às 18:00)

o Introdução à síntese lógica. Síntese lógica básica do BlackJack.

Instrutores: Shiroma Montali e Vinicius Martins

Atividades:

§ Laboratório 1: Introdução ao fluxo de síntese lógica

§ Laboratório 2: Utilização dos três tipos de síntese lógica: Genérico,

Mapeado e Incremental.

§ Laboratório 3: Criação das condições de contorno e introdução a

comparação de equivalência lógica.

Dia 4 – 13/07 (sexta-feira)

• Manhã (08:30 às 12:30)

o Introdução a FPGA. Conceitos, evolução e prototipação.

Instrutores: Shiroma Montali e Vinicius Martins

Atividades:

§ Laboratório 1: Prototipação em FPGA de um relógio desenvolvido em

Verilog.

• Tarde (14:00 às 18:00)

o Introdução ao Fluxo de Síntese Física

o Fechamento dos laboratórios. Revisão de todos os conceitos abordados no

curso.

Instrutores: Vinicius Martins e Ruy Costa

Anda mungkin juga menyukai

- Design Modelagem Ergonomica a-POCDokumen120 halamanDesign Modelagem Ergonomica a-POCAlessandra BilléBelum ada peringkat

- 1380 SurDokumen28 halaman1380 Surwilson silveiraBelum ada peringkat

- Artigo Sobre AudacesDokumen113 halamanArtigo Sobre AudacesGlenda MeloBelum ada peringkat

- Proporções entre lojas de rua e shoppingDokumen49 halamanProporções entre lojas de rua e shoppingPaulo Henrique100% (1)

- Uma Casa - para - A - Vida PDFDokumen74 halamanUma Casa - para - A - Vida PDFPedro Alvernaz100% (1)

- 31 Fornecedores OcultosDokumen32 halaman31 Fornecedores OcultosBruno Halfeld DutraBelum ada peringkat

- Ebook Design Thinking Aplicado Arquitetura e Engenharia v.2Dokumen14 halamanEbook Design Thinking Aplicado Arquitetura e Engenharia v.2Valéria Sales100% (2)

- Lista Precios Leds 16 Marzo Al 16 Abril 2023Dokumen21 halamanLista Precios Leds 16 Marzo Al 16 Abril 2023Rafael Guerrero100% (1)

- Relatorio 2 - Lab C2 - UFMG 2014/1Dokumen9 halamanRelatorio 2 - Lab C2 - UFMG 2014/1João VictorBelum ada peringkat

- Trabalho de Geografia - TransporteDokumen1 halamanTrabalho de Geografia - TransporteJoão VictorBelum ada peringkat

- Lição 02 - Ei, Táxi PDFDokumen5 halamanLição 02 - Ei, Táxi PDFTierry ConstantinoBelum ada peringkat

- Lição 02 - Ei, Táxi PDFDokumen5 halamanLição 02 - Ei, Táxi PDFTierry ConstantinoBelum ada peringkat

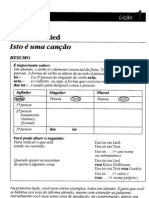

- Lição 01 - Isto É Uma Canção PDFDokumen2 halamanLição 01 - Isto É Uma Canção PDFTierry ConstantinoBelum ada peringkat

- Curso Fonte Chaveada - 02 - 2008Dokumen77 halamanCurso Fonte Chaveada - 02 - 2008João VictorBelum ada peringkat

- Linha Do Tempo Da EducaçãoDokumen1 halamanLinha Do Tempo Da EducaçãoJoão VictorBelum ada peringkat

- Lição 01 - Isto É Uma Canção PDFDokumen2 halamanLição 01 - Isto É Uma Canção PDFTierry ConstantinoBelum ada peringkat

- FluxogramasDokumen3 halamanFluxogramasJoão VictorBelum ada peringkat

- Cap6 IO DigitalDokumen18 halamanCap6 IO DigitalJoão VictorBelum ada peringkat

- Unificação Da Alemanha e ItáliaDokumen4 halamanUnificação Da Alemanha e ItáliaJoão VictorBelum ada peringkat

- Unificação Da Alemanha e ItáliaDokumen4 halamanUnificação Da Alemanha e ItáliaJoão VictorBelum ada peringkat

- Origem da Ergonomia e sua relação com o DesignDokumen6 halamanOrigem da Ergonomia e sua relação com o DesignAna Beatriz OliveiraBelum ada peringkat

- DFSS PDFDokumen33 halamanDFSS PDFAntonio Tadeu MenesesBelum ada peringkat

- Planta LavanderiaDokumen1 halamanPlanta LavanderiaLais RotheBelum ada peringkat

- Domain Driven Design: DomínioDokumen2 halamanDomain Driven Design: DomínioorualconectBelum ada peringkat

- 2022.2 - Empreendedorismo DigitalDokumen7 halaman2022.2 - Empreendedorismo Digitaldeivide_Belum ada peringkat

- Slides Unificados AutoCadDokumen66 halamanSlides Unificados AutoCadVeronica Da Silva LimaBelum ada peringkat

- Caracteres e Prop SeparaçãoDokumen56 halamanCaracteres e Prop SeparaçãomizuhokazamiBelum ada peringkat

- Modelagem Do Vestuário InformatizadaDokumen12 halamanModelagem Do Vestuário InformatizadaReginaldo Costa SilvaBelum ada peringkat

- Tecnicas Digitacao ManualDokumen10 halamanTecnicas Digitacao ManualJorge BandeiraBelum ada peringkat

- Design, Bordado e Resistência Entre Trajes e Pontos de Oposição.Dokumen145 halamanDesign, Bordado e Resistência Entre Trajes e Pontos de Oposição.Fernanda CintraBelum ada peringkat

- Ficha Tecnica 13807Dokumen23 halamanFicha Tecnica 13807romuloajBelum ada peringkat

- Apostila Design JogosDokumen117 halamanApostila Design JogosMALVESG100% (2)

- Cap. 3 - Design, Cultura e Sociedade - Gui BonsiepeDokumen28 halamanCap. 3 - Design, Cultura e Sociedade - Gui BonsiepeAyla Leite100% (1)

- CV - Gabriel BusatoDokumen5 halamanCV - Gabriel BusatoGabriel da RochaBelum ada peringkat

- Suas Reuniões Tem Cadeira Vazia PDFDokumen6 halamanSuas Reuniões Tem Cadeira Vazia PDFLucas R. D. OliveiraBelum ada peringkat