Gabarito Comentado - Com - Versão A

Diunggah oleh

Ana Lúcia Costa de AbreuDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Gabarito Comentado - Com - Versão A

Diunggah oleh

Ana Lúcia Costa de AbreuHak Cipta:

Format Tersedia

CONHECIMENTOS ESPECIALIZADOS

41) Um dado condutor 1, que tem resistência R, comprimento L, área de seção reta A e resistividade , foi substituído

por outro condutor 2, com a mesma resistividade, entretanto, com o dobro do comprimento e com metade da área

de seção reta do condutor 1. Comparativamente, o valor da resistência do condutor 2 será

a) a mesma do condutor 1.

b) a metade do valor de resistência do condutor 1.

c) duas vezes maior que o valor de resistência do condutor 1.

d) quatro vezes maior que o valor de resistência do condutor 1.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA D)

De acordo com os dados apresentados, tem-se:

l1 A1

R1 ρ1 l 2 2l 1 A2

A1 2

2 l1 l

R 2 ρ1 2 2 ρ1 1

A1 A1

2

l1

R2 4 ρ 4 R1

1 A1

Fonte: GUSSOW, Milton. Eletricidade básica. 2. ed. rev. e ampl. São Paulo: Pearson Makron Books, 1997. 639p.

(Schaum). (Cap. 4, pág. 72).

Gabarito Comentado – CFOE 2015 – COM – Versão A -1-

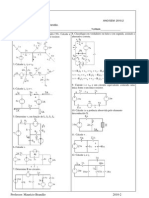

42) Analise o circuito abaixo.

Sendo V1=50V, R1=R3=R4=100Ω e R2=R5=R6=50Ω, calcule o valor da corrente no ramo g-d, em Ampères,

considerando-se que o ramo c-b esteja aberto.

a) 0,5A.

b) 1,0A.

c) 2,0A.

d) 2,5A.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA A)

Na análise do circuito apresentado, observa-se que os ramos g-f, f-a, h-a estão ligados de tal forma que o resistor R5

está em curto-circuito. Com o ramo c-b aberto, o resistor R6 entra em série com o resistor R2. Desse modo, a partir

dos pontos a e b, tem-se um circuito com R1=R3=R4=(R2+R6)=100Ω, o que equivale a N=4 resistores R iguais em

paralelo.

Onde:

N, número de resistores iguais;

Rt, Resistor equivalente; e,

It, corrente total do circuito;

Sendo:

Rt = R / N

It = V / Rt

Como os resistores são iguais, as correntes em cada ramo paralelo também serão iguais.

I1 = I2 = I3 = I4 = I

It

It = I1 + I2 + I3 + I4 = 4.I ou I

4

Então:

100

Rt 25Ω

4

It = V / Rt = 50 / 25 = 2A

It 2

I1 0,5A

4 4

Fonte: GUSSOW, Milton. Eletricidade básica. 2. ed. rev. e ampl. São Paulo: Pearson Makron Books, 1997. 639p.

(Schaum). (Cap. 5, pág. 96 a 99).

Gabarito Comentado – CFOE 2015 – COM – Versão A -2-

43) Nos terminais da bateria de um automóvel desligado, foi medido o valor de 12Vdc, sem carga. Durante a

realização da partida, a tensão medida nos terminais caiu para 10Vdc. A resistência do motor de arranque na

partida é de 0,5Ω. Marque a alternativa correta relativa ao valor da resistência interna da bateria.

a) 0,2Ω

b) 0,3Ω

c) 0,1Ω

d) 0,5Ω

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA C)

Todo gerador de tensão cc possui uma resistência interna Ri, que está em série com a tensão gerada VB. Quando

não há carga ligada à bateria, não há corrente, então a queda de tensão em Ri será igual a zero. A tensão VB

projeta-se sobre os terminais de saída da bateria, sendo igual a 12Vdc.

Durante a partida, uma carga, no caso o motor de arranque, é ligada à bateria. A corrente circula pela Ri e pela carga.

Observa-se uma queda de tensão sobre Ri, que se subtrai do valor de VB, obtendo-se o valor entregue à carga

conforme a fórmula: VL = VB - IL.Ri. No caso, esta será de 10Vdc.

Para achar o valor de IL, basta aplicar a fórmula IL = VL/RL.

Então RL= 0,5Ω, temos

IL=10/0,5=20A.

Como:

VL = VB - IL.Ri

Substituindo-se os valores na fórmula, tem-se:

Ri = (VB – VL) / IL

Ri = (12 – 10 ) /20

Ri = 2/20

Ri = 0,1Ω

Fonte: GUSSOW, Milton. Eletricidade básica. 2. ed. rev. e ampl. São Paulo: Pearson Makron Books,1997. 639p.

(Schaum). (Cap. 6, pág. 126 e 127).

44) Um sargento da Base Aérea de Santa Cruz necessitava realizar manutenção corretiva no sistema de

acionamento dos portões do Hangar. Ele observou, porém, que o capacitor de correção do fator de potência,

ligado em paralelo com o motor de indução, estava danificado. Como sua especificação estava deteriorada pela

umidade, não foi possível encontrar sua capacitância. Sabendo-se, de antemão, que a corrente do capacitor era

22A e a tensão e a frequência da rede, 220Vca/60Hz, foi possível calcular o valor do capacitor. É correto afirmar

que o valor encontrado foi de

a) 228µF.

b) 233µF.

c) 250µF.

d) 265µF.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA D)

Achando o valor de Xc tem-se:

Vc 220V

Xc = 10Ω

Ic 22A

Aplicando na fórmula que relaciona Xc com sua capacitância fica:

1

Xc =

2fC

1

C=

2fXc

Substituindo os valores, tem-se:

3 2

1 1 0,159 159.10 .10 5 6

C= 26,5 .10 265 .10 265µF

2fXc 2 .60.10

2

6.10 6

C=265µF

Fonte: GUSSOW, Milton. Eletricidade básica. 2. ed. rev. e ampl. São Paulo: Pearson Makron Books, 1997. 639p.

(Schaum). (Cap. 14, pág. 386 a 392).

Gabarito Comentado – CFOE 2015 – COM – Versão A -3-

45) Quanto ao conceito de ressonância em circuitos RLC série operando em ca – corrente alternada -, é correto

afirmar que

a) um circuito ressoa quando sua resistência total é igual à reatância indutiva (R=XL).

b) um circuito está em ressonância quando a impedância Z é mínima e o fator de potência é igual a 1.

c) a impedância Z do circuito, na ressonância, é máxima e igual às reatâncias XL e XC, que devem ser iguais.

d) um circuito RLC série ressonante tem um ângulo de fase igual a 90° e, portanto, o fator de potência está

próximo a zero.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA B)

A alternativa “A” é incorreta, pois um circuito ressoa quando a reatância capacitiva do circuito é igual à reatância

indutiva, ou seja, XC=XL.

A alternativa “B” é correta, pois uma das características mais importantes de um circuito RLC série na ressonância é

que a reatância capacitiva do circuito é igual à reatância indutiva, ou seja, XC=XL, anulando-se. Portanto, o valor total

de impedância Z é igual ao da resistência R.

2 2

Z R (XL XC)

Como o ângulo de fase é igual a zero, o fator de potência é igual a 1.

A alternativa “C” é incorreta, pois a impedância Z do circuito, na ressonância, é mínima e igual a R.

A alternativa “D” é incorreta, pois um circuito RLC série ressonante tem um ângulo de fase igual a 0° e, portanto, o

fator de potência é igual a um.

Fonte: GUSSOW, Milton. Eletricidade básica. 2. ed. rev. e ampl. São Paulo: Pearson Makron Books,1997. 639p.

(Schaum). (Cap. 18, pág. 492 e 493).

46) Um circuito série é formado por um resistor R, um capacitor C, uma fonte de tensão constante V e uma chave S que

fecha ou abre esse circuito. Supondo que, ao se fechar a chave S, o capacitor demore 7 s para atingir seu valor

estacionário, quantos segundos serão necessários para que a tensão no resistor R caia de 3e V para 3e-1 V?

a) 1,4.

b) 2,0.

c) 2,8.

d) 4,0.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA C)

Considerando que a constante de tempo T para um circuito capacitivo é dada por T = RC, sendo R a resistência e C

a capacitância, e que, em circuitos capacitivos, a tensão e a corrente atingem seus valores finais ou estacionários em

cinco constantes de tempo (5T), tem-se que:

o capacitor da questão atinge seu valor estacionário em 7 s. Se 5T = 7 s, então T = 1,4 s; e

V

o tempo necessário para o decaimento de uma determinada tensão é dado por t RC ln , sendo R o valor da

v

resistência, C o valor da capacitância, ln(V/v) o logaritmo natural da razão entre V, que é a tensão mais alta no início,

e v, que é a tensão mais baixa no final. Substituindo-se os valores conhecidos, tem-se:

V

t RC ln

v

Sendo:

T = RC = 1,4,

V = 3e, e

v = 3e-1

Então:

1,4 lne 1,4 2 2,8

3e 2

t 1,4 ln 1

3e

t = 2,8 s.

Fonte: GUSSOW, Milton. Eletricidade básica. 2. ed. rev. e ampl. São Paulo: Pearson Makron Books,1997. 639p.

(Schaum). (Cap. 19, pág. 535 e 536).

Gabarito Comentado – CFOE 2015 – COM – Versão A -4-

47) Para um amplificador classe B que fornece um sinal de 40V de pico para um alto-falante de 4Ω e uma fonte de

alimentação de Vcc =+ 50V, os valores da potência de entrada, da potência de saída e da eficiência do circuito

são, respectivamente:

a) 400W; 300W; 75%.

b) 280W; 190W; 67,8%.

c) 315W; 200W; 63,49%.

d) 127,3W; 100W; 78,5%.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA C)

Um sinal de 40V de pico alimentando uma carga de 4Ω fornece uma corrente de pico na carga de:

VL (p) 40V

I L (p) 10A

RL 4Ω

Então, o valor cc da corrente fornecida pela fonte de alimentação será:

2 2

I cc I L (p) .10 6,3A

Logo, o valor da potência de entrada liberada pela fonte de tensão vale:

Pi (cc) Vcc.Icc 50.6,3 315W

A potência de saída liberada para a carga é:

2 2

VL (p) 40 V

Po(ca) 200W

2R L 2 4Ω

Portanto, a eficiência será de:

Po(ca) 200

%η .100% .100% 63,49%

Pi(cc) 315

Fonte: BOYLESTAD, Robert L.; NASHELSKY, Louis. Dispositivos eletrônicos e teoria de circuitos. 8. ed. São

Paulo: Pearson Prentice Hall, 2004. 672p. (Cap. 15, pág. 507).

48) Nos dispositivos do tipo transistor de junção bipolar (TBJ) e transistor de efeito de campo (FET), a corrente do

circuito de saída é controlada por um parâmetro do circuito de entrada. É correto afirmar que esses parâmetros

são, respectivamente:

a) corrente Ib e tensão Vgs.

b) corrente Ic e tensão Vds.

c) tensão Vgs e corrente Ib.

d) tensão Vds e corrente Ic.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA A)

A principal diferença entre os tipos de transistores é o fato de o TBJ ser controlado por corrente (Ib) enquanto o FET

é controlado por tensão (Vgs).

Fonte: BOYLESTAD, Robert L.; NASHELSKY, Louis. Dispositivos eletrônicos e teoria de circuitos. 8. ed. São Paulo:

Pearson Prentice Hall, 2004. 672p. (Cap. 5, pág. 174).

Gabarito Comentado – CFOE 2015 – COM – Versão A -5-

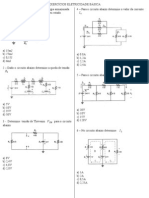

49) Analise o circuito abaixo.

Considerando o diodo como ideal, assinale a alternativa que mostra o sinal de saída Vout.

a) c)

b) d)

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA C)

O circuito ceifador tem como característica a capacidade de ceifar uma porção do sinal de entrada sem distorcer o

restante da forma de onda alternada. Considerando o diodo como ideal, seu comportamento é de uma chave fechada

quando está polarizado diretamente, desta forma VD=0V. Em contrapartida, o mesmo se comporta como uma chave

aberta quando está polarizado reversamente.

Inicialmente, a bateria de +4V está polarizando diretamente o diodo, desta forma, a sua tensão é projetada para a

saída Vout = +4V.

No semiciclo positivo do sinal de entrada, enquanto o seu valor for menor que a tensão da bateria, o diodo estará

polarizado diretamente, e a saída será igual à tensão da bateria Vout = +4V. Quando Vin ≥ +4v, o diodo para de

conduzir, isolando a bateria, e a tensão de saída (Vout) será igual à de entrada (Vin).

Durante todo o semiciclo negativo da entrada, o diodo estará polarizado diretamente e a tensão da bateria será

projetada para a saída Vout = +4V.

Fonte: BOYLESTAD, Robert L.; NASHELSKY, Louis. Dispositivos eletrônicos e teoria de circuitos. 8. ed. São

Paulo: Pearson Prentice Hall, 2004. 672p. (Cap. 2, pág. 58 e 60).

Gabarito Comentado – CFOE 2015 – COM – Versão A -6-

50) Calcule o valor da tensão de saída ao se aplicar 3V na entrada do circuito abaixo. Os valores dos resistores do

circuito estão em OHM (Ω).

a) – 1,5 V.

b) – 6 V.

c) 1,5 V.

d) 6 V.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA B)

O circuito amplificador operacional está funcionando como um amplificador inversor.

A tensão de saída é calculada por:

Rf

Vo Vi

Ri

Vi = 3V

Rf = 1 MΩ

Ri = 500KΩ

Logo

6 1

1 x 10 1 x 10

Vo 3

x3 x 3 2 x 3 6V

500 x 10 5

Fonte: BOYLESTAD, Robert L.; NASHELSKY, Louis. Dispositivos eletrônicos e teoria de circuitos. 8. ed. São

Paulo: Pearson Prentice Hall, 2004. 672p. (Cap. 13, pág. 459).

51) Considere o transistor de silício do circuito abaixo no estado de saturação, com VCE = 0V.

É correto afirmar que a junção

a) base-coletor está polarizada diretamente.

b) base-coletor está polarizada reversamente.

c) base-emissor está polarizada reversamente.

d) base-emissor está polarizada diretamente com VBE = +Vcc.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA A)

O circuito operando na região de saturação possui as seguintes características: junção base-emissor polarizada

diretamente com Vbe = 0,7V e junção base-coletor polarizada diretamente.

Fonte: BOYLESTAD, Robert L.; NASHELSKY, Louis. Dispositivos eletrônicos e teoria de circuitos. 8. ed. São

Paulo: Pearson Prentice Hall, 2004. 672p. (Cap. 4, pág. 121).

Gabarito Comentado – CFOE 2015 – COM – Versão A -7-

52) Analise o circuito abaixo.

Um técnico em eletrônica deseja que o LED permaneça aceso. Considerando-se que as características do

amplificador operacional são ideais, o valor da tensão presente na entrada do amplificador operacional (Vin) deve

ser

a) igual a +8V.

b) igual a +12V.

c) maior que +7V.

d) menor que +6V.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA D)

O circuito amplificador operacional está funcionando como comparador.

A tensão de referência é obtida pelo divisor de tensão formado pelos resistores R2 e R3 iguais a 220Ω. Logo, a

tensão de referência vale a metade do valor da tensão aplicada (+6V).

Quando a tensão (Vin) presente na entrada inversora do amplificador operacional possuir um valor abaixo da entrada

não inversora, ou seja, Vin < +6V, a saída do amplificador operacional terá o valor de saturação positivo (+12V),

acendendo o LED.

Então, Vin deve ser menor que +6V.

Fonte: BOYLESTAD, Robert L.; NASHELSKY, Louis. Dispositivos eletrônicos e teoria de circuitos. 8. ed. São

Paulo: Pearson Prentice Hall, 2004. 672p. (Cap. 14, pág. 485).

53) Quanto aos sistemas de comunicações por satélite, é correto afirmar que

a) a unidade rádio do satélite é conhecida como transponder, o qual é responsável por receber o sinal captado

pela antena, realizar a conversão da frequência, amplificar o sinal em potência e devolvê-lo à antena.

b) as frequências de operação em sistemas de comunicações por satélite são de 6 KHz, tanto para a transmissão

quanto para a recepção.

c) satélites do sistema de posicionamento global (GPS) são exemplos de satélites de comunicações

geoestacionários ou geossíncronos.

d) um satélite posicionado em órbita geossíncrona (GEO) leva de 5 a 12 horas para percorrer toda a órbita.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA A)

A alternativa “A” está correta, pois o transponder é a unidade rádio do satélite, que recebe o sinal captado pela

antena, converte em frequência, amplifica em potência e devolve à antena.

A alternativa “B” é incorreta, pois as frequências de operação são de 6 GHz para transmissão terrena ao satélite e de

4 GHz do satélite para a Terra. Outras faixas de frequências disponíveis são: 7/8, 10/12, 12/14, 14/18, 20/27 GHz.

A alternativa “C” é incorreta, pois satélites GPS estão posicionados em órbitas médias (MEO).

A alternativa “D” é incorreta, pois um satélite posicionado em órbita geossíncrona (GEO) encontra-se no plano do

equador terrestre. Em órbita geossíncrona, o satélite permanece parado no espaço, sobre um ponto fixo na Terra,

acompanhando-a em seu movimento de rotação. Satélites em órbita média (MEO) levam de 5 a 12 horas para

percorrer a órbita.

Fonte: MEDEIROS, Júlio César de Oliveira. Princípios de Telecomunicações: teoria e prática. 2. ed. São Paulo:

Érica, 2007. 316p. (Cap. 1, pág. 30 e 31).

Gabarito Comentado – CFOE 2015 – COM – Versão A -8-

54) Para a escolha e aplicação adequada de uma antena em um sistema de comunicação, é necessário definir suas

características e seus parâmetros. Assinale a alternativa que descreve corretamente um parâmetro da antena.

a) A abertura efetiva da antena não está relacionada com o seu ganho.

b) O ganho é expresso pelo produto da largura de feixe pela diretividade.

c) A real resistência da antena é responsável pela radiação da onda eletromagnética.

d) Diretividade é a propriedade de irradiar mais fortemente em algumas direções que em outras.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA D)

A alternativa “A” está incorreta, pois a abertura efetiva da antena está intimamente relacionada com o seu ganho.

A alternativa “B” está incorreta, pois o ganho é o produto da diretividade pela eficiência do feixe da antena.

A alternativa “C” está incorreta, pois a resistência real da antena é a responsável pela energia dissipada na forma de

calor.

A alternativa “D” está correta, pois diretividade é a propriedade de irradiar mais fortemente em algumas direções que

em outras.

Fonte: MEDEIROS, Júlio Cesar de Oliveira. Princípios de Telecomunicações: teoria e prática. 2. ed. São Paulo:

Érica, 2007. 316p. (Cap. 8, pág. 197 a 202).

55) O processo de conversão do sinal digital em sinal analógico - conversão D/A do sinal PCM - consiste nas

seguintes etapas:

a) regeneração, decodificação e filtragem.

b) amostragem, quantização e codificação.

c) amostragem, filtragem, quantização e codificação.

d) regeneração, quantização, decodificação e filtragem.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA A)

O processo de conversão do sinal digital em sinal analógico – conversão D/A do sinal PCM – consiste nas seguintes

etapas: regeneração, decodificação e filtragem.

Fonte: MEDEIROS, Júlio Cesar de Oliveira. Princípios de Telecomunicações: teoria e prática. 2. ed. São Paulo:

Érica, 2007. 316 p. (Cap. 2, pág. 74).

Gabarito Comentado – CFOE 2015 – COM – Versão A -9-

56) “Os gases não são responsáveis somente pela curvatura das ondas, também impõem perdas por absorção, que

podem ser leves ou acentuadas, em função da frequência da onda”. Observe o gráfico abaixo das atenuações na

troposfera terrestre.

(Fonte: Reference Data for Engenieers, 9ª Edição.)

Qual o valor do comprimento de onda, em metros (m), da frequência que sofre a maior atenuação provocada por

O2, na troposfera terrestre, na faixa de 3 a 350GHz?

a) 0,01.

b) 0,005.

c) 0,003.

d) 0,04.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA B)

Observa-se no gráfico que a maior atenuação em dB para O2 ocorre na frequência de 60GHz. Para se encontrar o

comprimento de onda, usa-se a relação:

Vc

λ

f

Onde:

VC é a velocidade da luz;

f é a frequência em Hz; e,

λ é o cumprimento de onda, em metros;

Logo:

8

3 .10

λ 9

0,005m

60 .10

Fonte: MEDEIROS, Júlio Cesar de Oliveira. Princípios de Telecomunicações: teoria e prática. 2. ed. São Paulo:

Érica, 2007. 316 p. (Cap. 4, pág. 107 e Cap. 9, pág. 224 e 225).

Gabarito Comentado – CFOE 2015 – COM – Versão A - 10 -

57) Circuitos aritméticos fazem parte de uma classe de circuitos combinacionais utilizados nas unidades lógicas

aritméticas dos microprocessadores. Considerando essa informação, analise o circuito abaixo.

É correto afirmar que o circuito analisado representa um

a) meio somador.

b) meio subtrator.

c) somador completo.

d) subtrator completo.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA B)

A partir do circuito analisado, monta-se a seguinte tabela verdade:

A B X Y

0 0 0 0

0 1 1 1

1 0 1 0

1 1 0 0

Essa tabela é o resultado da subtração do número binário A por B. X é o resultado e Y é o valor do transporte, que

ocorre quando B é maior que A, ou seja, a tabela representa um subtrator.

O circuito é um meio subtrator, pois manipula apenas dois dígitos binários, não há entrada para o bit de transporte.

As alternativas “A” e “C” estão incorretas, porque a tabela verdade resultante corresponde a uma subtração entre A

e B.

A alternativa “D”, está incorreta, porque o circuito não possui a entrada de transporte da coluna anterior.

Fonte: IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel. Elementos de eletrônica digital. 40. ed. São Paulo:

Érica, 2008. 524 p. (Cap. 5, pág. 217).

Gabarito Comentado – CFOE 2015 – COM – Versão A - 11 -

58) Analise a figura abaixo.

O sistema efetua a soma de dois números de 4 dígitos binários e apresenta nas saídas os valores S4 = 1, S3 = 1,

S2 = 0, S1 = 1 e S0 = 0. Os valores de transporte de saída são Ts1 = Ts2 = 0 e Ts3 = 1.

Considerando-se que A3 e B3 são os bits mais significativos e A0 e B0 são os menos significativos, qual alternativa

representa os dois números da entrada em decimal, de acordo com os valores apresentados na saída?

a) 13 e 13.

b) 10 e 16.

c) 12 e 14.

d) 11 e 15.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA C)

Para o somador 4 ter as saídas S4 = 1 e S3 = 1, os valores de A3 e B3, necessariamente, serão iguais a 1, já que

Te4 = Ts3 = 1. Tem-se: A3 = 1, B3 = 1.

Para o somador 3 ter as saídas S2 = 0 e Ts3 = 1, os valores de A2 e B2, necessariamente, serão iguais a 1, já que

Ts2 = Te3 = 0. Tem-se: A2 = 1, B2 = 1.

Para o somador 2 ter as saídas S1 = 1 e Ts2 = 0, os valores de A1 e B1 podem admitir (A1 = 0 e B1 = 1) ou (A1 = 1

e B1 = 0), já que Ts1 = Te2 = 0. Pode-se ter duas condições: A1 = 0 e B1 = 1 ou A1 = 1 e B1 = 0.

Para o somador 1 ter as saídas S0 = 0 e Ts1 = 0, os valores de A0 e B0, necessariamente, serão iguais a 0. Tem-se:

A0 = 0 e B0 = 0.

Desta forma, os números “A” e “B” serão:

A3 = 1, A2 = 1, A1 = 0 ou A1 = 1, A0 = 0

B3 = 1, B2 = 1, B1 = 1 ou B1 = 0, B0 = 0

Como se verifica, há duas condições:

Se o valor de “A” for 1100, o valor de “B” será 1110. Em decimal, A = 12 e B = 14.

Se o valor de “A” for 1110, o valor de “B” será 1100. Em decimal, A = 14 e B = 12.

Logo, a soma será o número 26 em decimal e 11010 em binário (S4 = 1, S3 = 1, S2 = 0, S1 = 1 e S0 = 0).

Então, os valores de A e B podem ser: A = 12 e B = 14 ou A = 14 e B = 12.

De qualquer forma, as parcelas desta soma serão os números 12 e 14 em decimal.

Fonte: IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel. Elementos de eletrônica digital. 40. ed. São Paulo:

Érica, 2008. 524p. (Cap. 5, pág. 214 e 215).

Gabarito Comentado – CFOE 2015 – COM – Versão A - 12 -

59) Analise as formas de onda das entradas J, K e CK de um flip-flop JK.

t1 t2 t3 t4 t5 t6 t7 t8 t9 t10 t11 t12

Considere a saída Q em nível 1 no estágio anterior a t1. É correto afirmar que a forma de onda da saída Q desse

flip-flop será.

a)

b)

c)

d)

t1 t2 t3 t4 t5 t6 t7 t8 t9 t10 t11 t12

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA C)

Conforme a simbologia do flip-flop apresentado, o Clock (CK) é ativo na descida, ou seja, do bit 1 para o bit 0. Logo,

as análises serão nos tempos t2, t4, t6, t8, t10 e t12.

Conhecendo-se a tabela da verdade do flip-flop JK, tems-e:

J K Q

0 0 Qa

0 1 0

1 0 1

1 1 Ǭa

No intervalo de tempo t2, a entrada J vale 1 e K vale 0, então, de acordo com a tabela da verdade, a saída Q será

igual a 1;

No intervalo de tempo t4, a entrada J vale 0 e K vale 0, então, de acordo com a tabela da verdade, a saída Q será

igual a Qa (estado anterior), Q = 1;

No intervalo de tempo t6, a entrada J vale 0 e K vale 1, então, de acordo com a tabela da verdade, a saída Q será

igual a 0;

No intervalo de tempo t8, a entrada J vale 0 e K vale 1, então, de acordo com a tabela da verdade, a saída Q será

igual a 0;

No intervalo de tempo t10, a entrada J vale 1 e K vale 0, então, de acordo com a tabela da verdade, a saída Q será

igual a 1;

No intervalo de tempo t12, a entrada J vale 1 e K vale 0, então, de acordo com a tabela da verdade, a saída Q será

igual a 1.

Fonte: IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel. Elementos de eletrônica digital. 40. ed. São Paulo:

Érica, 2008. 524p. (Cap. 6, pág. 244).

Gabarito Comentado – CFOE 2015 – COM – Versão A - 13 -

60) Observe o circuito Digital-Analógico com chave seletora digital abaixo.

Considere que as portas lógicas do conversor D/A pertencem à família TTL (nível alto de saída = +5Vdc) e que o

valor das entradas ABC valem 101, respectivamente. Calcule o valor de Vs.

a) – 9,37 V.

b) – 11,53 V.

c) – 13,12 V.

d) – 14,77 V.

JUSTIFICATIVA DA ALTERNATIVA CORRETA: (LETRA A)

Utilizando a expressão geral do conversor D/A com amplificador operacional e os dados fornecidos no circuito,

obtém-se:

V.Ro B C

Vs A

R 2 4

Onde:

V = +5Vdc

Ro = 150Ω

R = 100Ω

A=1

B=0

C=1

Substituindo os valores na fórmula, tem-se:

V.Ro B C 5.150 0 1 5

Vs A = 1 = 7,5 = –9,37V

R 2 4 100 2 4 4

Fonte: IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel. Elementos de eletrônica digital. 40. ed. São Paulo:

Érica, 2008. 524p. (Cap. 7, pág. 314 e 326).

Gabarito Comentado – CFOE 2015 – COM – Versão A - 14 -

Anda mungkin juga menyukai

- CFOE 2019 - CorrigidaDokumen28 halamanCFOE 2019 - CorrigidaDeisiellyRibeiroBelum ada peringkat

- Cfoe - Comunicações - Versão b2013Dokumen20 halamanCfoe - Comunicações - Versão b2013MarcosCardozoBelum ada peringkat

- Apostila Aeronáutica Eaoear 2018 Engenharia Eletrônica + BrindesDokumen2 halamanApostila Aeronáutica Eaoear 2018 Engenharia Eletrônica + BrindesAPRENDAMAISBelum ada peringkat

- Seleção Aeronáutica 2010Dokumen84 halamanSeleção Aeronáutica 2010mvjn100% (1)

- Sequencia de ResistoresDokumen18 halamanSequencia de ResistoresbrunamouziinhoBelum ada peringkat

- 2000 Provao EletricaDokumen24 halaman2000 Provao EletricaLuis Cláudio LABelum ada peringkat

- Conheça os principais pontos do exame de seleção para oficiais da AeronáuticaDokumen28 halamanConheça os principais pontos do exame de seleção para oficiais da AeronáuticaCarvalho JuniorBelum ada peringkat

- Exercicio de CircuitosDokumen2 halamanExercicio de CircuitosFrancisco SilvaBelum ada peringkat

- Lista de exercícios de associação mista de resistoresDokumen4 halamanLista de exercícios de associação mista de resistoresManoella SaraivaBelum ada peringkat

- Grandezas vetoriais e escalaresDokumen23 halamanGrandezas vetoriais e escalaresAnanda FreitasBelum ada peringkat

- Controle de Tráfego Versao ADokumen28 halamanControle de Tráfego Versao ARenata MirellyBelum ada peringkat

- Elementos elétricos passivosDokumen21 halamanElementos elétricos passivosFilipe PradoBelum ada peringkat

- Lista de Execicios Resolvidos Aula 3Dokumen10 halamanLista de Execicios Resolvidos Aula 3paulorjrBelum ada peringkat

- Gabarito Comentado - Controle de Tráfego Aéreo - Versão A ComentadaDokumen13 halamanGabarito Comentado - Controle de Tráfego Aéreo - Versão A ComentadaRenata MirellyBelum ada peringkat

- Questões EletricidadeDokumen9 halamanQuestões EletricidadeJohnnyOliveiraPinheiroBelum ada peringkat

- SI Magnetismo UnidadesDokumen12 halamanSI Magnetismo UnidadesMarcosCardozoBelum ada peringkat

- Batatinha Frita 1 2 3 PDFDokumen451 halamanBatatinha Frita 1 2 3 PDFIsabella Gomes RibeiroBelum ada peringkat

- 1 Lista de Circuitos 1 90 H 2010-2Dokumen3 halaman1 Lista de Circuitos 1 90 H 2010-2kbcao_r100% (1)

- DuvidasDokumen40 halamanDuvidasjeffersansBelum ada peringkat

- Lista 1Dokumen4 halamanLista 1Vinicius GoulartBelum ada peringkat

- Lista de exercícios de circuitos elétricosDokumen6 halamanLista de exercícios de circuitos elétricosDiego BandeiraBelum ada peringkat

- Princípios de Circuitos ElétricosDokumen8 halamanPrincípios de Circuitos ElétricosDouglas CarvalhoBelum ada peringkat

- Prova CFOE 2020Dokumen24 halamanProva CFOE 2020William Sudre de AssisBelum ada peringkat

- Exercícios Eletricidade BásicaDokumen6 halamanExercícios Eletricidade BásicaFelippe CostaBelum ada peringkat

- 1989 Matematica AFADokumen5 halaman1989 Matematica AFAalexandreBelum ada peringkat

- QuadripolosDokumen8 halamanQuadripolosKevin Perez EscalanteBelum ada peringkat

- Determinação de resistência desconhecida com ponte de WheatstoneDokumen6 halamanDeterminação de resistência desconhecida com ponte de WheatstoneNilton CamposBelum ada peringkat

- AULA - Polar de Arrasto AeronavesDokumen67 halamanAULA - Polar de Arrasto AeronavesGiuliano Gardolinski VensonBelum ada peringkat

- Conselhos de vida em carta a adolescenteDokumen13 halamanConselhos de vida em carta a adolescenteGeorge Henrique MacedoBelum ada peringkat

- ASON Nautica-ApostilaDokumen225 halamanASON Nautica-ApostilaHans Donner PantojaBelum ada peringkat

- Lista de Exercícios MEC1Dokumen19 halamanLista de Exercícios MEC1Darlene PereiraBelum ada peringkat

- Apostila EAGS 2024 SEL EEARDokumen15 halamanApostila EAGS 2024 SEL EEARVinicius Borges100% (1)

- MSOM4 - 2S2016 - Cap01 - Serie01Dokumen13 halamanMSOM4 - 2S2016 - Cap01 - Serie01serrano75100% (1)

- CCAexer Resolvidos IIDokumen8 halamanCCAexer Resolvidos IIRoseny BorgesBelum ada peringkat

- Lista Cap 3 Medidas-EletricasDokumen3 halamanLista Cap 3 Medidas-EletricasDavid Sousa100% (1)

- Lista Exercícios RelatividadeDokumen2 halamanLista Exercícios RelatividadeAllanBelum ada peringkat

- Problemas sobre Oscilador HarmônicoDokumen7 halamanProblemas sobre Oscilador HarmônicoLucas CordeiroBelum ada peringkat

- Gabarito Livro Eduardo Mauro 1Dokumen9 halamanGabarito Livro Eduardo Mauro 1paulo ricardoBelum ada peringkat

- Física - Óptica Geométrica - Questões de Vestibulares de 2016Dokumen29 halamanFísica - Óptica Geométrica - Questões de Vestibulares de 2016japizzirani406450% (4)

- Associação de ResistoresDokumen4 halamanAssociação de ResistoresDanilo MenezesBelum ada peringkat

- Física - Clóvis - Exercícios de Eletrodinâmica Geral (Lista 1) 2018 PDFDokumen6 halamanFísica - Clóvis - Exercícios de Eletrodinâmica Geral (Lista 1) 2018 PDFclovisjrBelum ada peringkat

- Capítulo VII - Forças em Vigas e CabosDokumen35 halamanCapítulo VII - Forças em Vigas e CabosAlexanderMarkovikBelum ada peringkat

- S Petrobras Engenheiro Eletricista ProvaDokumen12 halamanS Petrobras Engenheiro Eletricista ProvaLeonardo H. MacedoBelum ada peringkat

- Física - Resoluções - DinâmicaDokumen9 halamanFísica - Resoluções - DinâmicaFísica Concurso Vestibular100% (2)

- Exercícios Sobre Associação de ResistoresDokumen5 halamanExercícios Sobre Associação de ResistoresMATEUS LourençoBelum ada peringkat

- Forças componentes cálculosDokumen2 halamanForças componentes cálculosVitor Ruffini100% (1)

- Resolução de exercícios de circuitos elétricosDokumen4 halamanResolução de exercícios de circuitos elétricosIdo ManoelBelum ada peringkat

- Exercícios de Estática com ForçasDokumen4 halamanExercícios de Estática com ForçasLuis HenriqueBelum ada peringkat

- Apostila AFA 2006 A 2016Dokumen254 halamanApostila AFA 2006 A 2016Gabriel SilvaBelum ada peringkat

- Lista de Exercícios 1 - 1 AvaliaçãoDokumen8 halamanLista de Exercícios 1 - 1 AvaliaçãoMatheus GhettinoBelum ada peringkat

- Teo C.problemasEE EMS1Dokumen5 halamanTeo C.problemasEE EMS1Lopes Fernando Seabra BoaBelum ada peringkat

- LISTA DE EXERCÍCIOS DE ELETRICIDADE APLICADADokumen4 halamanLISTA DE EXERCÍCIOS DE ELETRICIDADE APLICADAFAbio AraujoBelum ada peringkat

- Circuitos R e RC lista exercícios físicaDokumen5 halamanCircuitos R e RC lista exercícios físicaRaphael BernardoBelum ada peringkat

- Exercícios Eletricidade - SoluçõesDokumen11 halamanExercícios Eletricidade - SoluçõesLaura SantosBelum ada peringkat

- EE530/EE532 - Simulação B2 - Retificador de Onda CompletaDokumen1 halamanEE530/EE532 - Simulação B2 - Retificador de Onda CompletaJoe StiflerBelum ada peringkat

- ChopperDokumen5 halamanChopperFabio KravetzBelum ada peringkat

- Choppers e Inversores: Simulações com PSIMDokumen5 halamanChoppers e Inversores: Simulações com PSIMFabio KravetzBelum ada peringkat

- Exercícios de corrente elétrica e resistênciaDokumen5 halamanExercícios de corrente elétrica e resistênciasidneypcostaBelum ada peringkat

- ATV EBD AnsiedadeDokumen4 halamanATV EBD AnsiedadeAna Lúcia Costa de AbreuBelum ada peringkat

- Dialnet JejumIntermitenteEDietaLowCarbNaComposicaoCorporal 6603195Dokumen8 halamanDialnet JejumIntermitenteEDietaLowCarbNaComposicaoCorporal 6603195Ana Lúcia Costa de AbreuBelum ada peringkat

- Comunicação Oficial PDFDokumen1 halamanComunicação Oficial PDFAna Lúcia Costa de AbreuBelum ada peringkat

- Portugues 2009Dokumen6 halamanPortugues 2009junioalvessdasBelum ada peringkat

- Manual de Manutenção AeronáuticaDokumen484 halamanManual de Manutenção AeronáuticaRonaldoePatricia Araujo100% (4)

- Gabarito 2008 PDFDokumen1 halamanGabarito 2008 PDFAna Lúcia Costa de AbreuBelum ada peringkat

- PentecosteDokumen9 halamanPentecosteAna Lúcia Costa de AbreuBelum ada peringkat

- Comunicação OficialDokumen6 halamanComunicação OficialAna Lúcia Costa de AbreuBelum ada peringkat

- Prova Do ITA 1° Dia 2017Dokumen7 halamanProva Do ITA 1° Dia 2017Fernanda RibeiroBelum ada peringkat

- O declínio da lavoura e a ascensão dos centros urbanos no BrasilDokumen6 halamanO declínio da lavoura e a ascensão dos centros urbanos no BrasilAna Lúcia Costa de AbreuBelum ada peringkat

- Atividades de Ligar Os Pontos para Adultos 1Dokumen1 halamanAtividades de Ligar Os Pontos para Adultos 1Ana Lúcia Costa de AbreuBelum ada peringkat

- Tapete CrochêDokumen2 halamanTapete CrochêAna Lúcia Costa de AbreuBelum ada peringkat

- Tabela de Honorários 2017Dokumen9 halamanTabela de Honorários 2017Alexandre MassarelliBelum ada peringkat

- Crochê passo a passo grátisDokumen2 halamanCrochê passo a passo grátisAna Lúcia Costa de AbreuBelum ada peringkat

- Resumo Cartas de PauloDokumen8 halamanResumo Cartas de PauloAna Lúcia Costa de Abreu100% (2)

- Novos Soldos PercentualDokumen1 halamanNovos Soldos PercentualAnonymous 0nrM2eBelum ada peringkat

- Comunicacoes Versao BDokumen28 halamanComunicacoes Versao BAna Lúcia Costa de AbreuBelum ada peringkat

- Paz multidimensionalDokumen28 halamanPaz multidimensionalAna Lúcia Costa de AbreuBelum ada peringkat

- ES CFOE 2015 – GABARITO OFICIAL DE MATEMÁTICA COM JUSTIFICATIVA PARA ALTERAÇÃO NO GABARITODokumen2 halamanES CFOE 2015 – GABARITO OFICIAL DE MATEMÁTICA COM JUSTIFICATIVA PARA ALTERAÇÃO NO GABARITOAna Lúcia Costa de AbreuBelum ada peringkat

- Introdução à Poesia Hebraica BíblicaDokumen139 halamanIntrodução à Poesia Hebraica BíblicaFlávio Filho100% (1)

- Comunicação Oficial PDFDokumen1 halamanComunicação Oficial PDFAna Lúcia Costa de AbreuBelum ada peringkat

- Dolghie PDFDokumen17 halamanDolghie PDFAna Lúcia Costa de AbreuBelum ada peringkat

- Circuitos elétricos PREMEDICINADokumen8 halamanCircuitos elétricos PREMEDICINALyanna LimaBelum ada peringkat

- Semana 29Dokumen15 halamanSemana 29Adriano LimaBelum ada peringkat

- Atividade - Física 3 SérieDokumen5 halamanAtividade - Física 3 SérieKelvini CerqueiraBelum ada peringkat

- Lista de Física do Lyceu de GoiâniaDokumen2 halamanLista de Física do Lyceu de GoiâniaGabriel HenriqueBelum ada peringkat

- Lista 1 SEP 1Dokumen6 halamanLista 1 SEP 1Filipe AugustoBelum ada peringkat

- Concurso Público COPEL Prova TécnicaDokumen12 halamanConcurso Público COPEL Prova TécnicaOsmir M. TupanBelum ada peringkat

- Prática 6 - Polarização Por Divisor de Tensão Do TBJDokumen17 halamanPrática 6 - Polarização Por Divisor de Tensão Do TBJEpitácio Junior Mauriz de Moura FeitosaBelum ada peringkat

- CAP 2 Análise de Circuito em Corrente ContínuaDokumen13 halamanCAP 2 Análise de Circuito em Corrente ContínuaSansy Silva Moreno100% (1)

- Circuitos de rádio controle remoto de 27 MHzDokumen43 halamanCircuitos de rádio controle remoto de 27 MHzMaurilio CaetanoBelum ada peringkat

- Eletrônica Analógica:) IC (MIN) É A Corrente de Coletor para Uma Tensão de Entrada Mínima. em Muitos ProjetosDokumen3 halamanEletrônica Analógica:) IC (MIN) É A Corrente de Coletor para Uma Tensão de Entrada Mínima. em Muitos ProjetosWellingtonBelum ada peringkat

- Circuitos Elétricos BásicosDokumen12 halamanCircuitos Elétricos BásicosGabriela PozzebonBelum ada peringkat

- Análise de Circuitos de Corrente ContínuaDokumen98 halamanAnálise de Circuitos de Corrente ContínuaAlberto Chicava SecoBelum ada peringkat

- Associações de caixas acústicas em série e paraleloDokumen13 halamanAssociações de caixas acústicas em série e paraleloandremassaBelum ada peringkat

- Exercicios de EletricaDokumen20 halamanExercicios de EletricaAlexsandro AndradeBelum ada peringkat

- AVALIAÇÃO BIMESTRAL - 3º BI - 3º Médio - 2023Dokumen2 halamanAVALIAÇÃO BIMESTRAL - 3º BI - 3º Médio - 2023Maju RamosBelum ada peringkat

- Circuitos Elétricos: Leis de Ohm e Cálculos BásicosDokumen6 halamanCircuitos Elétricos: Leis de Ohm e Cálculos BásicosJoão Victor Carvalho PinheiroBelum ada peringkat

- GABARITO MASTER Cálculo Diferencial e Integral III (MAD105)Dokumen75 halamanGABARITO MASTER Cálculo Diferencial e Integral III (MAD105)Milto Cezar Gomes100% (2)

- Circuitos Elétricos IDokumen37 halamanCircuitos Elétricos Iantonio carlos bassoBelum ada peringkat

- ELETRODINÂMICADokumen38 halamanELETRODINÂMICAAna Kelly AzevedoBelum ada peringkat

- Circuitos ElétricosDokumen39 halamanCircuitos ElétricosRebecca Cardoso47% (15)

- Eletricidade AplicadaDokumen61 halamanEletricidade AplicadaIsaque Ferreira100% (4)

- Teoremas de linearidade e circuitos elétricosDokumen14 halamanTeoremas de linearidade e circuitos elétricosiaraBelum ada peringkat

- Leis da Eletricidade: Lei de Ohm e Potência ElétricaDokumen61 halamanLeis da Eletricidade: Lei de Ohm e Potência Elétricagustavoguilherme123Belum ada peringkat

- Circuitos Elétricos I (UCP 2019-1Dokumen109 halamanCircuitos Elétricos I (UCP 2019-1Dykes Araujo de BarrosBelum ada peringkat

- Circuitos com capacitores e indutoresDokumen60 halamanCircuitos com capacitores e indutoresWagner RibeiroBelum ada peringkat

- Avaliação de Física (Associação de Resistores e Geradores)Dokumen4 halamanAvaliação de Física (Associação de Resistores e Geradores)10kaiobrunoBelum ada peringkat

- Segunda Lei de Kirchhoff (LTKDokumen13 halamanSegunda Lei de Kirchhoff (LTKEduardoBelum ada peringkat

- Electricidade e Electrónica AutomóvelDokumen4 halamanElectricidade e Electrónica AutomóvelmitoswrcBelum ada peringkat

- Relatório Experimento I (Resistores Lineares e Não Lineares) - Circuitos e FotônicaDokumen12 halamanRelatório Experimento I (Resistores Lineares e Não Lineares) - Circuitos e FotônicaLeonardo NoronhaBelum ada peringkat

- Manual Electronica 2 IEFP PDFDokumen191 halamanManual Electronica 2 IEFP PDFavelinomartins100% (1)