Abstract Nikhil Rane SE (ENTC) SSBT COET Milestone 2k18

Diunggah oleh

navneet patilHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Abstract Nikhil Rane SE (ENTC) SSBT COET Milestone 2k18

Diunggah oleh

navneet patilHak Cipta:

Format Tersedia

Abstract: Integral use of field-programmable gate array (FPGA), Delay Locked Loop (DLL) and Micro

Photodiode Array (MPA) for Artificial Vision in fully automated robots, self-driving automobiles and

humans.

Nikhil Pramod Rane (ranenikhil999@gmail.com)

Shram Sadhana Bombay Trust's COLLEGE OF ENGINEERING AND TECHNOLOGY, Bambhori,

Jalgaon (Maharashtra). SE (E & TC).

Abstract: The proposed system consists of a combination of circuitry which consists of an external (CCD

or CMOS) digital camera which will acquire an image, whereupon it will be encoded by PWM encoder

which will be transmitted via RF telemetry to a transceiver. Video processing will be implemented using

SRAM frame buffers, ADC (Analog to Digital converters) and a field programmable gate array (FPGA)

which is an integrated circuit (IC) semiconductor device containing programmable logic components and

programmable interconnects. Reconfigurable FPGA's allows flexibility for various image processing

algorithms using artificial neural networks. A data signal will be transmitted by AM/ ASK modulation

after which it will be passed through a class E power amplifier. The signal will be rectified and filtered,

and the overall circuitry will be capable of extracting power, data, and a clock signal. The subsequently

derived image will then be stimulated upon the Micro Photodiode Array. The inductive link used in our

system consists of two resonant circuits which provide data for setting the configuration of the stimulating

electrodes in the photoreceptive MPA. A DC power supply is obtained by the rectification of the

incoming RF signal which solves the problem of external power supply. The receiver on the secondary

side extracts four bits of data for each pixel from the incoming RF signal and provides filtering,

demodulation and amplification. The extracted data is interpreted by the electrode signal driver which

finally generates appropriate currents for the stimulating electrodes in terms of magnitude, phase, pulse

width, height and frequency. The special feature of this system is that it will use a Delay Locked Loop

(DLL) to decipher the PWM wave. Twenty controlled variable current sources (CVCS) will receive

clocking and data info from deciphered PWM wave each of which is connected to 5 electrodes using

DEMUX which will provide 4 bit linear scale stimulus which in turn altogether (100 electrodes) will

form desired image pattern. We use local gain control instead of primitive frames to obtain precisely

timed temporal contrast subsequently removing the limitation of uniform sampling rate. Visual sensations

or “phosphenes” can be evoked by electrical stimulation of the different levels of the visual pathway by

altering the membrane potential in retina in case of humans and by far if the same system is used in

automated robots along with the existing system will give them artificial vision and can also aid in fully

automated transportation vehicles. Thus we see this paper have multiple high impact broad domain

applications.

Keywords: Delay Locked Loop (DLL), SRAM frame buffers, Field Programmable Gate Array (FPGA),

Complementary metal–oxide semiconductor (CMOS) camera, class E power amplifier, Integrated Circuit

(IC), Micro Photodiode Array (MPA), Controlled Variable Current Sources (CVCS), local gain control,

neural network.

Anda mungkin juga menyukai

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (345)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (74)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- 01 06 ByVention V03 enDokumen166 halaman01 06 ByVention V03 enjeronimost100% (2)

- Atestat EnglezaDokumen16 halamanAtestat EnglezaCosmin CrisBelum ada peringkat

- RX-V3300/DSP-AZ2: Av Receiver/Av AmplifierDokumen128 halamanRX-V3300/DSP-AZ2: Av Receiver/Av Amplifieravreceivertech100% (1)

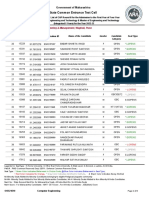

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- Syl RAC Lab KbcnmuDokumen2 halamanSyl RAC Lab Kbcnmunavneet patilBelum ada peringkat

- FDP Program Imr 2023Dokumen2 halamanFDP Program Imr 2023navneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- Specification of Tool Makers MicroscopeDokumen1 halamanSpecification of Tool Makers Microscopenavneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- State Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, PuneDokumen1 halamanState Common Entrance Test Cell: 6155 G.H.Raisoni College of Engineering & Management, Wagholi, Punenavneet patilBelum ada peringkat

- Group Discussion Assessment FormDokumen1 halamanGroup Discussion Assessment Formnavneet patilBelum ada peringkat

- To Print The Entire Project, You Will Choose To Regulate What To Plot A)Dokumen1 halamanTo Print The Entire Project, You Will Choose To Regulate What To Plot A)navneet patilBelum ada peringkat

- Solids HWDokumen2 halamanSolids HWnavneet patilBelum ada peringkat

- Road SafetyDokumen1 halamanRoad Safetynavneet patilBelum ada peringkat

- Rules and Regulations: DivisionsDokumen2 halamanRules and Regulations: Divisionsnavneet patilBelum ada peringkat

- Fabrication of Pneumatic Polishing Hammer: S.S.B.T. C.O.E.T. JalgaonDokumen1 halamanFabrication of Pneumatic Polishing Hammer: S.S.B.T. C.O.E.T. Jalgaonnavneet patilBelum ada peringkat

- Assignment 1Dokumen2 halamanAssignment 1navneet patilBelum ada peringkat

- Introduction To Mechanical Engineering & Engineering Drawing LabDokumen2 halamanIntroduction To Mechanical Engineering & Engineering Drawing Labnavneet patilBelum ada peringkat

- Faq of Module 2Dokumen1 halamanFaq of Module 2navneet patilBelum ada peringkat

- IMEED NMU SyllabusDokumen3 halamanIMEED NMU Syllabusnavneet patilBelum ada peringkat

- Kre1052503 - 9 (Odv-065r15m18jj-G)Dokumen2 halamanKre1052503 - 9 (Odv-065r15m18jj-G)Jŕ MaiaBelum ada peringkat

- Frendx. ,,, ,,., I: ISSN 0160 - 1989Dokumen60 halamanFrendx. ,,, ,,., I: ISSN 0160 - 1989Kasi XswlBelum ada peringkat

- Raspberry Pi BScIT Practicals ManualDokumen64 halamanRaspberry Pi BScIT Practicals ManualSancheetBelum ada peringkat

- Arduino-Based Automatic Sliding Door DesignDokumen8 halamanArduino-Based Automatic Sliding Door DesignNizar Noer InsanBelum ada peringkat

- Radio PillDokumen41 halamanRadio PillAadhithya Priya100% (2)

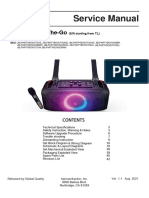

- JBL Partybox OnthegoDokumen42 halamanJBL Partybox Onthegovs674584Belum ada peringkat

- HBXX-3319DS-VTM - HBXX-3319DS-A2M: General SpecificationsDokumen4 halamanHBXX-3319DS-VTM - HBXX-3319DS-A2M: General SpecificationsakiselBelum ada peringkat

- Vacuum&SemiconDokumen96 halamanVacuum&Semiconcajaro100% (1)

- TB6560 ManualDokumen2 halamanTB6560 ManualEmerson Luiz BusnelloBelum ada peringkat

- KPI ExportDokumen153 halamanKPI ExportnandijBelum ada peringkat

- Computer Organization and Assembly Language: Laboratory ManualDokumen25 halamanComputer Organization and Assembly Language: Laboratory ManualMohd ShahBelum ada peringkat

- Tutorial Guide For PICsDokumen27 halamanTutorial Guide For PICsJose Smith100% (1)

- Kick NEKXA Buds Z10 User ManualDokumen1 halamanKick NEKXA Buds Z10 User ManualllaonunBelum ada peringkat

- A+ Guide To Hardware, 4eDokumen62 halamanA+ Guide To Hardware, 4eepriyaa100% (4)

- Experiment 3 Duran ZanderDokumen8 halamanExperiment 3 Duran ZanderFreos VinciBelum ada peringkat

- Siklu DS EtherHaul 8010FX PDFDokumen2 halamanSiklu DS EtherHaul 8010FX PDFJosé MoralesBelum ada peringkat

- Samplechapter 2018080110032088Dokumen25 halamanSamplechapter 2018080110032088MasoudBelum ada peringkat

- X299 Series Memory QVL 20200526Dokumen10 halamanX299 Series Memory QVL 20200526johndillbakersfieldBelum ada peringkat

- Samsung 713bm 913bm Plus CH Ls17plm Ls19plmDokumen34 halamanSamsung 713bm 913bm Plus CH Ls17plm Ls19plmCristian Valentin0% (1)

- Module 5 - Digital Techniques Electronic Instrument Systems PDFDokumen42 halamanModule 5 - Digital Techniques Electronic Instrument Systems PDFanilmathew244Belum ada peringkat

- Y Series Changeover Motorswitch: Automatic Transfer UnitDokumen2 halamanY Series Changeover Motorswitch: Automatic Transfer UnitDuda CorrêaBelum ada peringkat

- Hygrolab: Bench Top Humidity Temperature Indicator Instruction Manual V2.0Dokumen42 halamanHygrolab: Bench Top Humidity Temperature Indicator Instruction Manual V2.0Angel Luis AmadorBelum ada peringkat

- Grundig E100 Shortwave Radio ManualDokumen102 halamanGrundig E100 Shortwave Radio Manualnaupas007Belum ada peringkat

- Surge Protection Device: Section 2: Technical SpecificationDokumen2 halamanSurge Protection Device: Section 2: Technical SpecificationcRi Society0% (1)

- 2 Information AgeDokumen3 halaman2 Information Agexuxi dulBelum ada peringkat

- Everyday Electronics 1972-02Dokumen60 halamanEveryday Electronics 1972-02Toni TursićBelum ada peringkat

- Astrol AA 10276 001 PDFDokumen9 halamanAstrol AA 10276 001 PDFreza yousefiBelum ada peringkat