Kumpulan Instruksi Atmega 8535

Diunggah oleh

sword of excalibur0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

11 tayangan2 halamanChart avr

Judul Asli

chart-2019

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniChart avr

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

11 tayangan2 halamanKumpulan Instruksi Atmega 8535

Diunggah oleh

sword of excaliburChart avr

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 2

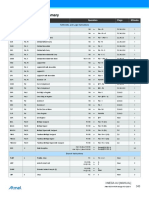

KUMPULAN INSTRUKSI ATMEGA 8535 2019

mnemonic operand Keterangan Operasi (7..0) OP-CODE (7..0) Flag T

Aritmatika dan Logika Univesitas Sanata Dharma

ADD Rd, Rr Add two Reg. Rd ← Rd + Rr 0000 11rd dddd rrrr Z,C,N,V,H 1

ADC Rd, Rr Add two Reg. + C Rd ← Rd + Rr + C 0001 11rd dddd rrrr Z,C,N,V,H 1

ADIW Rdl,K Add Cons. to Word Rdh:Rdl ← Rdh:Rdl + K 1001 0110 KKdd KKKK Z,C,N,V,S 2

SUB Rd, Rr Subtract two Reg. Rd ← Rd - Rr 0001 10rd dddd rrrr Z,C,N,V,H 1

SUBI Rd, K Subtract Cons. from Reg. Rd ← Rd - K 0001 KKKK dddd KKKK Z,C,N,V,H 1

SBC Rd, Rr Subtract two Reg. - C Rd ← Rd - Rr - C 0000 10rd dddd rrrr Z,C,N,V,H 1

SBCI Rd, K Subtract Cons. from Reg. - C Rd ← Rd - K - C 0100 KKKK dddd KKKK Z,C,N,V,H 1

SBIW Rdl,K Subtract Cons. from Word Rdh:Rdl ← Rdh:Rdl - K 1001 0111 KKdd KKKK Z,C,N,V,S 2

AND Rd, Rr Logical AND Reg. Rd ← Rd • Rr 0010 00rd dddd rrrr Z,N,V 1

ANDI Rd, K Logical AND Reg. and Cons. Rd ← Rd • K 0111 KKKK dddd KKKK Z,N,V 1

OR Rd, Rr Logical OR Reg. Rd ← Rd v Rr 0010 10rd dddd rrrr Z,N,V 1

ORI Rd, K Logical OR Reg. and Cons. Rd ← Rd v K 0110 KKKK dddd KKKK Z,N,V 1

EOR Rd, Rr Exclusive OR Reg. Rd ← Rd ⊕ Rr 0010 01rd dddd rrrr Z,N,V 1

COM Rd One’s Complement Rd ← 0xFF − Rd 1001 010d dddd 0000 Z,C,N,V 1

NEG Rd Two’s Complement Rd ← 0x00 − Rd 1001 010d dddd 0001 Z,C,N,V,H 1

SBR Rd,K Set Bit(s) in Reg. Rd ← Rd v K 0110 KKKK dddd KKKK Z,N,V 1

CBR Rd,K Clear Bit(s) in Reg. Rd ← Rd • (0xFF - K) 0111 KKKK dddd KKKK Z,N,V 1

INC Rd Increment Rd ← Rd + 1 1001 010d dddd 0011 Z,N,V 1

DEC Rd Decrement Rd ← Rd − 1 1001 010d dddd 1010 Z,N,V 1

TST Rd Test for Zero or Minus Rd ← Rd • Rd 0010 00dd dddd dddd Z,N,V 1

CLR Rd Clear Reg. Rd ← Rd ⊕ Rd 1001 01dd dddd dddd Z,N,V 1

SER Rd Set Reg. Rd ← 0xFF 1110 1111 dddd 1111 None 1

MUL Rd, Rr Multiply Unsigned R1:R0 ← Rd x Rr 1001 11rd dddd rrrr Z,C 2

MULS Rd, Rr Multiply Signed R1:R0 ← Rd x Rr 0000 0010 dddd rrrr Z,C 2

MULSU Rd, Rr Mul. Signed with Unsigned R1:R0 ← Rd x Rr 0000 0011 0ddd 0rrr Z,C 2

FMUL Rd, Rr Fractional Mul. Unsigned R1:R0 ← (Rd x Rr) << 1 0000 0011 0ddd 1rrr Z,C 2

FMULS Rd, Rr Fractional Mul. Signed R1:R0 ← (Rd x Rr) << 1 0000 0011 0ddd 0rrr Z,C 2

FMULSU Rd, Rr Fractional Mul. Signed (Un) R1:R0 ← (Rd x Rr) << 1 0000 0011 1ddd 1rrr Z,C 2

Transfer Data SANATA DHARMA - YOGYAKARTA - 2019 TJN

MOV Rd, Rr Move Between Reg. Rd ← Rr 0010 11rd dddd rrrr None 1

MOVW Rd, Rr Copy Reg. Word Rd+1:Rd ← Rr+1:R 0000 0001 dddd rrrr None 1

LDI Rd, K Load Cons. Rd ← K 1110 KKKK dddd KKKK None 1

LD Rd, X Load Indirect Rd ← (X) 1001 000d dddd 1100 None 2

LD Rd, X+ Load Indirect and Post-Inc. Rd ← (X), X ← X + 1 1001 000d dddd 1101 None 2

LD Rd, - X Load Indirect and Pre-Dec. X ← X - 1, Rd ← (X) 1001 000d dddd 1110 None 2

LD Rd, Y Load Indirect Rd ← (Y) 1001 000d dddd 1000 None 2

LD Rd, Y+ Load Indirect and Post-Inc. Rd ← (Y), Y ← Y + 1 1001 000d dddd 1001 None 2

LD Rd, - Y Load Indirect and Pre-Dec. Y ← Y - 1, Rd ← (Y) 1001 000d dddd 1010 None 2

LDD Rd,Y+q Load Indirect with Disp. Rd ← (Y + q) 10q0 qq0d dddd 1qqq None 2

LD Rd, Z Load Indirect Rd ← (Z) 1001 000d dddd 0000 None 2

LD Rd, Z+ Load Indirect and Post-Inc. Rd ← (Z), Z ← Z+1 1001 000d dddd 0001 None 2

LD Rd, -Z Load Indirect and Pre-Dec. Z ← Z - 1, Rd ← (Z) 1001 000d dddd 0010 None 2

LDD Rd, Z+q Load Indirect with Disp. Rd ← (Z + q) 10q0 qq0d dddd 0qqq None 2

LDS Rd, k Load Direct from SRAM Rd ← (k) 1001 000d dddd 0000 None 2

ST X, Rr Store Indirect (X) ← Rr 1001 001r rrrr 1100 None 2

ST X+, Rr Store Indirect and Post-Inc. (X) ← Rr, X ← X + 1 1001 001r rrrr 1101 None 2

ST -X, Rr Store Indirect and Pre-Dec. X ← X - 1, (X) ← Rr 1001 001r rrrr 1110 None 2

ST Y, Rr Store Indirect (Y) ← Rr 1000 001r rrrr 1000 None 2

ST Y+, Rr Store Indirect and Post-Inc. (Y) ← Rr, Y ← Y + 1 1001 001r rrrr 1001 None 2

ST -Y, Rr Store Indirect and Pre-Dec. Y ← Y - 1, (Y) ← Rr 1001 001r rrrr 1010 None 2

STD Y+q,Rr Store Indirect with Disp. (Y + q) ← Rr 10q0 qq1r rrrr 1qqq None 2

ST Z, Rr Store Indirect (Z) ← Rr 1000 001r rrrr 0000 None 2

ST Z+, Rr Store Indirect and Post-Inc. (Z) ← Rr, Z ← Z + 1 1001 001r rrrr 0001 None 2

ST -Z, Rr Store Indirect and Pre-Dec. Z ← Z - 1, (Z) ← Rr 1001 001r rrrr 0010 None 2

STD Z+q,Rr Store Indirect with Disp. (Z + q) ← Rr 10q0 qq1r rrrr 0qqq None 2

STS k, Rr Store Direct to SRAM (k) ← Rr 1001 001d dddd 0000 None 2

LPM Load Program Memory R0 ← (Z) 1001 0101 1100 1000 None 3

LPM Rd, Z Load Program Memory Rd ← (Z) 1001 000d dddd 0100 None 3

LPM Rd, Z+ Load Prog Mem and Post-Inc Rd ← (Z), Z ← Z+1 1001 000d dddd 0101 None 3

SPM Store Program Memory (Z) ← R1:R0 1001 0101 1110 1000 None -

IN Rd, P In Port Rd ← P 1011 0AAd dddd AAAA None 1

OUT P, Rr Out Port P ← Rr 1011 1AAr rrrr AAAA None 1

PUSH Rr Push Reg. on Stack STACK ← Rr 1001 001d dddd 1111 None 2

POP Rd Pop Reg. from Stack Rd ← STACK 1001 000d dddd 1111 None 2

mnemonic operand Keterangan Operasi (7..0) OP-CODE (7..0) Flag T

Percabangan Universitas Sanata Dharma 2019

RJMP k Relative Jump PC ← PC + k + 1 1100 kkkk kkkk kkkk None 2

IJMP Indirect Jump to (Z) PC ← Z 1001 0100 0000 1001 None 2

RCALL k Relative Subroutine Call PC ← PC + k + 1 1101 kkkk kkkk kkkk None 3

ICALL Indirect Call to (Z) PC ← Z 1001 0101 0000 1001 None 3

RET Subroutine Return PC ← STACK 1001 0101 0000 1000 None 4

RETI Interrupt Return PC ← STACK 1001 0101 0001 1000 I 4

CPSE Rd,Rr Compare, Skip if Equal if (Rd = Rr) PC ← PC + 2 or 3 0000 00rd dddd rrrr None 1/2/3

CP Rd,Rr Compare Rd − Rr 0001 01rd dddd rrrr Z, N,V,C,H 1

CPC Rd,Rr Compare with C Rd − Rr − C 0000 01rd dddd rrrr Z, N,V,C,H 1

CPI Rd,K Compare Reg. with Cons. Rd − K 0011 KKKK dddd KKKK Z, N,V,C,H 1

SBRC Rr, b Skip if Bit in Reg. = 0 if (Rr(b)=0) PC ← PC + 2 or 3 1111 110r rrrr 0bbb None 1/2/3

SBRS Rr, b Skip if Bit in Reg. = 1 if (Rr(b)=1) PC ← PC + 2 or 3 1111 111r rrrr 0bbb None 1/2/3

SBIC P, b Skip if Bit in I/O Reg. = 0 if (P(b)=0) PC ← PC + 2 or 3 1001 1001 AAAA Abbb None 1/2/3

SBIS P, b Skip if Bit in I/O Reg. = 1 if (P(b)=1) PC ← PC + 2 or 3 1001 1011 AAAA Abbb None 1/2/3

BRBS s, k Branch if S = 1 if (S = 1), PC ← PC + k + 1 1111 00kk kkkk ksss None 1/2

BRBC s, k Branch if S = 0 if (S = 0), PC ← PC + k + 1 1111 01kk kkkk ksss None 1/2

BREQ k Branch if Z = 1 if (Z = 1), PC ← PC + k + 1 1111 00kk kkkk k001 None 1/2

BRNE k Branch if Z = 0 if (Z = 0), PC ← PC + k + 1 1111 01kk kkkk k001 None 1/2

BRCS k Branch if C = 1 if (C = 1), PC ← PC + k + 1 1111 00kk kkkk k000 None 1/2

BRCC k Branch if C = 0 if (C = 0), PC ← PC + k + 1 1111 01kk kkkk k000 None 1/2

BRSH k Branch if C = 0 if (C = 0), PC ← PC + k + 1 1111 01kk kkkk k000 None 1/2

BRLO k Branch if C = 1 if (C = 1), PC ← PC + k + 1 1111 00kk kkkk k000 None 1/2

BRMI k Branch if N = 1 if (N = 1), PC ← PC + k + 1 1111 00kk kkkk k010 None 1/2

BRPL k Branch if N = 0 if (N = 0), PC ← PC + k + 1 1111 01kk kkkk k010 None 1/2

BRGE k Branch if ≥ , Signed if (N ⊕ V= 0), PC ← PC + k + 1 1111 01kk kkkk k100 None 1/2

BRLT k Branch if Less than , Signed if (N ⊕ V= 1), PC ← PC + k + 1 1111 00kk kkkk k100 None 1/2

BRHS k Branch if H = 1 if (H = 1), PC ← PC + k + 1 1111 00kk kkkk k101 None 1/2

BRHC k Branch if H = 0 if (H = 0), PC ← PC + k + 1 1111 01kk kkkk k101 None 1/2

BRTS k Branch if T = 1 if (T = 1), PC ← PC + k + 1 1111 00kk kkkk k110 None 1/2

BRTC k Branch if T = 0 if (T = 0), PC ← PC + k + 1 1111 01kk kkkk k110 None 1/2

BRVS k Branch if V = 1 if (V = 1), PC ← PC + k + 1 1111 00kk kkkk k011 None 1/2

BRVC k Branch if V = 9 if (V = 0), PC ← PC + k + 1 1111 01kk kkkk k011 None 1/2

BRIE k Branch if I = 1 if ( I = 1), PC ← PC + k + 1 1111 00kk kkkk k111 None 1/2

BRID k Branch if I = 0 if ( I = 0), PC ← PC + k + 1 1111 01kk kkkk k111 None 1/2

Bit dan Tes Bit SANATA DHARMA - YOGYAKARTA - 2019 TJN

SBI P,b Set Bit in I/O Reg. I/O(P,b) ← 1 1001 1010 AAAA Abbb None 2

CBI P,b Clear Bit in I/O Reg. I/O(P,b) ← 0 1001 1000 AAAA Abbb None 2

LSL Rd Logical Shift Left ← 0000 11dd dddd dddd Z,C,N,V 1

LSR Rd Logical Shift Right → 1001 010d dddd 0110 Z,C,N,V 1

ROL Rd Rotate Left Through Cy ← 0001 11dd dddd dddd Z,C,N,V 1

ROR Rd Rotate Right Through Cy → 1001 010d dddd 0111 Z,C,N,V 1

ASR Rd Arithmetic Shift Right → 1001 010d dddd 0101 Z,C,N,V 1

SWAP Rd Swap Nibbles Rd(7..4)↔Rd(3..0) 1001 010d dddd 0010 None 1

BSET s Flag Set SREG(s) ← 1 1001 0100 0sss 1000 SREG(s) 1

BCLR s Flag Clear SREG(s) ← 0 1001 0100 1sss 1000 SREG(s) 1

BST Rr, b Bit Store from Reg. to T T ← Rr(b) 1111 101d dddd 0bbb T 1

BLD Rd, b Bit load from T to Reg. Rd(b) ← T 1111 100d dddd 0bbb None 1

SEC Set Carry C←1 1001 0100 0000 1000 C 1

CLC Clear Carry C←0 1001 0100 1000 1000 C 1

SEN N=1 N←1 1001 0100 0010 1000 N 1

CLN N=0 N←0 1001 0100 1010 1000 N 1

SEZ Z=1 Z←1 1001 0100 0001 1000 Z 1

CLZ Z=0 Z←0 1001 0100 1001 1000 Z 1

SEI I=1 I←1 1001 0100 0111 1000 I 1

CLI I=0 I←0 1001 0100 1111 1000 I 1

SES S=1 S←1 1001 0100 0100 1000 S 1

CLS S=0 S←0 1001 0100 1100 1000 S 1

SEV V=1 V←1 1001 0100 0011 1000 V 1

CLV V=0 V←0 1001 0100 1011 1000 V 1

SET T=1 T←1 1001 0100 0110 1000 T 1

CLT T=0 T←0 1001 0100 1110 1000 T 1

SEH H=1 H←1 1001 0100 0101 1000 H 1

CLH H=0 H←0 1001 0100 1101 1000 H 1

Kendali MCU

NOP No Operation 0000 0000 0000 0000 None 1

SLEEP Sleep (Sleep function) 1001 0101 1000 1000 None 1

WDR Watchdog Reset (WDR/Timer) 1001 0101 1010 1000 None 1

BREAK Break For On-chip Debug Only None

Anda mungkin juga menyukai

- Instruções Arduino UNODokumen4 halamanInstruções Arduino UNOLeonardo AlvesBelum ada peringkat

- AtmelDokumen4 halamanAtmelBaba YagaBelum ada peringkat

- Hoja Examen AVRDokumen3 halamanHoja Examen AVRIceyBelum ada peringkat

- Instruction Set Summary: Mnemonics Operands Description Operation Flags #ClocksDokumen3 halamanInstruction Set Summary: Mnemonics Operands Description Operation Flags #ClocksWalter Tintaya QuispeBelum ada peringkat

- Set Instrucciones PDFDokumen3 halamanSet Instrucciones PDFdatazo infoBelum ada peringkat

- Atmega32 Instruction Set SummaryDokumen3 halamanAtmega32 Instruction Set SummaryNumo BamiBelum ada peringkat

- AVR Instructions Set SummaryDokumen5 halamanAVR Instructions Set SummaryChicowolfBelum ada peringkat

- ATmega328P - Instruction Set SummaryDokumen4 halamanATmega328P - Instruction Set SummaryE&GBelum ada peringkat

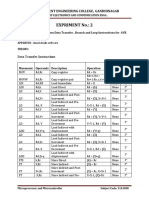

- Expriment No.: 2: Government Engineering College, GandhinagarDokumen10 halamanExpriment No.: 2: Government Engineering College, GandhinagarDhrumil ManiyarBelum ada peringkat

- Instruction SetDokumen1 halamanInstruction Setmakerlog200Belum ada peringkat

- Experiment No.: 3: PC With Atmel StudioDokumen11 halamanExperiment No.: 3: PC With Atmel StudioDhrumil ManiyarBelum ada peringkat

- AVR Instructions 1Dokumen133 halamanAVR Instructions 1Mlondo Khanyisani EmmanuelBelum ada peringkat

- Compare Signed Unsigned: BEQ BEQ ! BNE BNE BGT BHI BGE BHS BLT BLO BLE BLSDokumen3 halamanCompare Signed Unsigned: BEQ BEQ ! BNE BNE BGT BHI BGE BHS BLT BLO BLE BLSEmre CakmakyurduBelum ada peringkat

- 1AVR Juego de Instrucciones ResumidoDokumen2 halaman1AVR Juego de Instrucciones ResumidoLuis Alfonso Martinez FdezBelum ada peringkat

- Instrucciones de Carga Y AlmacenamientoDokumen3 halamanInstrucciones de Carga Y AlmacenamientoTonantzin GuerreroBelum ada peringkat

- LC320Instructions 144663026Dokumen16 halamanLC320Instructions 144663026Đức KhánhBelum ada peringkat

- Ebook - Atmel Avr AssemblerDokumen20 halamanEbook - Atmel Avr AssemblerTim OnnixBelum ada peringkat

- ATmega16 ATmega32Dokumen9 halamanATmega16 ATmega32binitdubeyBelum ada peringkat

- Instr Set PDFDokumen150 halamanInstr Set PDFvannybowoooBelum ada peringkat

- AVR Instruction Set SummaryDokumen4 halamanAVR Instruction Set SummarySinan PravadaliogluBelum ada peringkat

- Chapter 4 Arithmetic and Logic ARMDokumen31 halamanChapter 4 Arithmetic and Logic ARMzakariaBelum ada peringkat

- Cortex M4: Set de Instrucciones BásicoDokumen2 halamanCortex M4: Set de Instrucciones BásicoQuique MoralesBelum ada peringkat

- Basic Laws - Delta-Wye and Source TransformationDokumen24 halamanBasic Laws - Delta-Wye and Source TransformationSTACEYLEEN CYENTHIA LADIUN BK22110177Belum ada peringkat

- PC PC: PC+ 4+se (Imm 2) RT Field, Bits 20-16: Floating Point Instructions (FR Format, Even Regs Only)Dokumen1 halamanPC PC: PC+ 4+se (Imm 2) RT Field, Bits 20-16: Floating Point Instructions (FR Format, Even Regs Only)Hamza AsimBelum ada peringkat

- 7.1.6 Binkhorst Rumus: IOL FORMULA: Outline of IOL FormulaDokumen17 halaman7.1.6 Binkhorst Rumus: IOL FORMULA: Outline of IOL FormulaLevina RiskiBelum ada peringkat

- I1 + RR - RJ: 2D.1 Rolling-Ball ViscometerDokumen1 halamanI1 + RR - RJ: 2D.1 Rolling-Ball ViscometerArsal MaqboolBelum ada peringkat

- RS-485 Tech NoteDokumen21 halamanRS-485 Tech NoteAshley Sequeira100% (3)

- ARM® and Thumb®-2 Instruction Set Quick Reference CardDokumen6 halamanARM® and Thumb®-2 Instruction Set Quick Reference CardpavankrishnatBelum ada peringkat

- Atmega32 Instruction SetInstructon Set SummaryDokumen2 halamanAtmega32 Instruction SetInstructon Set SummaryRajsekhar NagBelum ada peringkat

- AVR Exam Sheets V5.1-1Dokumen12 halamanAVR Exam Sheets V5.1-1nancyrazzak5Belum ada peringkat

- Cao U3Dokumen3 halamanCao U3vilasvairagade02Belum ada peringkat

- Commands in AVR-assembler LanguageDokumen1 halamanCommands in AVR-assembler LanguageFrutzBelum ada peringkat

- Nevehilo PDFDokumen4 halamanNevehilo PDFpolo motoBelum ada peringkat

- Instrumentation Amplifier ProofDokumen3 halamanInstrumentation Amplifier Proofchester_cun100% (2)

- Atmel 0856 Avr Instruction Set ManualDokumen9 halamanAtmel 0856 Avr Instruction Set ManualGabriel Alejandro Francisco Gallardo TineoBelum ada peringkat

- Detailed SolutionsDokumen76 halamanDetailed SolutionsDuppalapudi SainadhBelum ada peringkat

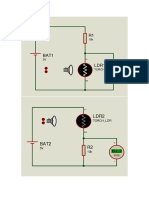

- Torch - LDR: VoltsDokumen3 halamanTorch - LDR: VoltsjeimssBelum ada peringkat

- EEC 140B: MOSFTE: Modern DevicesDokumen18 halamanEEC 140B: MOSFTE: Modern DevicesGerardo SanchezBelum ada peringkat

- Momentum Balance - L9 To L10 Version1Dokumen21 halamanMomentum Balance - L9 To L10 Version1Suhani SinghBelum ada peringkat

- Topic 5 Arithmetic & Logic Instruction (ISMAIL - FKEUTM 2018)Dokumen54 halamanTopic 5 Arithmetic & Logic Instruction (ISMAIL - FKEUTM 2018)Aya AmirBelum ada peringkat

- DC Analysi1Dokumen2 halamanDC Analysi1NanaBelum ada peringkat

- Lab 3Dokumen5 halamanLab 3Lina Rodriguez GamboaBelum ada peringkat

- LOAD COMBINATIONS (NSCP 2015 - 7th Edition)Dokumen4 halamanLOAD COMBINATIONS (NSCP 2015 - 7th Edition)Jes AbinalBelum ada peringkat

- Keling 4030 CNC WiringDokumen1 halamanKeling 4030 CNC WiringkairotdfBelum ada peringkat

- Road Covertable 2Dokumen18 halamanRoad Covertable 2AbhuMagliquianGumbocBelum ada peringkat

- Issues: RenderingDokumen32 halamanIssues: RenderingAshutosh ShuklaBelum ada peringkat

- Rotation by ComponentsDokumen4 halamanRotation by Componentstarek mahmoudBelum ada peringkat

- EE 508 Lect 19 Fall 2020Dokumen47 halamanEE 508 Lect 19 Fall 2020Sai KiranBelum ada peringkat

- Distance Protection Part 3Dokumen93 halamanDistance Protection Part 3Homer Simp67% (3)

- RISC-V Reference CardDokumen2 halamanRISC-V Reference CardTeresinha TeixeiraBelum ada peringkat

- Flow of A Film On The Outside of A Circular TubeDokumen6 halamanFlow of A Film On The Outside of A Circular TubeShubh100% (6)

- Field Description: WD Destination Register Select: 0000 W0 1111 W15Dokumen8 halamanField Description: WD Destination Register Select: 0000 W0 1111 W15Juan Pablo PeñaBelum ada peringkat

- Electric FieldDokumen27 halamanElectric FieldBurak OrsBelum ada peringkat

- ARM Instruction Set Quick Reference Card: Key To TablesDokumen3 halamanARM Instruction Set Quick Reference Card: Key To Tablesashley2009Belum ada peringkat

- SAP-1 Simple As Possible Computer With Microcoded ROMDokumen1 halamanSAP-1 Simple As Possible Computer With Microcoded ROMpong74lsBelum ada peringkat

- GATE Questions On MOSFET, CMOS & Introduction To VLSI (1987 Till Date)Dokumen15 halamanGATE Questions On MOSFET, CMOS & Introduction To VLSI (1987 Till Date)APBelum ada peringkat

- AMD Embedded SolutionsDokumen10 halamanAMD Embedded SolutionsKevin TateBelum ada peringkat

- A Processor Is An Integrated Electronic Circuit That Performs The Calculations That Run A ComputerDokumen2 halamanA Processor Is An Integrated Electronic Circuit That Performs The Calculations That Run A ComputerCyril Ang-numbaalaBelum ada peringkat

- CHKCPUDokumen8 halamanCHKCPUnakamaaBelum ada peringkat

- Semiconductor KIA7905F/PI KIA7924F/PI: Technical DataDokumen16 halamanSemiconductor KIA7905F/PI KIA7924F/PI: Technical DataNathan VeRaBelum ada peringkat

- CH02 Assignment 2Dokumen5 halamanCH02 Assignment 2Nidit ShahBelum ada peringkat

- Projects Need To Upload Online. Use The Standard Format. Use Any EDA Tool For The SimulationDokumen2 halamanProjects Need To Upload Online. Use The Standard Format. Use Any EDA Tool For The SimulationAjay DuranBelum ada peringkat

- Adld l6Dokumen117 halamanAdld l6prasanna prasannaBelum ada peringkat

- Differentiate Microprocessor and Microcontroller. A C203.1 2Dokumen3 halamanDifferentiate Microprocessor and Microcontroller. A C203.1 2kesavantBelum ada peringkat

- Held at E-Force Institute Chandigarh: Hello Electronics Pvt. LimitedDokumen20 halamanHeld at E-Force Institute Chandigarh: Hello Electronics Pvt. LimitedShubham KaushikBelum ada peringkat

- Multi RAM TesterDokumen15 halamanMulti RAM TesterFran MendezBelum ada peringkat

- Embedded Processors - PRELIM - QP - 2017-18Dokumen2 halamanEmbedded Processors - PRELIM - QP - 2017-18harshad lokhandeBelum ada peringkat

- Intel CPU-The Instruction Set ArchitectureDokumen2 halamanIntel CPU-The Instruction Set ArchitecturePauliniBelum ada peringkat

- BHILAI HOUSE, G.E. ROAD, DURG (C.G.) - 491001: Sub Code & Name:328713 (28) Microcontroller & Embedded Systems LabDokumen3 halamanBHILAI HOUSE, G.E. ROAD, DURG (C.G.) - 491001: Sub Code & Name:328713 (28) Microcontroller & Embedded Systems LabYudi JoshiBelum ada peringkat

- FisaDisciplina Bazele Tehnologiei InformatieiDokumen7 halamanFisaDisciplina Bazele Tehnologiei Informatieivesn.popovicBelum ada peringkat

- Ficha Técnica Microchip PIC16F77Dokumen174 halamanFicha Técnica Microchip PIC16F77Leandro Gabriel SantosBelum ada peringkat

- List of Intel Core I5 MicroprocessorsDokumen4 halamanList of Intel Core I5 MicroprocessorsKing 79Belum ada peringkat

- ESD Mid Sem Exam 2019 - KeyDokumen5 halamanESD Mid Sem Exam 2019 - Keyashish6789Belum ada peringkat

- Comparisons of BJT and MOSFETDokumen7 halamanComparisons of BJT and MOSFETFrank WanderiBelum ada peringkat

- The ARM Instruction Set: Advanced RISC MachinesDokumen11 halamanThe ARM Instruction Set: Advanced RISC MachinesGilberto VirgilioBelum ada peringkat

- Please Note That Cypress Is An Infineon Technologies CompanyDokumen16 halamanPlease Note That Cypress Is An Infineon Technologies Company20c552244bBelum ada peringkat

- Gaurav Srivastava Introduction and Work ExperienceDokumen9 halamanGaurav Srivastava Introduction and Work Experiencegauravsri_542631997Belum ada peringkat

- Stick Diagram & Lambda Based Design RulesDokumen21 halamanStick Diagram & Lambda Based Design Rulesbaraniinst6875100% (1)

- Project Review On Design & Implementation of Low Power 32-Bit Risc ProcessorDokumen3 halamanProject Review On Design & Implementation of Low Power 32-Bit Risc ProcessorKedhar MallaBelum ada peringkat

- Eex4436 Assignment 01. 416960756Dokumen18 halamanEex4436 Assignment 01. 416960756RusHan SenavirathnaBelum ada peringkat

- 76xxx Processor Datasheet PDFDokumen10 halaman76xxx Processor Datasheet PDFan nguyenBelum ada peringkat

- Computer OrganisationDokumen12 halamanComputer OrganisationSachuBelum ada peringkat

- Direct Memory Access (DMA)Dokumen7 halamanDirect Memory Access (DMA)Dhivya DharshniBelum ada peringkat

- Report On: "Library Cell Implementation of RHBDDokumen7 halamanReport On: "Library Cell Implementation of RHBDTasmiyaBelum ada peringkat