Sboa 212 A

Diunggah oleh

Gathy BrayohJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Sboa 212 A

Diunggah oleh

Gathy BrayohHak Cipta:

Format Tersedia

Analog Engineer's Circuit: Amplifiers

SBOA212A – January 2018 – Revised January 2019

PWM generator circuit

Design Goals

Input Output Supply

ViMin ViMax VoMin VoMax Vcc Vee Vref

–2.0V 2.0V 0V 5V 5V 0V 2.5V

Design Description

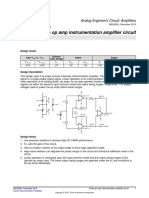

This circuit utilizes a triangle wave generator and comparator to generate a 500 kHz pulse-width-

modulated (PWM) waveform with a duty cycle that is inversely proportional to the input voltage. An op

amp and comparator (U3 and U4) generate a triangle waveform which is applied to the inverting input of a

second comparator (U2). The input voltage is applied to the non-inverting input of U2. By comparing the

input waveform to the triangle wave, a PWM waveform is produced. U2 is placed in the feedback loop of

an error amplifier (U1) to improve the accuracy and linearity of the output waveform.

Error Amplifier Comparator Triangle Wave Generator

C3 100p

R4 10k

R7 5.9k

-

C1 100p

Vsin U3 OPA365

Vcc +

+

R3 10k

- Vref

Vcc

U1 OPA365 ++

+

+

+ U2 TLV3501 Vo

Vi -

Vref

Vcc Vtri

Vref V1 -

+ U4 TLV3501

+

R1 10k

Vcc

R2 10k

C2 100n

R6 10k R5 8.45k

Design Notes

1. Use a comparator with push-pull output and minimal propagation delay.

2. Use an op amp with sufficient slew rate, GBW, and voltage output swing.

3. Place the pole created by C1 below the switching frequency and well above the audio range.

4. Vref must be low impedance (for example, output of an op amp).

SBOA212A – January 2018 – Revised January 2019 PWM generator circuit 1

Submit Documentation Feedback

Copyright © 2018–2019, Texas Instruments Incorporated

www.ti.com

Design Steps

1. Set the error amplifier inverting signal gain.

2. Determine R1 and R2 to divide Vref to cancel the non-inverting gain.

3. The amplitude of Vtri must be chosen such that it is greater than the maximum amplitude of Vi (2.0V) to

avoid 0% or 100% duty cycle in the PWM output signal. Select Vtri to be 2.1V. The amplitude of V1 =

2.5V.

4. Set the oscillation frequency to 500kHz.

5. Choose C1 to limit amplifier bandwidth to below switching frequency.

6. Select C2 to filter noise from Vref.

2 PWM generator circuit SBOA212A – January 2018 – Revised January 2019

Submit Documentation Feedback

Copyright © 2018–2019, Texas Instruments Incorporated

www.ti.com

Design Simulations

DC Simulation Results

T 5.0

4.5

4.0

3.5

3.0

Output

2.5

2.0

1.5

1.0

500.0m

0.0

-2.0 -1.0 0.0 1.0 2.0

Input voltage (V)

Transient Simulation Results

T 2.0

1.0

VIN 0.0

-1.0

-2.0

5.0

Vout 2.5

0.0

50.0u 60.0u 70.0u 80.0u 90.0u 100.0u

Time (s)

SBOA212A – January 2018 – Revised January 2019 PWM generator circuit 3

Submit Documentation Feedback

Copyright © 2018–2019, Texas Instruments Incorporated

www.ti.com

Design References

See Analog Engineer's Circuit Cookbooks for TI's comprehensive circuit library.

See circuit SPICE simulation file SBOC502.

See TIPD108, www.ti.com/tool/tipd108

Design Featured Op Amp

OPA2365

Vss 2.2V to 5.5V

VinCM Rail-to-rail

Vout Rail-to-rail

Vos 100µV

Iq 4.6mA

Ib 2pA

UGBW 50MHz

SR 25V/µs

#Channels 2

www.ti.com/product/opa2365

Design Comparator

TLV3502

Vss 2.2V to 5.5V

VinCM Rail-to-rail

Vout Rail-to-rail

Vos 1mV

Iq 3.2mA

Ib 2pA

UGBW -

SR -

#Channels 2

www.ti.com/product/tlv3502

Design Alternate Op Amp

OPA2353

Vss 2.7V to 5.5V

VinCM Rail-to-rail

Vout Rail-to-rail

Vos 3mV

Iq 5.2mA

Ib 0.5pA

UGBW 44MHz

SR 22V/µs

#Channels 2

www.ti.com/product/opa2353

Revision History

Revision Date Change

A January 2019 Downscale the title and changed title role to 'Amplifiers'.

Added link to circuit cookbook landing page.

4 PWM generator circuit SBOA212A – January 2018 – Revised January 2019

Submit Documentation Feedback

Copyright © 2018–2019, Texas Instruments Incorporated

IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE

DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES “AS IS”

AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY

IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD

PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate

TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable

standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you

permission to use these resources only for development of an application that uses the TI products described in the resource. Other

reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third

party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims,

damages, costs, losses, and liabilities arising out of your use of these resources.

TI’s products are provided subject to TI’s Terms of Sale (www.ti.com/legal/termsofsale.html) or other applicable terms available either on

ti.com or provided in conjunction with such TI products. TI’s provision of these resources does not expand or otherwise alter TI’s applicable

warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265

Copyright © 2019, Texas Instruments Incorporated

Anda mungkin juga menyukai

- Opamp TIDokumen5 halamanOpamp TIAmogh Gajaré100% (1)

- ECP 2 ReportDokumen2 halamanECP 2 ReportDejvis dishiBelum ada peringkat

- CDV700Pro Construction Tutorial PDFDokumen33 halamanCDV700Pro Construction Tutorial PDFjuan9gonzalez_9Belum ada peringkat

- Sboa 247Dokumen5 halamanSboa 247Surafel DestawBelum ada peringkat

- Fixed Point FFT Circuit and LayoutDokumen1 halamanFixed Point FFT Circuit and LayoutAlexe VictorBelum ada peringkat

- Adjustable Reference Voltage CircuitDokumen4 halamanAdjustable Reference Voltage CircuitThieplo BertolaBelum ada peringkat

- DB203 Basic Comp-Limiter Design THAT4305Dokumen6 halamanDB203 Basic Comp-Limiter Design THAT4305bruno magalhãesBelum ada peringkat

- Microphone Preamplifier Circuit DiagramDokumen1 halamanMicrophone Preamplifier Circuit DiagramSigg KeyoBelum ada peringkat

- SSM 2120 Nivel Detector dn126Dokumen8 halamanSSM 2120 Nivel Detector dn126Edson Francisco SilvaBelum ada peringkat

- Sboa 221 ADokumen4 halamanSboa 221 Anupoorhit2126Belum ada peringkat

- That Corporation Grsign Note 109Dokumen2 halamanThat Corporation Grsign Note 109Anonymous Wyb8Y10% (1)

- 68-Watt Audio Power AmplifierDokumen1 halaman68-Watt Audio Power AmplifierGábor BaloghBelum ada peringkat

- Acom 1011 Service ManualDokumen40 halamanAcom 1011 Service ManualHubert JoriskesBelum ada peringkat

- Service Information Service Information: WWW - Laney.co - UkDokumen3 halamanService Information Service Information: WWW - Laney.co - UkCarlos Cárdenas BarbaBelum ada peringkat

- Operational AmplifierDokumen46 halamanOperational AmplifierhajjkaBelum ada peringkat

- DodcompDokumen1 halamanDodcompPablo EspinosaBelum ada peringkat

- U1 (V+) U2 (V+) : AC VoltsDokumen2 halamanU1 (V+) U2 (V+) : AC VoltsPeter Giancarlo Ramirez TantaBelum ada peringkat

- KNR1723 2122Tutorial02SolutionwrewrweDokumen18 halamanKNR1723 2122Tutorial02SolutionwrewrweSebastianBelum ada peringkat

- Laney Lg12 SMDokumen3 halamanLaney Lg12 SMJavier RojasBelum ada peringkat

- Voltage Controlled Oscillator V3340D/M: 1. General DescriptionDokumen5 halamanVoltage Controlled Oscillator V3340D/M: 1. General DescriptionCarlos SulcaBelum ada peringkat

- High Voltage Shunt RegulatorDokumen1 halamanHigh Voltage Shunt RegulatorHertanto Setiawan Phunsuk WangduBelum ada peringkat

- A Low-Cost VCA Limiter: THAT Corporation Design Note 129Dokumen5 halamanA Low-Cost VCA Limiter: THAT Corporation Design Note 129Edson Francisco SilvaBelum ada peringkat

- 900W Regulated Power Amplifier SMPS Circuit DiagramDokumen1 halaman900W Regulated Power Amplifier SMPS Circuit DiagramSirJones Kekapoh100% (1)

- Current Source 20mADokumen4 halamanCurrent Source 20mAlingarajsahuBelum ada peringkat

- Eecs412 Lab1Dokumen4 halamanEecs412 Lab1Josué TriveñoBelum ada peringkat

- Bal869anced 976y o I68ponput v.1bDokumen1 halamanBal869anced 976y o I68ponput v.1bmdeky20Belum ada peringkat

- ECHOFEX SchematicDokumen1 halamanECHOFEX SchematicHristoIlievBelum ada peringkat

- sboa325Dokumen6 halamansboa325abhishek tiwariBelum ada peringkat

- Analog Sample and Hold Circuit Uses Just 6 DevicesDokumen5 halamanAnalog Sample and Hold Circuit Uses Just 6 Devicesmaddy13rocksBelum ada peringkat

- Utc 2030Dokumen14 halamanUtc 2030Jose M PeresBelum ada peringkat

- Funcionamiento Simplificado V90Dokumen2 halamanFuncionamiento Simplificado V90Antonio ValdebenitoBelum ada peringkat

- DIY Naim MC To MM Mod Sch2Dokumen1 halamanDIY Naim MC To MM Mod Sch2tubetymeBelum ada peringkat

- Mi21mtech11003 - BM5023 - 2021 - Lab 2Dokumen7 halamanMi21mtech11003 - BM5023 - 2021 - Lab 2Subhranil RoyBelum ada peringkat

- Elektor Attiny NoiseDokumen2 halamanElektor Attiny NoiseKlemensKohlweisBelum ada peringkat

- Xotic BB Preamp Andy Timmons - SchematicDokumen1 halamanXotic BB Preamp Andy Timmons - SchematicDavid Brown100% (1)

- Slurat9 28600Dokumen2 halamanSlurat9 28600jay lowkeyBelum ada peringkat

- Helix Electrical Package RevB 9-7-16Dokumen95 halamanHelix Electrical Package RevB 9-7-16casual divertidoBelum ada peringkat

- Micro Terror JFETDokumen1 halamanMicro Terror JFETwalterdadaBelum ada peringkat

- 22k audio taper mod for guitar amp preampDokumen4 halaman22k audio taper mod for guitar amp preampedi spenkBelum ada peringkat

- High-End Preamp With ECC88 (Schematic-1)Dokumen1 halamanHigh-End Preamp With ECC88 (Schematic-1)BIỂN NGUYỄN QUỐCBelum ada peringkat

- Sboa 268 ADokumen5 halamanSboa 268 AtimotheemokumaBelum ada peringkat

- High Power Factor Power DesignDokumen8 halamanHigh Power Factor Power DesignnutwutBelum ada peringkat

- H2PToday2207 Design Innovatia Part5Dokumen9 halamanH2PToday2207 Design Innovatia Part5juanBelum ada peringkat

- Dual Mic Pre Schematic - SSM2017-Based, But INA217 & THAT1510 Are Possible Subs - Kevin Ross Celestial - ComauDokumen1 halamanDual Mic Pre Schematic - SSM2017-Based, But INA217 & THAT1510 Are Possible Subs - Kevin Ross Celestial - ComaucrackintheshatBelum ada peringkat

- 15:25VA Dual Power SupplyDokumen1 halaman15:25VA Dual Power Supplynd2b8f4djmBelum ada peringkat

- 750wrms 2 Ohms 77v Supply Audio Power Amp I 6 Rlva FG 750wrms Ls2 2013 Rev 1Dokumen1 halaman750wrms 2 Ohms 77v Supply Audio Power Amp I 6 Rlva FG 750wrms Ls2 2013 Rev 1Mond Timpog LagmanBelum ada peringkat

- Flyback transformer specification and circuit diagramDokumen2 halamanFlyback transformer specification and circuit diagramRodrigoBelum ada peringkat

- UNI-750-1 Schematic 5V-AUX - D PDFDokumen1 halamanUNI-750-1 Schematic 5V-AUX - D PDFNelson Orjuela100% (1)

- GC-20 SchematicDokumen1 halamanGC-20 SchematicPetr BruzaBelum ada peringkat

- LDR01Dokumen1 halamanLDR01Luis RodríguezBelum ada peringkat

- Skilling DocumentDokumen10 halamanSkilling DocumentMLM TELUGU GAMERSBelum ada peringkat

- Roland Funny Cat SchematicDokumen4 halamanRoland Funny Cat SchematicGustavoTfLa100% (1)

- Eq2 DriverDokumen1 halamanEq2 Driverjuanmb1Belum ada peringkat

- 2do ParcialDokumen13 halaman2do ParcialJhan KanamaBelum ada peringkat

- WWW - Iranswitching.Ir: Ac/Dc Switch Mode Power Supply Design GuideDokumen2 halamanWWW - Iranswitching.Ir: Ac/Dc Switch Mode Power Supply Design GuidedraBelum ada peringkat

- Simulation of Adc and Dac Circuits - E3Dokumen6 halamanSimulation of Adc and Dac Circuits - E3Carlos GamioBelum ada peringkat

- Experiment Title: Study of Operational Amplifier As Precision Rectifier ObjectiveDokumen2 halamanExperiment Title: Study of Operational Amplifier As Precision Rectifier ObjectiveAaa AaaBelum ada peringkat

- Semiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsDari EverandSemiconductor Data Book: Characteristics of approx. 10,000 Transistors, FETs, UJTs, Diodes, Rectifiers, Optical Semiconductors, Triacs and SCRsBelum ada peringkat

- Zeros and Poles Transfer FunctionsDokumen158 halamanZeros and Poles Transfer FunctionsGathy BrayohBelum ada peringkat

- .MX Claroline Backends DownloadDokumen4 halaman.MX Claroline Backends DownloadHeriberto EspinosaBelum ada peringkat

- Cpa 296552 PDFDokumen2 halamanCpa 296552 PDFGathy BrayohBelum ada peringkat

- Mathhw9 SolnDokumen2 halamanMathhw9 SolnGathy BrayohBelum ada peringkat

- C13 1 CovDokumen3 halamanC13 1 CovGathy BrayohBelum ada peringkat

- MTDC REFsDokumen8 halamanMTDC REFsGathy BrayohBelum ada peringkat

- E1asoln Ece302 sp06Dokumen8 halamanE1asoln Ece302 sp06Gathy BrayohBelum ada peringkat

- 451 Exercise451 - Rev - S18Dokumen2 halaman451 Exercise451 - Rev - S18Gathy BrayohBelum ada peringkat

- Wave Guides Summary and ProblemsDokumen11 halamanWave Guides Summary and ProblemsGathy BrayohBelum ada peringkat

- Design and Implementation of Chopper-Stabilized AmplifiersDokumen2 halamanDesign and Implementation of Chopper-Stabilized AmplifiersGathy BrayohBelum ada peringkat

- Finance Department Finance InternDokumen1 halamanFinance Department Finance InternGathy BrayohBelum ada peringkat

- SpaceDokumen3 halamanSpaceGathy BrayohBelum ada peringkat

- Web Development Quotation: What About It?Dokumen4 halamanWeb Development Quotation: What About It?Gathy BrayohBelum ada peringkat

- K. Cheng,: Is ofDokumen2 halamanK. Cheng,: Is ofGathy BrayohBelum ada peringkat

- Example DocumentDokumen18 halamanExample DocumentGathy BrayohBelum ada peringkat

- Audience Data: Age and Gender SplitDokumen23 halamanAudience Data: Age and Gender SplitGathy BrayohBelum ada peringkat

- .MX Claroline Backends DownloadDokumen4 halaman.MX Claroline Backends DownloadHeriberto EspinosaBelum ada peringkat

- Course Structure Diploma in ITDokumen1 halamanCourse Structure Diploma in ITGathy BrayohBelum ada peringkat

- CCC502 Course OutlineDokumen3 halamanCCC502 Course OutlineGathy BrayohBelum ada peringkat

- Induction Motor Chapter: Stator Resistance, Speed, Torque CalculationsDokumen5 halamanInduction Motor Chapter: Stator Resistance, Speed, Torque CalculationsGathy BrayohBelum ada peringkat

- Distortionless Transmission Line TheoryDokumen7 halamanDistortionless Transmission Line TheoryGathy BrayohBelum ada peringkat

- Machine Copy For Proofreading, Vol. X, Y-Z, 2004Dokumen23 halamanMachine Copy For Proofreading, Vol. X, Y-Z, 2004Gathy BrayohBelum ada peringkat

- ELG3311: Assignment 3: Problem 6-12Dokumen15 halamanELG3311: Assignment 3: Problem 6-12Gathy BrayohBelum ada peringkat

- Statement: Google AdwordsDokumen2 halamanStatement: Google AdwordsGathy BrayohBelum ada peringkat

- TLDokumen16 halamanTLMannanHarshaBelum ada peringkat

- 4th Year Control Lab 1Dokumen3 halaman4th Year Control Lab 1Gathy BrayohBelum ada peringkat

- C13 1 CovDokumen3 halamanC13 1 CovGathy BrayohBelum ada peringkat

- Lab 1Dokumen26 halamanLab 1Gathy BrayohBelum ada peringkat

- VSD Pumps Best PracticeDokumen48 halamanVSD Pumps Best PracticebeechyBelum ada peringkat

- Multiple Choice QuestionsDokumen35 halamanMultiple Choice QuestionsAnonymous WAIDC7m3kxBelum ada peringkat

- Nova-M: Technical Data SheetDokumen2 halamanNova-M: Technical Data SheetparaboolBelum ada peringkat

- Telecommunications Engineering II by Jorma KekalainenDokumen608 halamanTelecommunications Engineering II by Jorma KekalainenJorma KekalainenBelum ada peringkat

- 1.LTE QoS From E2E Solution PerspectiveDokumen47 halaman1.LTE QoS From E2E Solution Perspectivecollinsg123100% (1)

- 2017 Summer Model Answer Paper PDFDokumen36 halaman2017 Summer Model Answer Paper PDFGordon lyonBelum ada peringkat

- XTENDAccess FlexiDokumen4 halamanXTENDAccess FlexiAli RazaBelum ada peringkat

- Gigabit Interface Converter (GBIC) Module and Small Form-Factor Pluggable (SFP) GBIC Module Installation Information and SpecificationsDokumen22 halamanGigabit Interface Converter (GBIC) Module and Small Form-Factor Pluggable (SFP) GBIC Module Installation Information and SpecificationsAdrian OprisanBelum ada peringkat

- CV3PX308R1Dokumen5 halamanCV3PX308R1AlejandroPortuguezTapiaBelum ada peringkat

- ABR202ADokumen2 halamanABR202AwolfdeniroBelum ada peringkat

- S-Wave U-65-18DV10-B4 - DEDokumen2 halamanS-Wave U-65-18DV10-B4 - DENymiterBelum ada peringkat

- Dipole Antenna ProblemsDokumen3 halamanDipole Antenna ProblemsRawasy TarhuniBelum ada peringkat

- Estimation, Filtering and Adaptive ProcessesDokumen135 halamanEstimation, Filtering and Adaptive Processesmehdicheraghi506Belum ada peringkat

- Enhancement Performance Tapered Slot Vivaldi Antenna For Weather Radar ApplicationDokumen4 halamanEnhancement Performance Tapered Slot Vivaldi Antenna For Weather Radar ApplicationayhaynglawuBelum ada peringkat

- CCNP Course at GlanceDokumen4 halamanCCNP Course at GlanceWILLEBelum ada peringkat

- Wireless MCQsDokumen73 halamanWireless MCQsSalma AkterBelum ada peringkat

- Appendix A: Electromagnetic Compatibility GuidanceDokumen4 halamanAppendix A: Electromagnetic Compatibility GuidanceAleksandar BerberBelum ada peringkat

- Linear Control Systems CourseDokumen2 halamanLinear Control Systems CourseBehzad SamadiBelum ada peringkat

- Com4 Satellite Communications ReviewersDokumen6 halamanCom4 Satellite Communications ReviewersKristine Ella BaduriaBelum ada peringkat

- LMMLDokumen7 halamanLMMLFrancisco Javier Bandarra BandarraBelum ada peringkat

- TC-268S/368S: Professional Two-Way RadioDokumen2 halamanTC-268S/368S: Professional Two-Way Radioijundi100% (1)

- Ericsson Switch 6391 DatasheetDokumen2 halamanEricsson Switch 6391 Datasheetkjlhgj dfBelum ada peringkat

- Nokia Siemens Network SRA 4 PDFDokumen5 halamanNokia Siemens Network SRA 4 PDFnovendra tobingBelum ada peringkat

- Lte Signal ProcessingDokumen15 halamanLte Signal ProcessingranazainBelum ada peringkat

- Data Sheet Amplificador AudioDokumen8 halamanData Sheet Amplificador AudiosebasvBelum ada peringkat

- Quantization NoiseDokumen18 halamanQuantization NoiseHernán Damián Duy RomeroBelum ada peringkat

- Datasheet UltrasonikDokumen2 halamanDatasheet UltrasonikAnthony TaylorBelum ada peringkat

- CompressionDokumen38 halamanCompressionShivani Goel100% (1)

- Antenna 742224Dokumen2 halamanAntenna 742224rezwan2kBelum ada peringkat

- Huij Sing 1985Dokumen7 halamanHuij Sing 1985Charles EcheverríaBelum ada peringkat

- DSP Assignment Sheet 1Dokumen2 halamanDSP Assignment Sheet 1gaurav maithaniBelum ada peringkat