Modul Praktikum Rangkaian Digital

Diunggah oleh

Rolandoganda SihombingHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Modul Praktikum Rangkaian Digital

Diunggah oleh

Rolandoganda SihombingHak Cipta:

Format Tersedia

MODUL I

GERBANG DASAR

A. Maksud dan Tujuan

Maksud : Memperkenalkan gerbang-gerbang dasar kepada para praktikan.

Tujuan : Praktikan dapat mengetahui komponen penyusun gerbang nalar dalam teori

sistem digital, serta dapat menyusun untai digital sederhana.

B. Teori

1. Komponen dasar sistem digital.

Untai digital pada taraf awal adalah relay dan saklar. Operasi dari saklar atau relay dapat

dilihat dengan mudahnya hakekatnya yang bersifat biner; ini berarti saklar bisa dalam

keadaan on (1) atau off (0). Untai digital modern saat ini adalah transistor, dimana

transistor pada suatu saat dapat bekerja (on=1) atau tidak bekerja (off=0) tergantung

dari kendali basisnya.

2. Sistem bilangan

Seperti yang telah diuraikan di atas, maka komponen digital hanya terdiri dari dua

buah nilai yaitu nilai on (1) dan off (0). Angka 0 desimal jika dilambangkan dengan

bilangan biner adalah bernilai 0, angka 1 desimal dilambangkan dengan 1, angka 2

desimal dilambangkan dengan 10, angka 3 dilambangkan dengan 11, begitu seterusnya.

3.Opreasi bilangan biner

Operasi dasar bilangan biner meliputi operasi AND (perkalian) yang dilambangkan

dengan tanda titik (.), OR (penjumlahan) yang dilambangkan dengan tanda plus (+),

NOT(pembalik) yang dilambangkan dengan tanda minus (-) atau tanda strip diatas nilai

yang akan dibalik, dan pengembangannya operasi NOR yang terdiri atas untai OR dan

NOT, operasi NAND yang terdiri atas untai AND yang digabungkan dengan NOT.

Selain itu juga ada operasi XOR (Exclusive OR) yang merupakan modifikasi dari

gerbang OR.

Gerbang AND

Gambar Gerbang AND 2 masukan :

Gerbang AND adalah suatu untai digital yang mempunyai beberapa masukan dan

sebuah keluaran. Definisi gerbang AND adalah keluaran akan bernilai 1 jika semua

masukan bernilai 1.

Gerbang OR

Gambar Gerbang OR 2 masukan

A

Y

B

Gerbang OR adalah suatu untai digital yang mempunyai beberapa masukan dan

sebuah keluaran. Definisi gerbang OR adalah keluaran akan bernilai 0 jika semua

masukan bernilai 0, atau dengan kata lain jika salah satu atau beberapa atau semua

masukan bernilai 1 maka keluaran akan bernilai 1.

Gerbang NOT

Petunjuk Praktikum Rangkaian Digital TK-D3 1

Gambar Gerbang NOT

A Y

Gerbang NOT atau yang sering disebut inverter atau pembalik adalah suatu

untai digital yang mempunyai sebuah masukan dan sebuah keluaran. Definisi

gerbang NOT adalah keluaran akan merupakan kebalikan dari masukannya.

Gerbang XOR

Gambar Gerbang XOR

A

B Y

Gerbang XOR adalah suatu untai digital yang mempunyai dua masukan dan

sebuah keluaran. Definisi gerbang OR adalah keluaran akan bernilai 0 jika kedua

nilai sama nilainya ( 0 semua atau 1 semua) dan akan bernilai 1 jika kedua

masukan tidak bernilai sama.

Gerbang NAND

Gambar Gerbang NAND 2 masukan

A

Y

B

Gerbang NAND akan merupakan gabungan dari gerbang AND dan gerbang NOT,

dimana hasil keluaran gerbang AND akan disambungkan dengan gerbang NOT,

keluaran gerbang NOT inilah yang menjadi keluaran gerbang NAND.

Gerbang NOR

Gambar Gerbang NOR 2 masukan

A

Y

B

Gerbang NOR akan merupakan gabungan dari gerbang NOR dan gerbang NOT,

dimana hasil keluaran gerbang OR akan disambungkan dengan gerbang NOT,

keluaran gerbang NOT inilah yang menjadi keluaran gerbang NOR.

B. Soal

1. Susunlah dan amatilah gerbang nalar berikut ini beserta tabel kebenarannya :

a. gerbang OR

b. gerbang AND

c. gerbang NOT

d. gerbang NOR

e. gerbang NAND

2. Susunlah dan amatilah untai-untai di bawah ini beserta tabel kebenarannya :

a. untai NOT dengan menggunakan gerbang NOR

b. untai NOT dengan menggunakan gerbang NAND

c. untai NOR tiga masukan dengan menggunakan tiga buah untai NOR 2 masukan

d. untai NAND tiga masukan dengan menggunakan tiga buah untai NAND 2 masukan.

Petunjuk Praktikum Rangkaian Digital TK-D3 2

3. Susunlah dan amatilah untai XOR dibawah ini berserta tabel kebenarannya.

a. gerbang XOR

b. persamaan XOR, Y = A B = (A + B) . (A . B)

c. persamaan XOR, Y = A B = (A . B) + (A . B)

d. persamaan XOR, Y = A B = (A . B) + (A . B)

e. persamaan XOR, Y = A B = (A + B) . (A + B)

Keterangan :

1. Masukan gerbang dihubungkan dengan Saklar biner.

2. Keluaran gerbang dihubungkan dengan penampil LED.

Petunjuk Praktikum Rangkaian Digital TK-D3 3

PRAKTIKUM RANGKAIAN DIGITAL

MODUL I. Gerbang Dasar

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1.a. Gerbang OR Tabel kebenaran

A B Y=A+ B

0 0

0 1

1 0

1 1

Simbol gerbang OR

Jenis IC OR yang digunakan : SN ........

1.b. Gerbang AND Tabel kebenaran

A B Y=A. B

0 0

0 1

1 0

1 1

Simbol gerbang AND

Jenis IC AND yang digunakan : SN ........

1.c. Gerbang NOT Tabel kebenaran

A Y=A

0

1

Simbol gerbang NOT

Jenis IC AND yang digunakan : SN ........

1.d. Gerbang NOR Tabel kebenaran

A B Y=A+ B

0 0

0 1

1 0

Simbol gerbang NOR 1 1

Jenis IC NOR yang digunakan : SN ........

1.e. Gerbang NAND Tabel kebenaran

A B Y=A. B

0 0

0 1

1 0

1 1

Simbol gerbang NAND

Jenis IC NAND yang digunakan : SN ........

2.a. Untai NOT dengan menggunakan gerbang NOR

Gambar untai Tabel kebenaran

Petunjuk Praktikum Rangkaian Digital TK-D3 4

A Y=A

0

1

2.b. Untai NOT dengan menggunakan gerbang NAND

Gambar untai Tabel kebenaran

A Y=A

0

1

2.c. Untai NOR tiga masukan dengan menggunakan tiga buah untai

NOR dua masukan.

A B C Y=A+B+C

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Gambar untai

2.d. Untai NAND tiga masukan dengan menggunakan tiga buah untai

NAND dua masukan.

A B C Y=A.B.C

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

Gambar untai

MODUL II

UNTAI PENJUMLAHAN DAN PENGURANGAN

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan untai penjumlahan dan pengurangan kepada para

praktikan.

Petunjuk Praktikum Rangkaian Digital TK-D3 5

2. Tujuan : Praktikan dapat mengetahui dan menyusun untai penjumlahan Half

Adder, Full Adder, Untai penjumlahan 2-bit, Untai penjumlahan dan

pengurangan 8-bit.

B. Teori

Dalam sistem digital dikenal beberapa untai penjumlahan (addder), antara lain adalah

untai penjumlah setengah (half adder), untai penjumlah penuh (full adder), untai

penjumlah biner sejajar.

1. Untai penjumlah setengah (half adder)

Untai penjumlah setengah (half adder) adalah suatu untai yang terdiri atas dua buah

masukan (bilangan yang akan dijumlahkan) dan dua buah keluaran terdiri atas hasil

penjumlahan (s) dan hasil bawaan (luapan = carry = c). Untuk menyusun untai half

adder ini digunakan gerbang-gerbang dasar yang telah dipraktikkan pada modul

sebelumnya.

Untuk lebih jelasnya dapat dilihat pada gambar di bawah ini :

A B A : Terminal masukan

B : Terminal keluaran

A dan B adalah bilangan yang dijumlahkan

HA

S : Hasil penjumlahan

C : Hasil bawaan (luapan/carry)

S C S =A B

C =A. B

2. Untai penjumlah penuh (full adder)

Untai penjumlah penuh (full adder) adalah suatu untai yang terdiri atas tiga buah

masukan dan dua buah keluaran.

Masukan terdiri atas dua buah bilangan yang akan dijumlahkan dan sebuah luapan yang

berasal dari full adder sebelumnya.

Keluaran terdiri atas sebuah hasil penjumlahan (s) dan hasil bawaan (luapan = carry = c).

Untuk menyusun untai full adder ini digunakan gerbang-gerbang dasar yang telah

dipraktikkan pada modul sebelumnya.

Untuk lebih jelasnya dapat dilihat pada gambar di bawah ini :

An Bn Cn-1 An : Terminal masukan

Bn : Terminal keluaran

Cn-1 : Luapan dari full adder sebelumnya

An dan Bn adalah bilangan yang dijumlahkan

Sn : Hasil penjumlahan

Cn : Hasil luapan (bawaan / carry)

Sn = (An Bn) Cn-1

FA

Sn Cn Cn = (An Bn). Cn-1 + (An . Bn)

3. Untai penjumlah sejajar

Untai penjumlah sejajar ini adalah merupakan pengembangan dari untai full adder yang

telah dibahas sebelumnya. Penyusunan dari untai penjumlah sejajar tersebut adalah

sebagai berikut :

Petunjuk Praktikum Rangkaian Digital TK-D3 6

Jika diinginkan suatu untai yang dapat berfungsi sebagai penjumlahan dan

pengurangan, maka perlu ditambahkan lagi untai EXOR pada masing-masing kaki

input bilangan B. Untuk lebih jelasnya dapat dilihat pada gambar di bawah ini :

Jika akan digunakan sebagai untai penjumlahan maka "Sub" diberi nilai 0 (dihubungkan

dengan Ground), jika akan digunakan sebagai untai pengurangan maka "Sub" diberi

nilai 1 (dihubungkan dengan Vcc), dimana A adalah bilangan yang akan dikurangi

bilangan B.

D. Soal

1. Buatlah untai half adder dengan menggunakan gerbang EXOR dan gerbang AND

dengan persamaan di bawah. Buatlah gambar untainya dan juga tabel hasil penjumlahan.

A dan B adalah bilangan yang akan dijumlahkan

S adalah hasil penjumlahan

C adalah luapan

Persamaan :

S =A B

C =A. B

2. Buatlah untai full adder dengan menggunakan gerbang EXOR dan gerbang AND,

gerbang OR dengan persamaan di bawah. Buatlah gambar untainya dan juga tabel hasil

penjumlahan.

An dan Bn adalah bilangan yang akan dijumlahkan

Cn-1 adalah luapan dari full adder sebelumnya

Sn adalah hasil penjumlahan

Cn adalah luapan

Persamaan :

Sn = (An Bn) Cn-1

Cn = ((An Bn) . Cn-1) + (An . Bn)

3. Buatlah untai penjumlahan 2-bit biner dengan menggunakan dua buah untai full

adder. Buatlah gambar untainya dan juga tabel hasil penjumlahan. Gambar untainya

adalah sebagai berikut :

Petunjuk Praktikum Rangkaian Digital TK-D3 7

4. Buatlah untai penjumlahan dan pengurangan 8-bit biner dengan menggunakan dua

buah untai full adder 4-bit. Untai tersebut dapat digunakan untuk penjumlahan dan

pengurangan, dimana A adalah bilangan pertama dan B adalah bilangan kedua.

Buatlah gambar untainya dan juga tabel hasilnya untuk berbagai contoh bilangan

yang akan dijumlahkan atau dikurangkan (buatlah masing masing 5 buah).

Gambar untainya adalah sebagai berikut:

Keterangan :

1. Jalur masukan dihubungkan dengan saklar biner

2. Untuk soal 1-3, jalur keluaran dihubungkan dengan penampil LED

3. Untuk soal 4, keluaran dihubungkan dengan penampil 7-segmen.

Petunjuk Praktikum Rangkaian Digital TK-D3 8

PRAKTIKUM RANGKAIAN DIGITAL

MODUL II. Penjumlahan dan Pengurangan

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1. Untai Half Adder

Gambar Untai Tabel Kebenaran

A B S C

0 0

0 1

1 0

1 1

2. Full Adder

Gambar Untai Tabel Kebenaran

An Bn Cn-1 Sn Cn

0 0 0

0 0 1

0 1 0

0 1 1

1 0 0

1 0 1

1 1 0

1 1 1

3. Penjumlahan 2-bit

Gambar Untai Tabel Kebenaran

A1 A0 B1 B0 C1 S1 S0

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

4. Penjumlahan dan Pengurangan 8-bit

Petunjuk Praktikum Rangkaian Digital TK-D3 9

Gambar Untai

Pengamatan Hasil Penjumlahan

Bilangan A Bilangan B Tampilan

8 7 6 5 4 3 2 1 Nil 8 7 6 5 4 3 2 1 Nil Hasil

Pengamatan Hasil Pengurangan

Bilangan A Bilangan B Tampilan

8 7 6 5 4 3 2 1 Nil 8 7 6 5 4 3 2 1 Nil Hasil

MODUL III

UNTAI LATCH

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan untai Latch kepada kepada para praktikan.

2. Tujuan : Praktikan dapat mengetahui fungsi untai Latch dan menyusun untai Latch

dengan berbagai macam untai Latch.

B. Teori

Peranti dasar yang dipakai dalam operasional atau bagian penghitung komputer digital

adalah gerbang-gerbang dan peranti yang disebut flip-flop. Flip-flop menyiapkan

Petunjuk Praktikum Rangkaian Digital TK-D3 10

memori dan gerbang menyiapkan operasi atau fungsi dari harga variabel yang tersimpan

dalam peranti memori ini.

1. Flip-Flop

Rangkaian dasar yang digunakan untuk menyimpan informasi disebut flip-flop.

Karakteristik flip-flop adalah sebagai berikut :

a. Flip-flop merupakan peranti yang dwimantap, yaitu rangkaian yang memiliki

dua keadaan yang diberi simbol keadaan 0 dan 1. Rangkaian flip-flop dapat

menyimpan 1 bit biner dari informasi karena sifatnya yang dwimantap. Flip-

flop menanggapi masukannya. Jika suatu masukan menyebabkannya

berpindah ke keadaan 1, peranti itu akan tetap dalam keadaan itu dan

"mengingatnya" sebagai 1 sampai signal lainnya menyebabkannya. Demikian

juga sebaliknya jika suatu masukan menyebabkannya berpindah ke keadaan 0,

peranti itu akan tetap dalam keadaan itu dan "mengingatnya" sebagai 0 sampai

signal lainnya menyebabkannya. Sifat dasar ini, yaitu mempertahankan

keadaannya merupakan dasar penyimpanan informasi dalam bagian

pengoperasian atau penghitungan suatu komputer digital.

b. Flip-flop mempunyai dua signal keluaran, yang satu merupakan komplemen dari

yang lainnya. Gambar 3.1. menunjukkan diagram blok suatu jenis flip-flop,

yaitu flip-flop RS. Terdapat dua masukan yaitu S (set) dan R (reset), dan dua

buah keluaran yang diberi simbol Q1 dan Q2. Untuk lebih jelasnya dapat dilihat

dalam contoh tabel logika flip-flop RS pada tabel 3.1.

S Q1

Flip-Flop

RS

R Q2

Gambar 3.1. Diagram blok flip-flop RS

Tabel 3.1. Contoh tabel hasil operasi flip-flop RS

S R Q1 Q2 Keterangan

1 0 1 0 Q1 diset 1

0 0 1 0 tidak berubah

0 1 0 1 Q1 direset 0

0 0 0 1 tidak berubah

0 1 0 1 Q1 direset 0

0 0 0 1 tidak berubah

1 0 1 0 Q1 diset 1

0 0 1 0 tidak berubah

0 1 0 1 Q1 direset 0

Catatan :

1. Masukan R dan masukan S pada tabel diatas adalah mempunyai sifat aktif tinggi,

yaitu akan aktif jika diberi nilai 1 dan sebaliknya tidak akan aktif jika diberi nilai 0.

2. Pada jenis flip-flop yang lain ada juga yang bersifat aktif rendah, yaitu akan

aktif jika diberi nilai 0 dan sebaliknya tidak akan aktif jika diberi nilai 1.

Suatu untai flip-flop dapat dibuat dengan menggunakan beberapa gerbang dasar.

Gambar 3.2.a menunjukkan suatu untai Flip-Flop yang dirangkai dengan

menggunakan gerbang NAND dan gambar 3.2.b menunjukkan suatu untai Flip-Flop

yang dirangkai dengan menggunakan gerbang NOR. Sedangkan Tabel 3.2.a

menunjukkan tabel kebenaran Untai Flip-flop yang yang disusun dengan gerbang

NAND dan Tabel 3.2.b menunjukkan tabel kebenaran Untai Flip-flop yang yang

disusun dengan gerbang NOR.

Petunjuk Praktikum Rangkaian Digital TK-D3 11

(a)

(b)

Gambar 3.2. (a) Flip-flop RS dengan NAND

(b) Flip-flop RS dengan NOR

Tabel 3.2. Kebenaran Untai Flip-flop

a. dengan NAND

S R Output Q1

0 0 Tidak Dipakai

0 1 1

1 0 0

1 1 Tidak Berubah

b. dengan gerbang NOR

S R Output Q1

0 0 Tidak Berubah

0 1 1

1 0 0

1 1 Tidak Dipakai

2. Flip-Flop RS tergerbang

Dari uraian yang telah dijelaskan pada bagian sebelumnya, masih terdapat kekurangan dalam

unjuk kerja pada untai flip-flop. Sebagai contoh jika masukan R dan masukan S aktif

dalam waktu yang bersamaan maka akan terdapat keadaan yang tidak diinginkan (keadaan

tidak dipakai).

Untuk mengatasi keadaan yang tidak dipakai inilah dibutuhkan suatu untai tambahan, hal

ini seperti terlihat pada Gambar 3.3.

Untuk lebih jelasnya dapat dilihat pada contoh tabel hasil operasi Flip-flop RS tergerbang

pada tabel 3.3. dibawah ini :

Tabel 3.3. Contoh tabel hasil

Clk A B Q1 Q2 Keterangan

Petunjuk Praktikum Rangkaian Digital TK-D3 12

0 1 0 0 1 keadaan awal

1 1 0 1 0 Q1 diset 1

0 1 1 1 0 tidak berubah

1 0 0 0 1 tidak berubah

0 0 1 0 1 tidak berubah

1 0 1 0 1 Q1 direset

0 0 1 1 0 tidak berubah

1 0 0 0 1 tidak berubah

D. Soal

1. Susunlah untai flip-flop RS dengan menggunakan gerbang NAND, kemudian isikan

hasil pengamatan kedalam tabel yang telah disediakan.

2. Susunlah untai flip-flop RS dengan menggunakan gerbang NOR, kemudian isikan

hasil pengamatan kedalam tabel yang telah disediakan.

3. Susunlah untai flip-flop RS tergerbang dengan menggunakan gerbang NAND,

kemudian isikan hasil pengamatan kedalam tabel yang telah disediakan.

4. Susunlah untai flip-flop RS tergerbang dengan menggunakan gerbang NOR, kemudian

isikan hasil pengamatan kedalam tabel yang telah disediakan.

5. Jawablah pertanyaan di bawah ini dalam laporan sementara :

a. Pada flip-flop input A atau S disebut sebagai SET input, dan input B atau R disebut

sebagai RESET input. Apa sebabnya.

b. Bagaimanakan arah perubahan output Q1 untuk A = B = 0 untuk masing masing jenis

flip-flop RS ?

c. Bagaimanakan arah perubahan output Q1 untuk A = B = 1 untuk masing masing jenis

flip-flop RS ?

d. Bagaimanakah hubungan nalar antara Q1 dan Q2.

e. Pada flip-flop RS tergerbang untuk Clock = 0, bagaimanakah keadaan output untuk

sembarang kombinasi input ?

Petunjuk Praktikum Rangkaian Digital TK-D3 13

PRAKTIKUM RANGKAIAN DIGITAL

MODUL III. Untai Latch atau Flip-flop

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1. Untai flip-flop RS dengan gerbang NAND.

Gambar rangkaian Tabel hasil pengamatan

A B Q1 Q2

0 1

1 1

1 0

1 1

0 1

1 0

0 0

0 1

1 1

2. Untai flip-flop RS dengan gerbang NOR.

Gambar rangkaian Tabel hasil pengamatan

A B Q1 Q2

0 1

1 1

1 0

1 1

0 1

1 0

0 0

0 1

1 1

3. Untai flip-flop RS tergerbang dengan gerbang NAND.

Gambar rangkaian Tabel hasil pengamatan

Clk A B Q1 Q2

0 0 1

1 0 1

0 0 0

1 0 0

0 1 0

1 1 0

0 1 1

1 1 1

4. Untai flip-flop RS tergerbang dengan gerbang NOR.

Gambar rangkaian Tabel hasil pengamatan

Petunjuk Praktikum Rangkaian Digital TK-D3 14

Clk A B Q1 Q2

0 0 1

1 0 1

0 0 0

1 0 0

0 1 0

1 1 0

0 1 1

1 1 1

5. Jawaban soal :

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

………………………………………………………………………………………………..

Petunjuk Praktikum Rangkaian Digital TK-D3 15

MODUL IV

UNTAI DEKODER

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan untai dekoder kepada kepada para praktikan.

2. Tujuan : Praktikan dapat mengetahui fungsi untai dekoder dan menyusun untai

dekoder dengan berbagai macam kombinasinya.

B. Teori

Bagian terpenting dari sistem yang memilih lokasi sel yang akan dibaca atau

ditulisi adalah dekoder. Rangkaian khusus ini disebut dekoder banyak-ke-satu, matriks

dekoder, atau dekoder, dan memiliki karakteristik sedemikian sehingga untuk masing-

masing bilangan masukan biner dari 2 n yang mungkin diambil oleh n-sel masukan, matriks

itu akan mempunyai satu saluran yang unik dari 2n saluran keluaran.

Dalam pelaksanaan praktikum, yang digunakan adalah IC dengan fungsi dekoder

tersebut. Gambar 4.1. menunjukkan diagram kotak IC dekoder 2-bit) dengan masukan 2

buah dan keluaran berjumlah 4 buah, serta sebuah kendali. Hubungan antara masukan dan

keluaran adalah jumlah keluaran merupakan 2 pangkat masukannya (keluaran = 2masukan).

Sebagai contoh jika masukannya 2, maka keluarannya adalah 22 = 4. Tabel 4.1.

menunjukkan hasil keluaran dari dekoder pada gambar 4.1.

Gambar 4.1. Diagram kotak Dekoder 2-bit.

Tabel 4.1. Fungsi keadaan dekoder 4.1

Masukan Keluaran

FE B A Y3 Y2 Y1 Y0

1 x x 1 1 1 1

0 0 0 1 1 1 0

0 0 1 1 1 0 1

0 1 0 1 0 1 1

0 1 1 0 1 1 1

Dari tabel 4.1 dapat dilihat bahwa FE berfungsi sebagai masukan untuk membolehkan

(men-enable) dekoder tersebut bekerja, jika aktif (=0=aktif rendah), maka dekoder baru

memperhatikan masukan A dan B. Jika A=0 dan B=0, maka keluaran Y0 akan aktif

(=0=aktif rendah), demikian seterusnya untuk masukan yang lain dapat dilihat pada tabel

4.1. tersebut.

D. Soal

1. Susunlah untai dekoder 4-bit dengan menggunakan dua dekoder biner 2-bit,

seperti pada gambar dibawah. Amatilah hasil keluarannya, dan isilah pada tabel yang

telah disediakan pada lembar kerja.

Petunjuk Praktikum Rangkaian Digital TK-D3 16

2. Susunlah untai dekoder 10-bit ( yang digunakan hanya 3-bit saja) dengan menggunakan

dekoder biner 3-bit, gerbang NAND 8-masukan, dan beberapa gerbang NOT, seperti

pada gambar di bawah. Amatilah hasil keluarannya, dan isilah pada tabel yang telah

disediakan pada lembar kerja.

Keterangan :

- AEN dan -IOW dihubungkan dengan Ground (aktif rendah).

- Vcc dihubungkan dengan Vcc 5 Volt dari sumber daya.

Petunjuk Praktikum Rangkaian Digital TK-D3 17

PRAKTIKUM RANGKAIAN DIGITAL

MODUL IV.Dekoder

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1. Dekoder 4-bit dengan menggunakan dua buah dekoder 2-bit.

Gambar untai dekoder

Tabel pengamatan :

Masukan Keluaran

D C B A Y3 Y2 Y1 Y0

0 1 X X

1 0 X X

1 1 X X

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

2. Dekoder 10-bit dengan menggunakan dekoder 3-bit, gerbang NAND 8-masukan,

gerbang NOT.

Gambar untai dekoder

Masukan Keluaran

A9 A8 A7 A6 A5 A4 A3 A2 A1 A0 Y7 Y6 Y5 Y4 Y3 Y2 Y1 Y0

1 x x x x x x x x X

0 0 1 1 1 1 1 0 0 0

0 0 1 1 1 1 1 0 0 1

0 0 1 1 1 1 1 0 1 0

0 0 1 1 1 1 1 0 1 1

0 0 1 1 1 1 1 1 0 0

0 0 1 1 1 1 1 1 0 1

0 0 1 1 1 1 1 1 1 0

0 0 1 1 1 1 1 1 1 1

MODUL V

UNTAI PENCACAH

Petunjuk Praktikum Rangkaian Digital TK-D3 18

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan untai pencacah kepada para praktikan.

2. Tujuan : Praktikan dapat mengetahui fungsi untai pencacah dan menyusun untai

pencacah dengan berbagai macam kombinasinya.

B. Teori

Untai pencacah merupakan suatu untai digital yang digunakan untuk mencatat

banyaknya kejadian dari masukan tertentu. Hal ini yang digunakan sebagai dasar dari

pencacahan dan dipakai berulang-ulang. Untuk pengembangan lebih lanjut maka pencacah

dapat berupa pencacah naik atau pencacah turun.

Pencacah naik maksudnya adalah akan menambah nilai cacahan dengan nilai

tertentu jika suatu keadaan menyebabkannya bertambah, demikian juga pencacah turun

adalah akan mengurangi nilai cacahan dengan nilai tertentu jika suatu masukan

menyebabkannya berkurang.

1. Pencacah Biner

Pencacah biner adalah suatu jenis untai pencacah yang nilainya dimulai dari

keadaan 0 pada semua keluaran sampai dengan semua keluaran bernilai 1. Pada saat semua

keluaran bernilai 1 maka untuk keadaan selanjutnya akan mengambil keadaan awalnya,

demikian seterusnya.

Tabel 5.1.a menunjukkan hasil dari untai pencacah naik 3-bit dan tabel 5.1.b

menunjukkan hasil dari untai pencacah turun 3-bit.

Tabel 5.1. pencacah biner 3-bit

a. pencacah naik

Keadaan X2 X1 X0 Nilai Biner

1 0 0 0 0

2 0 0 1 1

3 0 1 0 2

4 0 1 1 3

5 1 0 0 4

6 1 0 1 5

7 1 1 0 6

8 1 1 1 7

9 0 0 0 0

... .. .. .. dan seterusnya

b. pencacah turun

Keadaan X2 X1 X0 Nilai Biner

1 0 0 0 0

2 0 0 1 7

3 0 1 0 6

4 0 1 1 5

5 1 0 0 4

6 1 0 1 3

7 1 1 0 2

8 1 1 1 1

9 0 0 0 0

... .. .. .. dan seterusnya

Untai pencacah dapat dibuat dengan berbagai macam cara, ada yang menggunakan untai

kombinasional antara gerbang-gerbang dasar atau juga sudah ada keping (chip = IC)

khusus yang memang sudah dirancang untuk keperluan pembuatan untai pencacah.

Beberapa untai pencacah akan dibahas dalam teori ini.

Petunjuk Praktikum Rangkaian Digital TK-D3 19

a. Untai Pencacah dengan Flip-flop JK

IC SN 7476 merupakan suatu IC (Integrated Circuit=rangkaian terintegrasi) keluaraga IC

TTL (transistor transistor logic) yang didalamnya terdapat dua buah Flip-flop JK. Untai

flip-flop JK merupakan pengembangan dari untai flip-flop RS. Lebih lanjut dapat dilihat

pada gambar 5.1.

a) b)

Gambar 5.1. Flip flop JK. (a). JK Flip-flop dibentuk dari flip flop RS.

(b). JK flip flop.

Tabel kebenaran dari untai flip-flop tipe JK dapat dilihat pada Tabel 5.1.

Tabel 5.1. Tabel kebenaran flip-flop JK

Masukan Keadaan

J K Berikutnya

0 0 Q1

0 1 0

1 0 1

1 1 Q2

Untai pencacah naik 3-bit dan pencacah turun 3-bit dengan Flip-flop JK adalah seperti

telihat pada gambar 5.2 berikut ini.

Gambar 5.2. Untai pencacah dengan Flip-flop JK

Jika diinginkan membuat untai pencacah naik maka keluaran yang digunakan

(dihubungkan dengan penampil) adalah keluaran dari Q1, demikian juga jika diinginkan

membuat untai pencacah turun maka keluaran yang digunakan (dihubungkan dengan

penampil) adalah keluaran dari Q2.

b. Untai pencacah dengan IC pencacah

Seperti telah disebutkan diatas bahwa terdapat keping (Chip=IC) khusus yang

digunakan untuk pencacah ini. Untuk itu maka akan dibahas komponen IC tersebut,

dalam hal ini adalah IC SN 7493 (pencacah biner). IC ini termasuk dalam keluarga IC

TTL. Gambar 5.3. menunjukkan gambar diagram IC SN 7493 yang digunakan sebagai

pencacah biner.

Petunjuk Praktikum Rangkaian Digital TK-D3 20

Gambar 5.3 Untai pencacah dengan IC SN 7493.

2. Pencacah jangkau tertentu.

Dalam aplikasi yang lain, seringkali diinginkan suatu nilai yang perputaran nilainya pada

nilai tertentu, contohnya suatu pencacah yang nilainya antara 0 sampai dengan 9, atau

nilainya antara 0 sampai dengan 4 (pencacah modulo 5) seperti pada digit menit dan jam

pada suatu jam digital dan lain-lain. Bahkan jika diinginkan suatu pencacah yang nilainya

antara 0 sampai dengan 23 (modulo 24) maka harus dibuat suatu untai pencacah BCD

bertingkat dengan modulo 24.

Untuk lebih memudahkan pembuatan atau perancangan pencacah maka digunakan IC yang

khusus digunakan untuk pencacah yaitu IC SN 7493 (pencacah biner) seperti yang telah

dijelaskan pada bagian sebelumnya dan suatu IC SN 7490 (pencacah BCD atau biner).

Pada perancangan untai pencacah dengan modulo tertentu maka yang harus diperhatikan

adalah pola bit biner dari bilangan tertinggi dari nilai yang bisa dicapai. Selain itu juga

fungsi masing masing kaki IC yang digunakan.

Pada bagian selanjutnya telah dibahas contoh aplikasi IC SN 7493 sebagai pencacah biner.

Kaki R01 dan R02 berfungsi sebagai RESET Counter dihubungkan dengan ground, hal

ini berarti kaki tersebut tidak pernah aktif (karena mempunyai aktif tinggi).

Jika diinginkan suatu pencacah yang mencacah pada jangkauan nilai tertentu saja maka

kaki R01 dan kaki R02 haruslah digunakan.

Contoh : Jika diinginkan suatu pencacah yang berfungsi sebagai pencacah modulo 5,

maka yang diperhatikan adalah pola bit biner 5 adalah 0101 (4-bit). Disini dilihat bahwa bit

ke-0 adalah 1, bit ke-1 adalah 0, bit ke-2 adalah 1, dan bit ke-3 adalah 0. Untuk

mengaktifkan reset counter (aktif tinggi) dapat kita gunakan bit ke-0 dan bit ke-2, oleh

karena itu maka salah satu reset counter dihubungkan dengan bit ke-0 dan reset yang lain

dihubungkan dengan bit ke-2 dari keluaran pencacah (counter).

Gambar untai pencacah modulo 5 adalah sebagai berikut :

Petunjuk Praktikum Rangkaian Digital TK-D3 21

Selanjutnya akan dibahas tentang IC SN 7490 sebagai pencacah BCD. Gambar 5.4.

menunjukkan diagram kotak IC SN 7490. Tabel 5.2. menunjukkan tabel fungsi pencacah

BCD.

Gambar 5.4. Diagram kotak IC SN 7490

Tabel 5.2 Fungsi pencacah BCD SN 7490

Reset Input Output

R01 R02 R91 R92 Qd Qc Qb Qa

H H x L L L L L

H H L x L L L L

x x H H H L L H

x L x L COUNT

L x L x COUNT

L x X L COUNT

x L L x COUNT

Contoh : Susunlah pencacah modulo 24 (nilainya 0 - 23) dengan pencacah BCD 7490.

Gambar untai pencacah modulo 24

D. Soal

1. Susunlah untai pencacah biner dengan flip-flop JK.

a. pencacah naik

b. pencacah turun

2. Susunlah untai pencacah biner dengan IC pencacah biner SN 7493.

3. Susunlah untai pencacah dengan modulo tertentu dengan IC SN 7493.

a. modulo 10

b. modulo 6

4. Susunlah untai pencacah yang berfungsi seperti halnya menit pada suatu jam.

5. Susunlah untai pencacah yang berfungsi seperti halnya kerja suatu jam (menit dan

detik saja).

Petunjuk Praktikum Rangkaian Digital TK-D3 22

PRAKTIKUM RANGKAIAN DIGITAL

MODUL V. Untai Pencacah

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1. Untai pencacah Biner dengan Flip-flop JK

a. pencacah naik

Gambar untai

Hasil pengamatan pada penampil 7-segmen

b. pencacah naik

Gambar untai

Hasil pengamatan pada penampil 7-segmen

2. Untai pencacah Biner dengan IC pencacah

Gambar untai

Hasil pengamatan pada penampil 7-segmen

3. Untai pencacah dengan modulo tertentu

a. modulo 10

Gambar untai

Hasil pengamatan pada penampil 7-segmen

b. modulo 6

Gambar untai

Petunjuk Praktikum Rangkaian Digital TK-D3 23

Hasil pengamatan pada penampil 7-segmen

4. Untai pencacah yang berfungsi sebagai menit

Gambar untai

Hasil pengamatan pada penampil 7-segmen

5. Untai pencacah yang berfungsi menit dan jam

Gambar untai

Hasil pengamatan pada penampil 7-segmen

MODUL VI

APLIKASI LALULINTAS SISTEM DIGITAL

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan salah satu aplikasi sistem digital kepada para praktikan.

Petunjuk Praktikum Rangkaian Digital TK-D3 24

2. Tujuan : Praktikan dapat mengetahui penerapan sistem dalam kehidupan sehari-hari

dan mampu untuk dilaksanakan dalam praktikum.

B. Teori

Salah satu aplikasi sistem digital yang akan dipraktikkan pada modul ini adalah untai

Lampu pengatur lalu lintas pada suatu pemberhentian simpang tiga, seperti telihat pada

gambar 6.1. Pada suatu saat hanya ada kendaraan dari satu arah saja yang diperbolehkan

lewat ke arau tujuan (dari arah A saja atau dari arah B saja).

Dalam aplikasi pada sistem digital nantinya dianggap bahwa kalau lampu hidup maka akan

berlogika atau bernalar 1 dan sebaliknya jika lampu padam maka akan bernalar 0.

Pertama-tama yang perlu diperhatikan adalah pembuatan tabel keadaan lampu lalu lintas

tersebut, seperti terlihat pada tabel 6.1.

Arah A Arah B

m M K H M K H

0 1 0 0 1 0 0

1 0 0 1 1 0 0

2 0 0 1 1 0 0

3 0 1 0 1 0 0

4 1 0 0 1 0 0

5 1 0 0 0 0 1

6 1 0 0 0 0 1

7 1 0 0 0 1 0

Keterangan : M = Merah, K = Kuning, H = Hijau

Dari Tabel tersebut kemudian dibuat peta Karnaugh (dibaca pada buku catatan kuliah)

untuk masing-masing lampu.

Peta Karnaugh untuk arah A

Lampu Merah Lampu Kuning Lampu Hijau

C C C C C C

A.B 1 0 A.B 0 0 A.B 0 1

A.B 0 0 A.B 0 1 A.B 1 0

Petunjuk Praktikum Rangkaian Digital TK-D3 25

A.B 1 1 A.B 0 0 A.B 0 0

A.B 1 1 A.B 0 0 A.B 0 0

Dengan penyederhanaan peta karnaugh di dapat persamaan sebagai berikut :

Y Merah = A + (B . C)

Y Kuning = A.B.C

Y Hijau = A.B.C + A.B.C

Keterangan : Bit A adalah bit MSB, bit C adalah bit LSB.

Peta Karnaugh untuk arah B

Lampu Merah Lampu Kuning Lampu Hijau

C C C C C C

A.B 1 1 A.B 0 0 A.B 0 0

A.B 1 1 A.B 0 0 A.B 0 0

A.B 0 0 A.B 0 1 A.B 1 0

A.B 1 0 A.B 0 0 A.B 0 1

Dengan penyederhanaan peta karnaugh di dapat persamaan sebagai berikut :

Y Merah = A + (B . C)

Y Kuning = A.B.C

Y Hijau = A.B.C + A.B.C

Keterangan : Bit A adalah bit MSB, bit C adalah bit LSB.

Setelah semua rangkaian dibuat, maka sebenarnya kerja dari lampu tersebut hanya

mengulang-ulang keadaan seperti terlihat dalam tabel 6.1 di atas. Sehingga untuk

merealisasikannya dibutuhkan suatu untai pencacah biner 3-bit yang mempunyai keadaan

keluaran sebanyak 8 buah. Gambar 6.2 menunjukkan hubungan antara dekoder lampu

lalu-lintas dengan untai pencacah biner 3-bit.

Petunjuk Praktikum Rangkaian Digital TK-D3 26

Gambar 6.2. Untai Pengatur lampu lalu-lintas simpang tiga.

D. Soal

1. Buatlah untai pengatur lalu-lintas simpang tiga seperti terlihat pada gambar 6.2 di

atas. Gambarlah sekali lagi untai masing-masing dekoder secara lebih detail

berserta untai pencacahnya dan hubungan antara keluaran pencacah (A, B, C)

dengan masukan pada dekoder (A, B, C).

2. Buatlah analisa tentang hasil yang telah anda kerjakan pada saat praktikum pada modul

ini. Buatlah analisa tentang hasil pengamatan sementara. Buatlah juga analisa secara

lebih lengkap pada Laporan resmi.

Petunjuk Praktikum Rangkaian Digital TK-D3 27

PRAKTIKUM RANGKAIAN DIGITAL

MODUL VI. Aplikasi Lalulintas Sistem Digital

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1. Untai pengatur lampu lalu-lintas.

a. Gambar untai secara lengkap.

b. Analisa hasil pengamatan.

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

………………………………………………………………………………………………...

Petunjuk Praktikum Rangkaian Digital TK-D3 28

MODUL VII

MULTIPLEKSER

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan multiplekser kepada para praktikan.

2. Tujuan : Praktikan dapat mengetahui fungsi multiplekser dan berbagai

kombinasinya.

B. Teori

Multiplekser adalah suatu untai digital yang berguna untuk menyalurkan sejumlah n-

masukan ke dalam satu atau dua jalur keluaran dengan mengatur jalur alamat (address)-nya

dan jalur select atau strobe. Gambar 7.1. menunjukkan diagram blok multiplekser 8-kanal

masukan dan 2-kanal output.

Gambar 7.1.

Jalur E0-E7 (8-kanal) adalah jalur masukan digital merupakan data yang akan disalurkan ke

jalur keluaranY, keluaran W merupakan jalur keluaran yang mempunyai nalar berlawanan

dengan jalur Y (W = -Y). Jalur A, B, C merupakan pemilih saluran. Jalur ST atau strobe

digunakan untuk mngendalikan keluaran Y dan W. Untuk lebih jelasnya dapat dilihat pada

tabel kebenaran multiplekser berikut ini:

INPUT OUTPUT

ST C B A Y W

H X X X L H

L L L L E0 -E0

L L L H E1 -E1

L L H L E2 -E2

L L H H E3 -E3

.

.

.

L H H H E7 -E7

Keterangan:

Untuk semua masukan A, B, C bernilai sembarang, jika ST diberikan nilai ‘1’ atau ‘H’ maka

Y akan bernilai ‘0’ atau ‘L’ dan W bernilai ‘1’ atau ‘H’.

C. Percobaan

1. Susunlah untai multiplekser seperti pada Gambar 7.1. Jalur E0 sampai E7 disambungkan

dengan jalur masukan saklar biner. Jalur A, B, C, dan ST disambungkan dengan jalur

Petunjuk Praktikum Rangkaian Digital TK-D3 29

masukan saklar biner. Jalur Y dan W disambungkan dengan penampil LED biner. Amati

hasilnya dan diisikan pada tabel kebenaran yang tersedia pada lembar pengamatan.

D. PERTANYAAN

1. Bagaimana hubungan antara jumlah masukan En terhadap jalur kendali pemilih saluran ?

2. Bagaimanakah cara untuk mendapatkan multiplekser dengan jumlah masukan 16, jika

yang tersedia adalah dua buah multiplekser dengan jumlah masukan 8 ?

PRAKTIKUM RANGKAIAN DIGITAL

MODUL VII. MULTIPLEKSER

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

Petunjuk Praktikum Rangkaian Digital TK-D3 30

1. Pengamatan Multiplekser

a. Gambar Rangkaian

b. Tabel Pengamatan

INPUT OUTPUT

ST C B A Y W

1 X X X

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

Jawaban pertanyaan

1.

............................................................................................................................................

............................................................................................................................................

............................................................................................................................................

............................................................................................................................................

............................................................................................................................................

............................................................................................................................................

2.

............................................................................................................................................

............................................................................................................................................

............................................................................................................................................

............................................................................................................................................

............................................................................................................................................

............................................................................................................................................

MODUL VIII

ENKODER (PENYANDI)

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan enkoder (penyandi) kepada para praktikan.

2. Tujuan : Praktikan dapat mengetahui fungsi enkoder (penyandi) dan berbagai

kombinasinya.

Petunjuk Praktikum Rangkaian Digital TK-D3 31

B. Teori

Enkoder atau penyandi adalah untai digital yang mempunyai fungsi yang berlawanan

dengan untai dekoder. Untai enkoder atau penyandi mempunyai sejumlah masukan yang

pada satu saat hanya ada satu masukan yang boleh aktif. Keluaran enkoder ini adalah bit

jamak terkode yang akan dibangkitkan tergantung pada masukan yang diaktifkan.

Aplikasi enkoder ini misalnya papan ketik yang terdiri atas karakter, angka,

dan karakter khusus yang kira-kira terdiri atas 84 karakter. Setiap karakter

dipilih dengan menekan sebuah tombol pada papan ketik (keyboard),

selanjutnya penyandi akan mengubah setiap masukan ke sandi biner tertentu.

Gambar 8.1. menunjukkan aplikasi enkoder untuk papan ketik atau keyboard.

Gambar 8.1. Aplikasi Enkode untuk keyboard.

Diperlukan sandi 7-bit untuk menyadikan 84 karakter yang ada menjadi kode biner (27 =

128).

Enkoder yang digunakan dalam praktikum adalah jenis 74148, yang mempunyai masukan

sebanyak 8-buah, dan keluaran sebanyak 3-buah. Berikut ini adalah gambar simbol Enkoder

74148.

Tabel Kebenaran Enkoder 74148

INPUT OUTPUT

__ _ _ _ _ _ _ _ _ __ __ __ __ __

EI 0 1 2 3 4 5 6 7 A2 A1 A0 GS EO

H X X X X X X X X H H H H H

L H H H H H H H H H H H H L

L X X X X X X X L L L L L H

L X X X X X X L H L L H L H

L X X X X X L H H L H L L H

L X X X X L H H H L H H L H

Petunjuk Praktikum Rangkaian Digital TK-D3 32

L X X X L H H H H H L L L H

L X X L H H H H H H L H L H

L X L H H H H H H H H L L H

L L H H H H H H H H H H L H

C. Percobaan

1. Susunlah untai enkoder dan amatilah masukan dan keluarannya pada tabel kebenaran.

PRAKTIKUM RANGKAIAN DIGITAL

MODUL VIII. ENKODER

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1. Gambar untai enkoder.

Petunjuk Praktikum Rangkaian Digital TK-D3 33

Tabel Kebenaran Enkoder 74148

INPUT OUTPUT

__ _ _ _ _ _ _ _ _ __ __ __ __ __

EI 0 1 2 3 4 5 6 7 A2 A1 A0 GS EO

H X X X X X X X X …… …… …… …… ……

L H H H H H H H H …… …… …… …… ……

L X X X X X X X L …… …… …… …… ……

L X X X X X X L H …… …… …… …… ……

L X X X X X L H H …… …… …… …… ……

L X X X X L H H H …… …… …… …… ……

L X X X L H H H H …… …… …… …… ……

L X X L H H H H H …… …… …… …… ……

L X L H H H H H H …… …… …… …… ……

L L H H H H H H H …… …… …… …… ……

MODUL IX

PEMBANDING (KOMPARATOR) DIGITAL

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan untai pembanding kepada para praktikan.

2. Tujuan : Praktikan dapat mengetahui fungsi untai pembanding dan berbagai

kombinasinya.

B. Teori

Pengertian mendasar dari pembanding atau comparator adalah membandingkan suatu

data dengan data yang lain. Besarnya data dapat bervariasi asalkan keduanya mempunyai

besaran yang sama (misalnya volt dengan volt, bilangan biner 1-bit dengan bilangan biner

1-bit, bilangan biner 2-bit dengan bilangan biner 2-bit, dan lain-lain). Pembahasan lebih

lanjut dalam praktikum ini adalah untai pembanding data biner.

Petunjuk Praktikum Rangkaian Digital TK-D3 34

1. Pembanding 1-bit

Pembanding 1-bit adalah membandingkan 1-bit data dengan 1-bit data lainya. Tabel

berikut ini menunjukkan tabel kebenaran untai pembanding 1-bit.

A B Fungsi 1 Fungsi 2

0 0 0 1

0 1 1 0

1 0 1 0

1 1 0 1

Dilihat dari tabel tersebut di atas, dapat dilihat bahwa untuk hasil Fungsi 1 akan

memberikan nilai 0 jika kedua data (data A dan B) bernilai sama, dan akan memberikan

nilai 1 jika kedua data bernilai berbeda. Untai pembanding demikian dinamakan dengan

untai pembanding 1-bit dengan keluaran aktif rendah. Gerbang yang sesuai dengan

tabel Fungsi 1 adalah gerbang EXOR.

Untuk hasil Fungsi 2 akan memberikan nilai 0 jika kedua data (data A dan B) bernilai

berbeda dan akan memberikan nilai 1 jika kedua data bernilai sama. Untai pembanding

demikian dinamakan dengan untai pembanding 1-bit dengan keluaran aktif tinggi.

Gerbang yang sesuai dengan tabel Fungsi 1 adalah gerbang EXNOR. Gambar 8.1.

menunjukkan untai pembanding 1-bit.

Gambar 8.1. Untai pembanding 1-bit.

2. Pembanding 2-bit

Untai pembanding 2-bit merupakan pengembangan dari untai pembanding 1-bit. Tabel

berikut menunjukkan tabel kebenaran untai pambending 2-bit.

A1 A0 B1 B0 Fungsi 1 Fungsi 2

0 0 0 0 0 1

0 0 0 1 1 0

0 0 1 0 1 0

0 0 1 1 1 0

0 1 0 0 1 0

0 1 0 1 0 1

0 1 1 0 1 0

0 1 1 1 1 0

1 0 0 0 1 0

1 0 0 1 1 0

1 0 1 0 0 1

1 0 1 1 1 0

1 1 0 0 1 0

1 1 0 1 1 0

1 1 1 0 1 0

1 1 1 1 0 1

Petunjuk Praktikum Rangkaian Digital TK-D3 35

Dilihat dari tabel tersebut di atas, dapat dilihat bahwa untuk hasil Fungsi 1 akan

memberikan nilai 0 jika kedua data (data A dan B) bernilai sama, dan akan memberikan

nilai 1 jika kedua data bernilai berbeda. Untuk hasil Fungsi 2 akan memberikan nilai 0

jika kedua data (data A dan B) bernilai berbeda dan akan memberikan nilai 1 jika kedua

data bernilai sama. Perlu diingat bahwa gerbang EXOR dan gerbang EXNOR hanya

mempunyai dua buah masukan. untuk itu diperlukan gerbang lain yang digunakan untuk

menggabungkan kedua hasil keluaran. Gambar 8.2. menunjukkan untai pembanding 2-

bit.

(a)

(b)

Gambar 8.2. Untai pembanding 2-bit.

(a). Aktif Rendah

(b). Aktif Tinggi

3. Pembanding 8-bit

Pembanding 8-bit dapat disusun dengan menambah atau memodifikasi dari untai

pembanding 2-bit, namun hal ini terasa kurang praktis dan rangkaiannyapun relatif

banyak. Untuk mengatasi hal ini digunakan IC pembanding (comparator) dengan tipe

74688. Di dalam IC ini terdapat untai pembanding 8-bit dengan keluaran aktif rendah

(artinya keluaran akan bernilai rendah atau 0 jika kedua masukan bernilai sama dan

dakan bernilai tinggi atau 1 jika kedua masukan berbeda nilainya).

Gambar 8.3. menunjukkan IC 74688.

C. Percobaan

1. Susunlah untai pembanding atau comparator 1-bit dengan keluaran aktif rendah.

Amatilah hasilnya dalam sebuah tabel kebenaran.

Petunjuk Praktikum Rangkaian Digital TK-D3 36

2. Susunlah untai pembanding atau comparator 2-bit dengan keluaran aktif rendah.

Amatilah hasilnya dalam sebuah tabel kebenaran.

3. Susunlah untai pembanding atau comparator 8-bit dengan mengggunakan IC comparator

74688.

PRAKTIKUM RANGKAIAN DIGITAL

MODUL IX. PEMBANDING (KOMPARATOR) DIGITAL

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1. Untai pembanding atau comparator 1-bit dengan keluaran aktif rendah.

a. Gambar Rangkaian

b. Tabel Kenenaran

A B Fungsi

0 0

0 1

1 0

1 1

Petunjuk Praktikum Rangkaian Digital TK-D3 37

2. Untai pembanding atau comparator 2-bit dengan keluaran aktif rendah.

a. Gambar Rangkaian

b. Tabel Kenenaran

A1 A0 B1 B0 Fungsi

0 0 0 0

0 0 0 1

0 0 1 0

0 0 1 1

0 1 0 0

0 1 0 1

0 1 1 0

0 1 1 1

1 0 0 0

1 0 0 1

1 0 1 0

1 0 1 1

1 1 0 0

1 1 0 1

1 1 1 0

1 1 1 1

3. Untai pembanding atau comparator 8-bit dengan mengggunakan IC comparator 74688.

a. Gambar rangkaian

b. Tabel kebenaran

A7 A6 A5 A4 A3 A2 A1 A0 B7 B6 B5 B4 B3 B2 B1 B0 Fungsi

0 X X X X X X X 1 X X X X X X X

0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

0 0 0 0 0 0 0 1 0 0 0 0 0 0 0 1

Petunjuk Praktikum Rangkaian Digital TK-D3 38

0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1

1 1 1 1 0 0 0 0 1 1 1 1 0 0 0 0

X 1 X X X X X X X 0 X X X X X X

1 1 1 1 1 1 1 0 1 1 1 1 1 1 1 0

X X X X X X X 0 X X X X X X X 1

1 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

MODUL X

REGISTER GESER

A. Maksud dan Tujuan

1. Maksud : Memperkenalkan untai register geser kepada praktikan.

2. Tujuan : Praktikan dapat mengetahui fungsi untai register geser dan berbagai

kombinasinya.

B. Teori

Register geser merupakan salah satu untai sekuensial dalam sistem digital. Register

geser digunakan untuk mencatat data yang masuk secara berurutan. Adapun jenis-jenis

register geser tersebut adalah :

a) Serial IN serial OUT (SISO)

Masukan dari register ini adalah serial dan output dari register ini juga serial.

Ilustrasi :

Data In Data Out

b) Serial IN paralel OUT (SIPO)

Masukan dari register ini adalah serial dan output dari register ini paralel.

Ilustrasi :

Data In

Data Out (paralel)

Petunjuk Praktikum Rangkaian Digital TK-D3 39

c) Paralel IN serial OUT (PISO)

Masukan dari register ini adalah paralel dan output dari register ini serial.

Ilustrasi :

Data In Data Out

d) Paralel IN paralel OUT (PIPO)

Masukan dari register ini adalah paralel dan output dari register ini juga paralel.

Ilustrasi :

Data In (paralel)

Data Out (paralel)

Register geser yang digunakan untuk praktikum ini adalah jenis SN 74LS194 yang

mempunyai Input serial maupun paralel (4-bit), dengan Output Paralel (4-bit). Register geser

dengan menggunakan IC jenis ini dapat digunakan untuk operasi penggeseran ke kiri (left

shift) atau untuk operasi penggeseran ke kanan (right shift). Berikut ini adalah gambar IC

74LS194.

Gambar 10.1. Susunan kaki IC 74LS198

Jalur-jalur yang ada pada register IC 74LS198 dapat dilihat pada tabel berikut ini:

Input Output

Clear Mode Clock Serial Paralel QA QB QC QD Keterangan

S1 S0 Left Right A .. D

L X X X X X X L L L L Clear

H X X L X X X QA0 QB0 QC0 QD0 No Change

H H H X X a .. h a b c d Par. Load

H L H X H X H QAn QBn QCn Sh. Right

H L H X L X L QAn QBn QCn Sh. Right

H H L H X X QBn QCn QDn H Sh. Left

H H L L X X QBn QCn QDn Sh. Left

L

H L L X X X X QA0 QB0 QC0 QD0 No Change

Keterangan :

Jalur Clear digunakan untuk mereset keluaran atau output paralel.

Jalur Mode S1 dan S0 digunakan untuk mengendalikan operasi penggeseran

Jalur Clock (T) digunakan untuk memberikan sinyal pulsa.

Jalur Serial Left (SEl) digunakan untuk memberikan data serial terhadap data yang

akan digeser ke kiri

Petunjuk Praktikum Rangkaian Digital TK-D3 40

Jalur Serial Right (SEr) digunakan untuk memberikan data serial terhadap data yang

akan digeser ke kanan

Jalur Paralel Input (A .. D) digunakan untuk memberikan data masukan paralel

terhadap regsiter.

Jalur Paralel Output (QA .. QD) merupakan jalur keluaran dari register (8-bit paralel)

C. Percobaan

C.1. Serial IN Serial OUT

Langkah percobaan (Shift Right/geser kanan)

1. Hubungkan jalur S1 dan S0 dengan masukan saklar (beri logika 0 untuk S1 dan

logika 1 untuk S0) menjadi mode shift right (geser kanan).

2. Hubungkan jalur QD dengan penampil LED sebagai keluaran serial

3. Hubungkan jalur SEr dengan saklar biner sebagai masukan serial

4. Berilah data pada SEr diikuti dengan penekanan tombol clock (catatlah data

tersebut).

5. Ulangi langkah 4 sebanyak delapan kali

6. Amati tampilan LED biner diikuti dengan penekanan tombol clock.

Tabel Pengamatan

Input Serial SEr Output Serial (QD)

1 0 1 0

0 0 1 1

1 1 0 0

0 1 0 1

TUGAS A. Setelah melakukan percobaan C.1., maka buatlah register geser tersebut

sedemikian sehingga berfungsi sebagai register geser kiri (Shift Left). Jalur mana saja yang

digunakan, data serial dapat diubah sesuai dengan keinginan anda.

C.2. Paralel IN Paralel OUT

Langkah percobaan

1. Hubungkan jalur S1 dan S0 dengan masukan saklar (beri logika 1 untuk S1 dan

logika 1 untuk S0) menjadi mode paralel in.

2. Hubungkan jalur QA sampai QD dengan penampil LED sebagai keluaran paralel

3. Hubungkan jalur A sampai H dengan saklar biner sebagai masukan paralel

(catatlah data tersebut).

Tabel Pengamatan

Input Paralel Output Paralel (QA..QD)

(A B C D)

1 0 1 0

0 0 1 1

1 1 0 0

0 1 0 1

TUGAS B.

1. Buatlah register dengan masukan serial dan output paralel (geser kiri).

2. Buatlah register dengan masukan serial dan output paralel (geser kanan).

3. Gunakan tabel pengamatan pada percobaan C2. (data masukan dapat diganti)

Petunjuk Praktikum Rangkaian Digital TK-D3 41

PRAKTIKUM RANGKAIAN DIGITAL

MODUL X. REGISTER GESER

Nomor Mhs : ........ Paraf Asisten : .........

Nama Praktikan : .................. tanggal : .........

1. Serial Input Serial Output

Tabel Pengamatan

Input Serial SEr Output Serial (QD)

1 0 1 0

0 0 1 1

1 1 0 0

0 1 0 1

2. Paralel Input Paralel Output

Tabel Pengamatan

Input Paralel Output Paralel (QA..QD)

(A B C D)

1 0 1 0

0 0 1 1

1 1 0 0

0 1 0 1

Tugas

A.

...........................

...........................

...........................

...........................

B1.

Petunjuk Praktikum Rangkaian Digital TK-D3 42

...........................

...........................

...........................

...........................

B2.

...........................

...........................

...........................

...........................

B3.

...........................

...........................

...........................

...........................

B4.

...........................

...........................

...........................

...........................

B5.

...........................

...........................

...........................

...........................

Petunjuk Praktikum Rangkaian Digital TK-D3 43

PANDUAN PRAKTIKUM

RANGKAIAN DIGITAL

UPT LABORATORIUM

SEKOLAH TINGGI MANAJEMEN INFORMATIKA DAN KOMPUTER

AKAKOM

YOGYAKARTA

Anda mungkin juga menyukai

- Nama Anggota STM Dos RohaDokumen38 halamanNama Anggota STM Dos RohaRolandoganda SihombingBelum ada peringkat

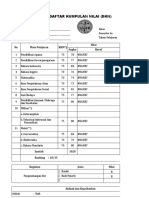

- DKN Raport Kelas 8.3 2019Dokumen77 halamanDKN Raport Kelas 8.3 2019Rolandoganda SihombingBelum ada peringkat

- CaraDokumen17 halamanCaraRolandoganda SihombingBelum ada peringkat

- Doa Bapa KamiDokumen1 halamanDoa Bapa KamiRolandoganda SihombingBelum ada peringkat