Hjgdeghiuhuhuhg

Diunggah oleh

Anonymous G1iPoNOKJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Hjgdeghiuhuhuhg

Diunggah oleh

Anonymous G1iPoNOKHak Cipta:

Format Tersedia

On the Ultimate Limits of IC Inductors-An RF MEMS Perspective

Hector J. De Los Santos

COVENTOR, Inc.

7 Corporate Park, Suite 260, Irvine, CA 92606

Trace resistance, due to its finite conductivity and width; (3)

Abstract

Substrate capacitance and ohmic losses, due to their shunting

Inductors are playing an ever-increasing role in RFICs, of the input signal to ground and, thus, causing less than the

motivating extensive work on the development of structures to

input signal to reach the output. These loss elements are

achieve optimized performance. In this paper we review the embodied by the circuit model of Fig. 2 [ 101.

different approaches being explored to achieve high inductor

Q and self-resonance frequency, in the context of conventional

CMOS and BiCMOS processes, and examine how the

application of RF MEMS techniques may effect superior

monolithic inductor performance, and at what expense.

Introduction

Inductors are playing an ever-increasing role in RFICs [ 1-

41. In addition to being frequently employed in passive tunkg Silic

circuits, or as high-impedance chokes, many novel techniques

to achieve low-voltage operation in advanced silicon IC

processes rely on the negligible DC voltage drop across

inductors when utilized as loads or as emitterhource

degenerators [3-41. When fabricated in a planar process, the

trace capacitance to ground tends to lower the inductor self- Figure 1. Planar inductor [SI.

resonance frequency, and the substrate conductivity tends to

lower its quality factor (Q) [5]. While optimization of the

spiral geometry and line width [2], 15-61 is essential to tailor

the frequency of maximum Q, this exercise only addresses

minimization of the trace o h c losses and substrate

capacitance. Thus, a number of attempts to use conventional

processing techniques to diminish the substrate losses created

by eddy currents induced by the magnetic field of the spiral COXL COX

have been pursued. For instance, while [5] introduced

blocking p-n-p junctions in the path of the eddy current

T T

flowing in an underlying p+ layer, [7] introduced a patterned

metal ground shield to also block the eddy current. These, and

similar approaches, however, only achieve modest relative

improvements and, certainly, do not achieve Qs much greater

than 10, or self-resonance frequencies greater than a few GHz.

The fabrication flexibility afforded by Figure 2. Equivalent circuit model of planar inductor

microelectromechanical systems (MEMS) technology is [lo].

expected to greatly enhance the performance of monolithic RF

passive devices but, by how much and at what expense? In this A multitude of ways to address one or more of the above

paper, for the first time, we present an analysis of RFIC inductor performance-limiting factors, in the context of

inductors build in both conventional and RF MEMS conventional Si processes, have been advanced. Next,

technologies, and establish a projection of their ultimate respective typical cases are reviewed.

achievable performance limits. Eddy current blocking structures are shown in Fig. 3. In

these structures, the eddy current, which flows in paths around

Conventional RFIC Inductors the axis of the spiral, is reduced by introducing structures that

The fundamental monolithic inductor is usually increase the path resistance. In the example of Fig. 3(a) [5],

implemented as a spiral trace disposed on the passivation layer this is accomplished by inserting narrow stripes of n+ regions

over a silicon substrate, Fig. 1. The connection to the perpendicular to the current flow such as to create blocking p-

innermost turn is effected either through an underpass, or via n-p junctions. This blocking structure resulted in a Q

an airbridge. An examination of the fundamental structure improvement from 5.3 to 6.0 (13.2%) at 3.5 GHz on a 1.8nH

reveals the following sources of performance degradation [9]: inductor, obtaining an inductance-per-tum of 0.9nH.

(1) Eddy current-induced losses, due to magnetic field

penetration into both the substrate and adjacent traces; (2)

0-7803-7430-4/02/$17.0002002 IEEE 1027 2002 Electronic Components and Technology Conference

Si substrate ( p - 5 - io n . cm ), implanting ions in

- ~3 x 1019~ 1 1 2 -,~

concentrations ranging from 1x 1019~ r n to

resulted in Qs between 3.8 and 5.8, respectively, at about 2

GHz for 1.lnH to 1.25nH inductance values, obtaining an

inductance-per-turn of -0.781-H.

Approaches to reduce metal trace losses, Fig. 4, invcdve

A reduction of both conduction- and magnetically-induced

losses.

I

, I, ! ! SpiralLines

E Field \/ ' SoiralTrace

\ ll/ j j

I +I-

i j I ,

p Substrate

I \, I /

n+ Blocking Structure

(a)

I

r kcitation

mat

Eddy CduTult Loops

Figure 4. Losses in inductor metal trace [12].

From a study of the field distribution in a spiral [2], [91], it

was determined that ohmic losses are predominant in the outer

tums, while, since the magnetic field reaches a maximum near

the axis, magnetic losses predominate in the inner tums.

Accordingly, an algorithm to vary the trace width from a small

width for the inner tums, to a larger width for the outer tums,

resulted in a layout-optimized structure, Fig. 5. For inductors

realized over an etched bulk (so as to not have substrate losses

present) with metal traces exhibiting 20rn!2 sheet

resistances, this approach yielded a measured Q of 17 at 1.5

GHz for a 34nH inductor, and predicted Q values greater lhan

40 for a 20nH inductor at 3.5 GHz, which represen1.s a

projected Q improvement of 60%, with respect to single stip-

width inductors operating also at 3.5GHz [9].

Slots between Strips

(b)

Figure 3 (a) Eddy-current blocking approaches: (a) p-n-p

junction perpendicular to current flow path [SI. (b)

Patterned metal ground plane with open slots [7].

In the pattemed-ground approach, Fig. 3(b) [7], slots,

oriented perpendicularly to the spiral, are etched in the ground

plane. These, act as open circuits to impede the path of the

eddy currents. The slots are made with a width narrow enough

to preclude the vertical electric field from penetrating down to

the underlying silicon, and merge together at a metal strip

around the periphery. Implementation of this scheme has Figure 5. Metal loss-optimized inductor layout [91.

resulted in a Q improvement from 5.08 to 6.76 (33%) at 2

GHz on a 7.5 nH inductor, obtaining an inductance-per-turn of Recent work [131 aimed at obtaining both increased Q and

1.07nH. self-resonance frequency, without process modifications, have

In the substrate damage approach [l 11, the low-resistivity concluded that differentially driven inductors have the

of the Si substrate is increased by disordering the lattice sites, potential to exhibit (ideally) double the Q and increased Iself-

i.e., by damaging the lattice structure with high-energy- resonance frequency, with respect to single-ended inductors,

due to the reduced effect of the substrate shuntparasitic:s in

implanted (2OOkeV) si:, ions. Starting with a low-resistivity the differential case. With the voltages and currents at Ports 1

1028 2002 Electronic Components and Technology Conference

and 2 excited 180” out of phase, when differentially excited, R F MEMS-Enabled Inductors

Fig. 6, a useful property of the structure is that the trace In RF MEMS technology, the power of surface and bulk

currents flow in the same directions and this increases the micromachining fabrication techniques [ 171 is exploited to

inductance per unit area. either suspend within the bulk [18], or elevate above the wafer

surface [19], inductor structures, thus eliminating the major

Underpass i Axis of Symmetry

sources of performance degradation.

Bulk micromachined inductors, similar to that shown in

Fig. 7, are realized by removing the substrate under the

Node inductor spiral via top-side etching [18]. This type of structure

resulted in a self-resonance frequency enhancement from 800

MHz to 3 GHz, upon substrate removal, and a Q of 22 at 270

MHz on an 115nH inductor, obtaining an inductance-per-turn

ratio of 5nH [11.

Figure 6. Symmetrical differentially driven microstrip

inductor [13].

The approach has resulted in Qs of 6.6 and 9.3 at 1.6 GHz

and 2.5 GHz, respectively, for an inductor of 8nH [13].

As may be surmized by examining the approaches

presented thus far for optimizing planar inductors in

conventional silicon processes, these fall into two fundamental Figure 7. Bulk-micromachined inductor 1181.

categories, namely, substrate insulation techniques, and layout While the performance of bulk micromachined inductors

optimization techniques. Two other opportunities for improves upon that of their conventional counterparts,

performance enhancement may be also available, depending questions have been raised regarding their ruggedness to

on the number of top metal interconnect lavels and the ability withstand subsequent wafer processing, lack of a good RF

to increase the thickness of the traces. Pertaining to these, the ground, and susceptibility of their characteristics to

following examples are relevant: (1) A 1.88nH inductor with a electromagnetic coupling. This issues were addressed in the

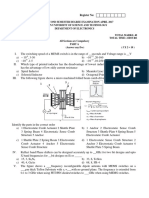

Q of 6-10 at 4GHz fabricated on a 10 Q . cm / I - 3 p m elevated structure of Fig. 8 [19]. The structure consists of an

single-metal process, demonstrated by Long and Copeland elevated inductor suspended over a 3 0 p -deep copper-lined

[14]; (2) A 13nH inductor with a Q of 12 at 3GHz fabricated cavity etched in Si bulk. The cavity depth is chosen such that

on a 2 kn . cm 1 2 p m double-metal process, demonstrated the eddy currents induced in the metal shield are small.

by Park et al. [l5]; and (3) A 2.2nH inductor with a Q of 16 at Cu-Encapdated

2GHz fabricated on a 12 k~ . cm / 4 . 3 p m triple-metal

process, demonstrated by Burghartz et al. [16].

Clearly, in light of the fact that most commercial silicon

bipolar and BiCMOS processes employ wafers with

resistivities in the neighborhood 10 Q . cm , and that to

reduce hot-electron induced substrate currents, as well as

isolate sensitive analog circuits from noisy digital circuits,

most sub-micron CMOS wafers employ substrates with

resistivities around 0.01 n . cm [2], it is not difficult to see

that the substrate poses the ultimate limitation on the Figure 8. Schematic of a copper-encapsulated polysilicon

performance of IC inductors. Some estimates [ 141, in fact, set inductor suspended over a copper-lined cavity beneath

this limit at approximately a Q less than 10 in the 1-3GHz 1191.

range for a 1nH inductor. This approach yielded a Q of 30 at 8 GHz on a 10.4nH

The potential of RF MEMS technology to overcome the inductor with a self-resonance frequency of 10.1 GHz,.and an

“substrate barrier” limiting the performance of IC inductors is inductance-per-turn of 1.48nH.

presented next.

1029 2002 Electronic Components and Technology Conference

While substrate removal and shielding, and spiral RF MEMS Perspective on RFIC Inductors

elevation do improve inductor performance, the remaining As demonstrated in the previous section, the versatility of

parasitic capacitance, between metals trace and the substrate, RF MEMS fabrication technology to decouple IC inductor

poses the ultimate limitation on improvement. The solenoid performance from substrate characteristics is unquestionable.

inductor, Fig. 9, addresses these issues [20]. It might appear, however, that, to take advantage of it, one

would have to incur “extra” processing steps, and this is

indeed the case. Nevertheless, the fact that these estra

processing steps may be implemented as a “post-process

module” [22], that does not require chip manufacturer!; to

modify their high-volume fabrication processes, makes the

approach extremely appealing, given the enabling capability

of RF MEMS. Indeed, as the frequency capability of advanced

silicon IC processes increases to many multiples of GHz, the

concomitant manifestation of substrate losses will become

progressively more difficult to circumvent. The future, thus,

will inexorably lead to RF MEMS.

Conclusions

The performance of monolithic RFIC inductors has made

great strides, despite the limits set by poor subslrate

characteristics, in particular, low resistivity. In this context, it

is expected that inductors with Qs and inductance markedly

greater than 10 and lnH, respectively, in the 1-4GHz

frequency range will not be possible. Therefore, the extension

Figure 9. SEM photograph of 20-turn, on-Si, air-core, all-

of silicon processes to higher frequency wireless applications

copper solenoid inductor(upper: overview, lower:

will inexorably lead to the exploitation of RF MEMS, via

magnified view) [20].

post-processing techniques.

This approach yielded a Q of 16.7 at 2.4 GHz on 2.67 nH

inductors, with an inductance per-tum of 0.136nH. One Acknowledgments

advantage of solenoid inductors, over spiral ones, is that they I would like to thank ECTC 2002 Program Committee

exhibit a linear relationship between inductance and number member Ms. Lei Mercado, of Motorola, Inc., for the invita.tion

of turns. to contribute this paper.

Another approach aimed at decoupling inductor properties References

from those of the substrate is the self-assembly principle, Fig. 1. Chang, J. Y.-C. and A. A. Abidi, “Large suspended

10 [21]. inductors on silicon and their use in a 2-um CMOS RF

amplifier,” IEEE Electron Device Lett., vol. 14, (1993),

pp. 246-248.

2. Craninckx, J. and M. Steyaert, “A 1.8-GHz low-phase-

noise CMOS VCO using optimized hollow spiral

inductors,” IEEE J . Solid-state Circuits, vol. 32, No. 5

(1997), pp. 736-745.

3. Abou-Allam, A., J.J. Nisbet, and M.C. Maliepaard, ‘‘LOW-

Voltage 1.9 GHz Front-End Receiver in O h m CMOS

Technology, “ IEEE J . Solid-state Circuits, Vol. 36, No.

10 (2001), pp. 1434-1443.

4. Gatta, F., et al., “A 2-dB Noise Figure 900-MHz

Differential CMOS LNA,” IEEE J . Solid-state Circuits,

Vol. 36, NO. 10 (2001), pp. 1444-1452.

Figure 10. 4lh-tu1-nmeander inductor after self-assembly 5. Memyei, F., F. Darrer, M. Pardoen, and Andreas Sibrai,

1211. “Reducing the Substrate Losses of RF Integrated

Inductors,” IEEE Microwave and Guided Wave Lstts.,

In this approach, solder surface tension self-assembly is

Vol. 8, NO. 9 (1998), pp. 300-301.

used to bring planar inductor structures perpendicular to the

substrate. It has yielded improvements in the Q of 2nH 6. Niknejad, A.M. and R.G. Meyer, “Analysis and

meander inductors from 4 at lGHz, for the planar realization, optimization of monolithic inductors and transformers for

RF IC’s, IEEE J . Solid-state Circuits, Vol. 32, No. 5

to 20 at 3 GHz for the self-assembly implementation, with

0.44nH per turn [21]. (1997) pp. 375-378.

1030 2002 Electronic Components and Technology Conference

7. Yue, C.P. and S.S. Wong, “On-Chip Spiral Inductors with technology,” IEEE Microwave Guided Wave Lett., Vol. 7 ,

Pattemed Ground Shields for Si-Based RF IC’s,’’ IEEE J. (1997), pp. 45-47.

Solid-state Circuits, Vol. 33, NO. 5 (1998), pp. 743-752. 16. Burghartz, J.N, et al, “Spiral inductors and transmission

8. Yue, C.P. and S.S. Wong, “A Study on Substrate Effects lines in silicon technology using copper-damascene

of Silicon-Based RF Passive Components,” 1999 IEEE interconnects and low-loss substrates,” IEEE Trans.

Int. Microwave Symp., Anaheim, CA. Microwave Theory Tech., Vol. 45, No. 10 (1997), pp.

9. Lopez-Villegas, J.M., et al., Improvement of the Quality 1961-1968.

Factor of RF Integrated Inductors by Layout 17. De Los Santos, H.J., Introduction to

Optimization,” IEEE Trans. Microwave Theory Tech., Microelectromechanical (MEM) Microwave Svstems,

Vol. 48, NO. 1 (2000), pp. 76-83. Artech House (Norwood, MA, 1999), pp. 6-8.

lO.Yue, C. P. and S.S. Wong, “Physical Modeling of Spiral 18.Sun, Y., H. van Zeijl, J.L. Tauritz and R.G.F. Baets,

Inductors on Silicon,” IEEE Trans. Electron Devices., “Suspended Membrane Inductors and Capacitors for

Vol. 47, NO. 3, (2000), pp. 560-568. Application in Silicon MMICs,” IEEE Microwave and

1l.Chen, P.Q. and Y.-J. Chan, “Improved Microwave Millimeter-wave Monolithic Circuits Symposium Digest of

Performance on Low-Resistivity Si substrates by Si’ Ion Papers, 1996, pp. 99-102.

Impalnation,” IEEE Trans. Microwave Theory Tech., Vol. 19. Jiang., H., Y. wang, J.-L.A. Yeh, and N.C. Tien.,

48, NO. 9 (2000), pp. 1582-1585. “Fabrication of High-Performance On-Chip Suspended

12. Kuhn, W.B., “Approximate Analytical Modeling of Spiral Inductors by Micromachining and Electroless

Current Crowding Effects in Multi-Tuen Spiral Inductors,” Copper Plating,” 2000 IEEE IMS Digest of Papers,

2000 IEEE Int. Microwave Symp., Baltimore. MD. Boston, MA.

13. Danesh, M. and J.R. Long, “Differentially Driven 20. Yoon, J.-B, B.K. Kim, C.H. Han, E. Yoon, and C.K. Kim.,

Symmetric Microstrip Inductors,” IEEE Trans. Microwave “Surface Micromachined Solenoid On-Si and On-Glass

Theory Tech., Vol. 50, No. 1 (2002), pp. 332-341. Inductors for RF Applications,” IEEE Electron Device

14. Long, J.R. and M.A. Copeland, “The Modeling, Letters, Vol. 20, (1999), pp. 487.

Characterization, and Design of Monolithic Inductors for 21.Dahlmann, G.W., E.M. Yeatman, P.R. Young, I.D.

Silicon RF IC’s,” IEEE J . Solid-state Circuits, Vol. 32, Robertson, and S.Lucyszyn, “MEMS High Q Microwave

NO. 3 (1997), pp. 357-369. Inductors Using Solder Surface Tension Self-Assembly, “

lS.Park, M., et al, “High Q CMOS-compatible microwave 2001 IEEE IMS Digest of Papers.

inductors using double-metal interconnection silicon

22. Pham, N.P. et al., “IC-Compatible Two-Level Bulk

Micromachining Proces Module for RF Silicon

Technology,” IEEE Trans. Electron Devices, Vol. 48, No.

8 (2001), pp. 1756-1764.

1 * COLOR 1

Your accompanying CD-ROM contains a

version of this paper with color images.

http:/ICMMN.cpmt.org/proceedings/

1031 2002 Electronic Components and Technology Conference

Anda mungkin juga menyukai

- Busch13 Towards A More Secure Border Control With 3D Face RecognitionDokumen12 halamanBusch13 Towards A More Secure Border Control With 3D Face RecognitionAnonymous G1iPoNOKBelum ada peringkat

- M3 Users GuideDokumen5 halamanM3 Users GuideAnonymous G1iPoNOKBelum ada peringkat

- 001184592-da-01-en-IC INTERFACE BUS ISO E L9637D SOIC 8 STM PDFDokumen15 halaman001184592-da-01-en-IC INTERFACE BUS ISO E L9637D SOIC 8 STM PDFTeguh PriyonoBelum ada peringkat

- Mail DecisionDokumen10 halamanMail DecisionAnonymous G1iPoNOKBelum ada peringkat

- TPO Data Coverage ENDokumen14 halamanTPO Data Coverage ENAnonymous G1iPoNOKBelum ada peringkat

- US7119339B2Dokumen2 halamanUS7119339B2Anonymous G1iPoNOKBelum ada peringkat

- United States Patent: Swersey Et Al. Jan. 18, 2005Dokumen14 halamanUnited States Patent: Swersey Et Al. Jan. 18, 2005Anonymous G1iPoNOKBelum ada peringkat

- US7119339B2Dokumen2 halamanUS7119339B2Anonymous G1iPoNOKBelum ada peringkat

- T Rec Y.2111 201111 I!!pdf eDokumen214 halamanT Rec Y.2111 201111 I!!pdf eAnonymous G1iPoNOKBelum ada peringkat

- Applications: RFMD + Triquint QorvoDokumen1 halamanApplications: RFMD + Triquint QorvoAnonymous G1iPoNOKBelum ada peringkat

- AFSI-T21C3S: 1.25 Gb/s To 11.1 Gb/s Transimpedance Amplifier ICDokumen1 halamanAFSI-T21C3S: 1.25 Gb/s To 11.1 Gb/s Transimpedance Amplifier ICAnonymous G1iPoNOKBelum ada peringkat

- PrintDokumen1 halamanPrintAnonymous G1iPoNOKBelum ada peringkat

- Product Description PDFDokumen148 halamanProduct Description PDFCoachArun MishraBelum ada peringkat

- B FIPS Siem InstDokumen39 halamanB FIPS Siem InstJames DiggityBelum ada peringkat

- PrintDokumen1 halamanPrintAnonymous G1iPoNOKBelum ada peringkat

- Cart - Wish - ComDokumen2 halamanCart - Wish - ComAnonymous G1iPoNOKBelum ada peringkat

- DE9105122U1 Bibliographic DetailsDokumen1 halamanDE9105122U1 Bibliographic DetailsAnonymous G1iPoNOKBelum ada peringkat

- EVDO RevADokumen22 halamanEVDO RevAKing GKBelum ada peringkat

- B FIPS Siem InstDokumen39 halamanB FIPS Siem InstJames DiggityBelum ada peringkat

- United States Patent (10) Patent No.: US 9,035,689 B2Dokumen15 halamanUnited States Patent (10) Patent No.: US 9,035,689 B2Anonymous G1iPoNOKBelum ada peringkat

- Obsolete: Six Output Programmable LED Current SinkDokumen9 halamanObsolete: Six Output Programmable LED Current SinkAnonymous G1iPoNOKBelum ada peringkat

- M3 Users GuideDokumen5 halamanM3 Users GuideAnonymous G1iPoNOKBelum ada peringkat

- Measurement and Analysis of Video Streaming Performance in Live Umts NetworksDokumen5 halamanMeasurement and Analysis of Video Streaming Performance in Live Umts NetworksAnonymous G1iPoNOKBelum ada peringkat

- PAM8302A: A Product Line of Diodes IncorporatedDokumen14 halamanPAM8302A: A Product Line of Diodes IncorporatedAnonymous G1iPoNOKBelum ada peringkat

- Laser Controller: Type: Ls11-La16v60-T19208-V0-872Dokumen2 halamanLaser Controller: Type: Ls11-La16v60-T19208-V0-872Vandana SinghBelum ada peringkat

- A60 Two-Channel Power Amplifier: User GuideDokumen12 halamanA60 Two-Channel Power Amplifier: User GuideAnonymous G1iPoNOKBelum ada peringkat

- lxmg1960 28 0x - ObsDokumen8 halamanlxmg1960 28 0x - ObsAnonymous G1iPoNOKBelum ada peringkat

- PAM8302A: A Product Line of Diodes IncorporatedDokumen14 halamanPAM8302A: A Product Line of Diodes IncorporatedAnonymous G1iPoNOKBelum ada peringkat

- Data Sheet: Afct-5941XtxzDokumen15 halamanData Sheet: Afct-5941XtxzAnonymous G1iPoNOKBelum ada peringkat

- 3535 White 1W SMD - Specification - R3 - 20160129Dokumen20 halaman3535 White 1W SMD - Specification - R3 - 20160129Anonymous G1iPoNOKBelum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (400)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (895)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (588)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (266)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2259)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (121)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Reconfigurable Antenna With Matching Network Final Project ReportDokumen44 halamanReconfigurable Antenna With Matching Network Final Project ReportDhruv ChaudharyBelum ada peringkat

- Mems Unit 1Dokumen48 halamanMems Unit 1CHETAN SETIYABelum ada peringkat

- Mems PPT 1Dokumen10 halamanMems PPT 1Mohith MarripatiBelum ada peringkat

- Anna University ME Optical Communication 2019 CurriculumDokumen36 halamanAnna University ME Optical Communication 2019 CurriculumAlphapalm100% (1)

- Design and Experimental Analysis of Multiband Frequency Reconfigurable Antenna For 5G and Sub-6 GHZ Wireless CommunicationDokumen15 halamanDesign and Experimental Analysis of Multiband Frequency Reconfigurable Antenna For 5G and Sub-6 GHZ Wireless CommunicationnhBelum ada peringkat

- Introduction To Comsol OptionalDokumen220 halamanIntroduction To Comsol OptionalJasleen KaurBelum ada peringkat

- Communication: A Reconfigurable Filtering Antenna With Integrated Bandpass Filters For UWB/WLAN ApplicationsDokumen4 halamanCommunication: A Reconfigurable Filtering Antenna With Integrated Bandpass Filters For UWB/WLAN Applicationsabinaya_359109181Belum ada peringkat

- Investigation of Reconfigurability of Dual-Band Microstrip Patch AntennaDokumen4 halamanInvestigation of Reconfigurability of Dual-Band Microstrip Patch Antennayulindon khaidirBelum ada peringkat

- Vol MNE 25 2017fDokumen117 halamanVol MNE 25 2017fvbanuBelum ada peringkat

- YOLE - MEMS Tech Seminar 2013-PublicDokumen26 halamanYOLE - MEMS Tech Seminar 2013-PublicRobertoBelum ada peringkat

- RF Mems Final UnivDokumen2 halamanRF Mems Final UnivSTUDENTS OF DOE CUSATBelum ada peringkat

- SP4T SP5TDokumen178 halamanSP4T SP5TPriyanka DwivediBelum ada peringkat

- A Survey On Reconfigurable Antennas: Zhang Jiajie, Wang Anguo, Wang Peng Tianjin University Tianjin 300072 ChinaDokumen4 halamanA Survey On Reconfigurable Antennas: Zhang Jiajie, Wang Anguo, Wang Peng Tianjin University Tianjin 300072 ChinaMurthyBelum ada peringkat

- (J. Bernhard) Reconfigurable AntennasDokumen74 halaman(J. Bernhard) Reconfigurable AntennasSwapna SBelum ada peringkat

- Module 6Dokumen26 halamanModule 6Neha RaoBelum ada peringkat

- RF MEMS Filters RF MEMS Filters RF MEMS Filters RF MEMS FiltersDokumen38 halamanRF MEMS Filters RF MEMS Filters RF MEMS Filters RF MEMS Filtersstanpjames2309Belum ada peringkat

- A New Wafer-Level Packaging Technology For MEMS With Hermetic Micro-EnvironmentDokumen11 halamanA New Wafer-Level Packaging Technology For MEMS With Hermetic Micro-EnvironmentOschano BuchananBelum ada peringkat

- 2021 Faculty Ee 1300007546 With AttchmentDokumen31 halaman2021 Faculty Ee 1300007546 With AttchmentKurmendra SinghBelum ada peringkat

- Datasheet PDFDokumen21 halamanDatasheet PDFheriBelum ada peringkat

- Devices and Sensors Applicable To 5G System ImplementationsDokumen15 halamanDevices and Sensors Applicable To 5G System ImplementationsCosmin KrishnaBelum ada peringkat

- Mems Sensors in Iot Applications: April 2021Dokumen6 halamanMems Sensors in Iot Applications: April 2021Abhish AbhiBelum ada peringkat

- Reconfigurable AntennaDokumen33 halamanReconfigurable Antennagauri dhavaleBelum ada peringkat

- A Comprehensive Analysis On The State-Of-The-Artdevelopments in Reflectarray, Transmitarray, and Transmit-Reflectarray AntennasDokumen22 halamanA Comprehensive Analysis On The State-Of-The-Artdevelopments in Reflectarray, Transmitarray, and Transmit-Reflectarray AntennasZohre NoamadeBelum ada peringkat

- Evolutionary Trends in Transmit-Receive Module For Active Phased Array RadarsDokumen7 halamanEvolutionary Trends in Transmit-Receive Module For Active Phased Array RadarsPhan Xuân TuấnBelum ada peringkat

- Electrical & Electronics Engineering PDFDokumen10 halamanElectrical & Electronics Engineering PDFmdasifhassanapspdcl100% (1)

- Mems Assignment TwoDokumen7 halamanMems Assignment TwoDrey rap.dance.songwritingBelum ada peringkat

- Sensors: Thin Film Encapsulation For RF MEMS in 5G and Modern Telecommunication SystemsDokumen12 halamanSensors: Thin Film Encapsulation For RF MEMS in 5G and Modern Telecommunication Systems施玟宇Belum ada peringkat

- Arrow 0909 Live PPT PDFDokumen57 halamanArrow 0909 Live PPT PDFปฏิวัติ ชาติดํารงค์Belum ada peringkat

- Evolution of Residual StressDokumen4 halamanEvolution of Residual StressengetarcioBelum ada peringkat

- Nanosatellite Communication and MEMS Technology: Project SummaryDokumen17 halamanNanosatellite Communication and MEMS Technology: Project Summaryjaennii parkBelum ada peringkat