BCD to Excess-3 Code Converter Lab Report

Diunggah oleh

Muhammad Asad Khalil RaoJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

BCD to Excess-3 Code Converter Lab Report

Diunggah oleh

Muhammad Asad Khalil RaoHak Cipta:

Format Tersedia

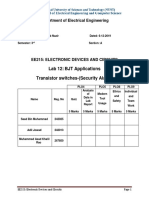

Department of Electrical Engineering

Faculty Member: ____________________ Dated: ________________

Semester: __________________________ Section: ________________

Group No.:

EE-221: Digital Logic Design

Lab 6: BCD to Excess-3 Code Conversion

PLO4/CLO4 PLO4/CLO4 PLO5/CLO5 PLO8/CLO6 PLO9/CLO7

Name Reg. No Viva / Lab Analysis Modern Ethics and Individual Total

Performanc of data in Tool Usage Safety and Team marks

e Lab Report Work Obtained

5 Marks 5 Marks 5 Marks 5 Marks 5 Marks 25 Marks

EE221: Digital Logic Design Page 1

Lab 6: BCD to Excess-3 Code Conversion

This Lab has been divided into two parts:

In first part you are required to design and implement a BCD to Excess-3 code converter.

The next part is the Verilog Modeling and Simulation of the Circuit you implemented in you first

lab.

Objectives:

Understand steps involved in design of combinational circuits

Understand binary codes for decimals and their hardware realization

Write code for combinational circuits using Verilog Gate Level Modeling

Design a circuit in Verilog by calling different modules

Lab Instructions

This lab activity comprises three parts, namely Pre-lab, Lab tasks, and Post-Lab Viva

session.

The lab report will be uploaded on LMS three days before scheduled lab date. The

students will get hard copy of lab report, complete the Pre-lab task before coming to the

lab and deposit it with teacher/lab engineer for necessary evaluation.

The students will start lab task and demonstrate design steps separately for step-wise

evaluation (course instructor/lab engineer will sign each step after ascertaining functional

verification).

Remember that a neat logic diagram with pins numbered coupled with nicely patched

circuit will simplify trouble-shooting process.

After the lab, students are expected to unwire the circuit and deposit back components

before leaving.

The students will complete lab task and submit complete report to Lab Engineer before

leaving lab.

There are related questions at the end of this activity. Give complete answers.

EE221: Digital Logic Design Page 2

Pre-Lab Tasks: (To be done before coming to the lab) 3 marks

1. What do you understand by decimal codes? Name any three of these. Express the last four

digits of your registration number duly negated in signed magnitude, 10’s complement, and 9’s

complement forms for the following codes:

a. 8,4,2,1

b. Excess-3

2. What is the significance of BCD code? Write its application in digital circuits.

3. In the lab you would be implementing a BCD to Excess-3 code converter. Make a truth table

for both the codes by filling in the following tables and simplify the expressions for W, X, Y, Z in

terms of A, B, C, D. (Use backside of the page if necessary). Use unused combinations as

don’t care conditions.

HINT:

Dec Binary Excess 3

Our inputs and outputs are of 4-bit decimal

A B C D W X Y Z values. You will have to make 4 K-Maps

0 (Consider W as independent function of

input variables A, B, C, D, Make K-Map and

1

simplify it). Arrive at the simplest

2 expression for each output.

3

4 W=

5 X=

6

Y=

7

8 Z=

9

EE221: Digital Logic Design Page 3

4. Draw the logic diagram for BCD to Excess-3 code converter using basic gates in the space

provided below.

5. Draw the logic diagram for BCD to Excess-3 code converter using NAND gates in the space

provided below.

EE221: Digital Logic Design Page 4

Choose the required gates out of the following gates.

Lab Tasks: (To be completed in the lab) 2 marks

Lab Task 1:

Realize the BCD to Excess-3 code converter using NAND gates only. Make the Schematic Diagram.

Show the results to your Teacher/Lab Engr.

EE221: Digital Logic Design Page 5

Lab Task 2:

Design and simulate the dataflow-level model of the circuit you patched. Give the code in the space

provided below.

EE221: Digital Logic Design Page 6

Anda mungkin juga menyukai

- Lab 9 Excess-3 To Gray Code Conversion Using Nand GatesDokumen6 halamanLab 9 Excess-3 To Gray Code Conversion Using Nand GatesZuha FatimaBelum ada peringkat

- DLD Lab 9Dokumen6 halamanDLD Lab 9Muhammad RehanBelum ada peringkat

- Lab 9 (Group 4) - 1Dokumen11 halamanLab 9 (Group 4) - 1MUHAMMAD HUZAIFABelum ada peringkat

- Lab 5 Pre LabDokumen10 halamanLab 5 Pre Labfatima razaBelum ada peringkat

- Lab5 BCD-to-Excess-3 Code Conversion2Dokumen10 halamanLab5 BCD-to-Excess-3 Code Conversion2Muhammad Tehsin Rashad0% (2)

- Lab6 BCD-to-Excess-3 Code ConversionDokumen7 halamanLab6 BCD-to-Excess-3 Code ConversionMuhammad Asad Khalil RaoBelum ada peringkat

- EE-221 Lab Report: BCD to Seven Segment Decoder with Multiplexed DisplayDokumen5 halamanEE-221 Lab Report: BCD to Seven Segment Decoder with Multiplexed DisplayAisha SheikhBelum ada peringkat

- pdf lab 2 dldDokumen13 halamanpdf lab 2 dldSana KhitranBelum ada peringkat

- Lab 6Dokumen15 halamanLab 6taimoor.asad.789Belum ada peringkat

- Project DLDDokumen3 halamanProject DLDHala QamareldeenBelum ada peringkat

- Lab3 Verilog FAM - NBCDokumen6 halamanLab3 Verilog FAM - NBCMuhammad HaroonBelum ada peringkat

- Lab8 2-Bit Binary Adder-SubtractorDokumen11 halamanLab8 2-Bit Binary Adder-SubtractorAhmed Razi UllahBelum ada peringkat

- Department of Electrical Engineering: Lab No # 2: Introduction To Verilog (CLO4, P3)Dokumen9 halamanDepartment of Electrical Engineering: Lab No # 2: Introduction To Verilog (CLO4, P3)Muhammad RehanBelum ada peringkat

- Digital Logic Design Lab ReportDokumen8 halamanDigital Logic Design Lab ReportMuhammad RehanBelum ada peringkat

- Lab 1Dokumen5 halamanLab 1tttm2609Belum ada peringkat

- Digital Logic Design (EL-227) : Laboratory Manual Spring-2020Dokumen5 halamanDigital Logic Design (EL-227) : Laboratory Manual Spring-2020Demin revisBelum ada peringkat

- BCD To Excess-3 Code Converter-EncoderDokumen2 halamanBCD To Excess-3 Code Converter-EncoderJunaid Iqbal50% (4)

- Introduction to Verilog HDL and logic circuit designDokumen6 halamanIntroduction to Verilog HDL and logic circuit designpioneer boysBelum ada peringkat

- Lab12 Voting Machine DesignDokumen6 halamanLab12 Voting Machine DesignMuneeb AsifBelum ada peringkat

- CSE369 Lab1&2 Wi22Dokumen5 halamanCSE369 Lab1&2 Wi22Deniz Melek TürkBelum ada peringkat

- Lab8 2-Bit Binary Adder-SubtractorDokumen5 halamanLab8 2-Bit Binary Adder-SubtractorMazoon ButtBelum ada peringkat

- Practice Problem 04Dokumen1 halamanPractice Problem 04Ali AlyamiBelum ada peringkat

- Lab 1 Familiarization With Digital Logic GatesDokumen7 halamanLab 1 Familiarization With Digital Logic Gatespioneer boysBelum ada peringkat

- HDL Lab SyllabusDokumen2 halamanHDL Lab Syllabussuhas RBelum ada peringkat

- Department of Software Engineering: Lab1: Familiarization of Basic Gates and Digital IcsDokumen14 halamanDepartment of Software Engineering: Lab1: Familiarization of Basic Gates and Digital IcsMuhammad RehanBelum ada peringkat

- Lab7: Part (A) : Design of 2-Out-Of-5 To BCD Code Converter With DisplayDokumen7 halamanLab7: Part (A) : Design of 2-Out-Of-5 To BCD Code Converter With DisplaySanan yaqoobBelum ada peringkat

- DLD - Lab13 OEL Report Group 2, 6Dokumen11 halamanDLD - Lab13 OEL Report Group 2, 6muibrahim.bee22seecsBelum ada peringkat

- Ee203 Midterm2Dokumen6 halamanEe203 Midterm2Marwan WahedBelum ada peringkat

- Dldlab6 justPreLabDokumen10 halamanDldlab6 justPreLabArfaat SanitaryBelum ada peringkat

- Lab12 Design of A Combinational Circuit (BCD To 7-Segment Decoder) ND Voting Machine DesignDokumen7 halamanLab12 Design of A Combinational Circuit (BCD To 7-Segment Decoder) ND Voting Machine DesignAisha SheikhBelum ada peringkat

- Question # 1 2 3 4 5 Total Total Marks 5 5 5 5 5 25 Obtained MarksDokumen11 halamanQuestion # 1 2 3 4 5 Total Total Marks 5 5 5 5 5 25 Obtained MarksFarah DurraniBelum ada peringkat

- Antennas and Wave Propagation Fourth EditionDokumen37 halamanAntennas and Wave Propagation Fourth EditionAsha JBelum ada peringkat

- Verilog LabDokumen70 halamanVerilog Labhkes rcrBelum ada peringkat

- Verilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation PrinciplesDokumen3 halamanVerilog HDL Basics Lab Assignments: Lab Work 1. Study of Module Declaration and Module Instantiation PrinciplesSindhu RajanBelum ada peringkat

- DLD Lab Practical Updated VersionDokumen2 halamanDLD Lab Practical Updated VersionAli SarmadBelum ada peringkat

- 7 Segment Display GuideDokumen12 halaman7 Segment Display Guidehieu minh TranBelum ada peringkat

- Design and Implement n-Bit Adder/SubtractorDokumen11 halamanDesign and Implement n-Bit Adder/SubtractorMuneeb ahmadBelum ada peringkat

- DLD Lab #07 DecoderDokumen3 halamanDLD Lab #07 Decodernkdhanani2Belum ada peringkat

- 5C7-Lab Manuals EE200 LabDokumen46 halaman5C7-Lab Manuals EE200 Labxavier_2010Belum ada peringkat

- Lab 3 (Verilog Implementation of Stop Light Controller)Dokumen7 halamanLab 3 (Verilog Implementation of Stop Light Controller)Muhtasim Fuad JeetBelum ada peringkat

- Lab Report 3Dokumen5 halamanLab Report 3Amin QureshiBelum ada peringkat

- Lab12 Design of A Combinational Circuit (BCD To 7-Segment Decoder) ND Voting Machine DesignDokumen7 halamanLab12 Design of A Combinational Circuit (BCD To 7-Segment Decoder) ND Voting Machine DesignAli HassanBelum ada peringkat

- Experiment No: 01 Name of The Experiment: Representing Logical Problems Through Truth Table and Deducing Logic Functions From Truth TableDokumen6 halamanExperiment No: 01 Name of The Experiment: Representing Logical Problems Through Truth Table and Deducing Logic Functions From Truth Tablemtim360Belum ada peringkat

- Design and Implement Combinational Logic CircuitsDokumen2 halamanDesign and Implement Combinational Logic CircuitsEU JUN HONGBelum ada peringkat

- Combinational Logic DesignDokumen31 halamanCombinational Logic DesignManav KaushalBelum ada peringkat

- HDL Manual 3 June 2022Dokumen83 halamanHDL Manual 3 June 2022Ram Kumar SinghBelum ada peringkat

- Ecgr2156 Experiment 3 Seven Segment DecoderDokumen6 halamanEcgr2156 Experiment 3 Seven Segment Decoderm shahBelum ada peringkat

- Lab # 03 Hierarchical Design Using Gate Level Modeling: ObjectivesDokumen7 halamanLab # 03 Hierarchical Design Using Gate Level Modeling: ObjectivesUsman janBelum ada peringkat

- Week1 Tutorial Chapter1 With SolutionDokumen57 halamanWeek1 Tutorial Chapter1 With SolutionCST2109168Belum ada peringkat

- LCST Lab Experiment 06Dokumen3 halamanLCST Lab Experiment 06keny amigableBelum ada peringkat

- EN6000 - Project - Oct - 2022 - NewDokumen24 halamanEN6000 - Project - Oct - 2022 - News.mahadrBelum ada peringkat

- Design of Very Large Scale Integration CircuitsDokumen15 halamanDesign of Very Large Scale Integration CircuitsStudentBelum ada peringkat

- Lecture2 Chapter3 - Five-Variable Function Simplification Using Map Method, Product-of-Sum (PoS) Simplification Using Map MethodDokumen32 halamanLecture2 Chapter3 - Five-Variable Function Simplification Using Map Method, Product-of-Sum (PoS) Simplification Using Map MethodDaniyal ChaudharyBelum ada peringkat

- DLD Exp 6 Student Manual PDFDokumen4 halamanDLD Exp 6 Student Manual PDFS M AkashBelum ada peringkat

- Department of Electrical Engineering: Lab 12: Sequence DetectorDokumen19 halamanDepartment of Electrical Engineering: Lab 12: Sequence DetectorArial96Belum ada peringkat

- C Programming for the Pc the Mac and the Arduino Microcontroller SystemDari EverandC Programming for the Pc the Mac and the Arduino Microcontroller SystemBelum ada peringkat

- Microcontroller Projects in C for the 8051Dari EverandMicrocontroller Projects in C for the 8051Penilaian: 5 dari 5 bintang5/5 (1)

- Advanced C++ Interview Questions You'll Most Likely Be AskedDari EverandAdvanced C++ Interview Questions You'll Most Likely Be AskedBelum ada peringkat

- Assignment 1Dokumen1 halamanAssignment 1Muhammad Asad Khalil RaoBelum ada peringkat

- EE215 Lecture 37, 38, 39 Applying MOSFET in Amplifier DesignDokumen28 halamanEE215 Lecture 37, 38, 39 Applying MOSFET in Amplifier DesignMuhammad Asad Khalil RaoBelum ada peringkat

- EE215 Lecture 37, 38, 39 Applying MOSFET in Amplifier DesignDokumen28 halamanEE215 Lecture 37, 38, 39 Applying MOSFET in Amplifier DesignMuhammad Asad Khalil RaoBelum ada peringkat

- EDC Lab 12Dokumen6 halamanEDC Lab 12Muhammad Asad Khalil RaoBelum ada peringkat

- Lab6 BCD-to-Excess-3 Code ConversionDokumen7 halamanLab6 BCD-to-Excess-3 Code ConversionMuhammad Asad Khalil RaoBelum ada peringkat

- EDC Lab 12Dokumen6 halamanEDC Lab 12Muhammad Asad Khalil RaoBelum ada peringkat

- EDC Lab 12Dokumen6 halamanEDC Lab 12Muhammad Asad Khalil RaoBelum ada peringkat

- Doppler EffectDokumen11 halamanDoppler EffectMuhammad Asad Khalil RaoBelum ada peringkat

- Semilog Paper For Bode Plots Graphg1 PDFDokumen1 halamanSemilog Paper For Bode Plots Graphg1 PDFrjkadivarBelum ada peringkat

- Radio Data Reference Book Jessop 1967Dokumen148 halamanRadio Data Reference Book Jessop 1967Cubelinho ResuaBelum ada peringkat

- Thursday Forenoon: Instant Examinations - June - 2018Dokumen6 halamanThursday Forenoon: Instant Examinations - June - 2018Gurusamy GuruBelum ada peringkat

- Week 1 - Topic: Chapter 2: The Foreign Exchange Market 21 March 2021Dokumen36 halamanWeek 1 - Topic: Chapter 2: The Foreign Exchange Market 21 March 2021Jenita singhBelum ada peringkat

- Very Good, Course Steered, Speed Rung, Engine Configuration, You Have the ConDokumen5 halamanVery Good, Course Steered, Speed Rung, Engine Configuration, You Have the ConRoger Medallon Bag-aoBelum ada peringkat

- Residency Programs in The USADokumen28 halamanResidency Programs in The USAAnastasiafynnBelum ada peringkat

- ServiceNow Certified System Administrator CSA Practice Test Set 2Dokumen76 halamanServiceNow Certified System Administrator CSA Practice Test Set 2Apoorv DiwanBelum ada peringkat

- Specification Table for Kindergarten English Cognitive Domain LevelsDokumen2 halamanSpecification Table for Kindergarten English Cognitive Domain LevelsStefany Jane PascualBelum ada peringkat

- PractService Level Agreement NEBDN National Diploma in Dental NursingiceDokumen21 halamanPractService Level Agreement NEBDN National Diploma in Dental NursingiceAdriana MihalachiBelum ada peringkat

- KA7630/KA7631: Fixed Multi-Output RegulatorDokumen6 halamanKA7630/KA7631: Fixed Multi-Output RegulatorTecnico GenioBelum ada peringkat

- Tropical Fruit CHAPTER-3Dokumen32 halamanTropical Fruit CHAPTER-3Jeylan FekiBelum ada peringkat

- Default Password For All TMNet Streamyx Supported ModemDokumen2 halamanDefault Password For All TMNet Streamyx Supported ModemFrankly F. ChiaBelum ada peringkat

- Assertive CommunicationDokumen5 halamanAssertive CommunicationAditi VaidBelum ada peringkat

- Pending 1667646640 ForeclosureSimulationDokumen2 halamanPending 1667646640 ForeclosureSimulationpramod roy0% (1)

- 9706 w12 Ms 23Dokumen7 halaman9706 w12 Ms 23Diksha KoossoolBelum ada peringkat

- The Works of Lord Byron, Vol. 3 - Hebrew Melodies, PoemsDokumen361 halamanThe Works of Lord Byron, Vol. 3 - Hebrew Melodies, Poemszpervan1Belum ada peringkat

- P&C Ep. 6. Seizure DisordersDokumen36 halamanP&C Ep. 6. Seizure DisordersYahmayah von TronchinBelum ada peringkat

- Gartner - Predicts 2021 - Accelerate - Results - Beyond - RPA - To - Hyperautomation-2020Q4Dokumen17 halamanGartner - Predicts 2021 - Accelerate - Results - Beyond - RPA - To - Hyperautomation-2020Q4Guille LopezBelum ada peringkat

- REPLACEMENT IDLER TIRE SPECIFICATIONSDokumen2 halamanREPLACEMENT IDLER TIRE SPECIFICATIONSLuis HumBelum ada peringkat

- Mind Map of "Architecture+Participation"Dokumen1 halamanMind Map of "Architecture+Participation"Maysan MamounBelum ada peringkat

- Logistics and Supply Chain ManagementDokumen6 halamanLogistics and Supply Chain ManagementJerson ßÖydBelum ada peringkat

- Programmable Logic Controller (PLC)Dokumen19 halamanProgrammable Logic Controller (PLC)Jason Sonido88% (8)

- Manual Videoporteiro Tuya Painel de Chamada 84218Dokumen6 halamanManual Videoporteiro Tuya Painel de Chamada 84218JGC CoimbraBelum ada peringkat

- Interest SwapsDokumen6 halamanInterest SwapsamiBelum ada peringkat

- Strategies of Literary TranslationDokumen7 halamanStrategies of Literary TranslationMuhammad J H AbdullatiefBelum ada peringkat

- ASA-RAC Application GuideDokumen15 halamanASA-RAC Application GuideIsrael Miranda Zamarca100% (2)

- Integral University Study & Evaluation Scheme B.Tech. CSE/ITDokumen16 halamanIntegral University Study & Evaluation Scheme B.Tech. CSE/ITQwt YwtwBelum ada peringkat

- Assignment: New Product Development PROJECT TITLE: Safety Alarm For Construction WorkerDokumen21 halamanAssignment: New Product Development PROJECT TITLE: Safety Alarm For Construction WorkerHazim ZakiBelum ada peringkat

- Arslan CVDokumen18 halamanArslan CVAwais NaeemBelum ada peringkat

- Miguel Angel Quimbay TinjacaDokumen9 halamanMiguel Angel Quimbay TinjacaLaura LombanaBelum ada peringkat

- CostingDokumen3 halamanCostingAarti JBelum ada peringkat