Accident Msging System

Diunggah oleh

Vivian ThomasDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Accident Msging System

Diunggah oleh

Vivian ThomasHak Cipta:

Format Tersedia

Accident Alert System

ABSTRACT

This project aims to develop a device that informs the control station if the

vehicle in which the device is fitted, met with a severe accident. This project is

implemented using an accelerometer sensor, which works using MEMS technology along

with GSM and GPS.The device has a micro controller connected to an Accelerometer

sensor, GPS module and GSM module. The software that is embedded in the micro

controller controls the various operations of the device.

The micro controller monitors the waveform from the accelerometer

sensor.The GPS module calculates the geographical position of the module. This helps in

detecting the location/longitude of the module. The GPS system functions on the basis of

NEMA protocol.

The device monitors the vibrations due to impact from the sensors that are

received as analog values. The user can feed the tolerance level of impact. If the level is

above the tolerance level (in case of accident), the device sends alert messages (SMS)

along with the location data from GPS module to the control station or to hospital using

the GSM module.The control station or hospital receives the message from the vehicle

through the GSM module, which helps to initiate the appropriate action.

ASIET, Kalady Page 1 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

1. INTRODUCTION

In search of our project we plan to do something, which is ye to be established and must

be useful to day to day life. We analyzed the current situation and realized that if there

may be system that informs the accidents at the right time, we will be able to save

thousands of precious life. So we decided to develop such a system that informs the

accidents to a station or the right person.

It is implemented using an accelerometer sensor which works using MEMS technology

along with GPS and GSM. The various operations of the device are controlled by the

software that is embedded in the microcontroller.

ASIET, Kalady Page 2 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

1.1 MICROCONTROLLERS AND MICROPROCESSORS

The contrast between a Microprocessor and Microcontroller is best exemplified

by the fact that most Microprocessors have many opcodes for moving data from external

memory to CPU; Microcontroller have one or two.

Microprocessor may have one or two types of bit handling instructions;

Microcontrollers will have many. Microprocessors are concerned with rapid movement

of code and data from external address to the chip. Microprocessor must have many

additional parts to be optional. Microcontrollers can function as a computer with addition

of no external digital parts.

Microprocessors are intended to be general purpose digital computer where as

Microcontroller are intended to be special purpose digital controllers. Microprocessors

contain a CPU, memory, addressing circuits and interrupt handling data. Microcontrollers

have these features as well as timers, parallel and serial I/O internal RAM and ROM.

1.2 INTRODUCTION TO EMBEDDED SYSTEMS

Embedded System is any electronic equipment with built in intelligence and

dedicated software. All embedded Systems use either a microprocessor or a micro

controller. The application of these controllers makes user-friendly cheaper solutions and

enables to add features otherwise impossible to provide by other means.

Embedded devices can be defined as any device with a microprocessor or

micro controller embedded in it that has a relatively focused functionality. The software

for the Embedded System is called firmware. The firmware is written in Assembly

language for time or resource critical operations or using higher-level languages like C or

Embedded C. The software will be simultaneously micro code simulations for the largest

processor. Since they are supported to perform only specific task, these programs are

stored in Read Only Memories (ROMs). Moreover they may need no or minimal inputs

from the user, hence the user interface like monitor, mouse & large keyboard etc. may be

absent.

ASIET, Kalady Page 3 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Embedded Systems are also known as Real time Systems since they respond to an input

or event and produce the result within the guaranteed time period. This time period can

be a few microseconds to days or months.

Embedded Systems Development:

In the development of Embedded System application the hardware and software

must go in hand in hand. The software created by the software engineers must be burnt

into or micro coded into the hardware or the micro controller produced by the VLSI

engineers. The micro controller and the software micro coded in it together form the

system for the particular application.

The software program for real time system is written either in assembly or high-

level language such as C. The assembly language is used in the case of tome critical

applications. Now day’s high-level languages replace most of the assembly language

constructs.

ASIET, Kalady Page 4 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

1.3 ADVANTAGES OF EMBEDDED SYSTEM

Higher performance: The integration of various ICs shortens the

traveling rout and time of data to be transmitted resulting in higher

performance.

Lower power consumption: The integration of various ICs eliminates

buffers and other interface circuits. As the number of components is

reduced, less power will be consumed.

Slimmer and more compact: Housed in a single separate package, the

chip is smaller in size and therefore occupies less space on the PCB. Hence

products using embedded system are slimmer and more compact.

Reduced design and development system: The system on a chip provides

all functionality required by the system. System designers need not worry

about the basic function of the system-right from the beginning of the

design phase, they can focus on the development features. As a result, the

time spends on research and development is reduced and this in turn

reduces the time to market of their products.

Lower system costs: In the past, several chips in separate packages were

required to configure a system. Now, just one system on-chip can replace

all of these, dramatically reducing the packaging cost.

ASIET, Kalady Page 5 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

2. OVERVIEW

2.1 PROJECT IDEA

The device monitors the vibrations due to impact from the sensors that are

received as analog values. The response level of the systems developed using MEMS

technology is very high say a few milliseconds. The tolerance level of impact can be fed

by the user to the system. If the level is above the tolerance level (in case of accidents),

the device sends alert messages (SMS) along with the location data from GPS module to

the control station or to hospital using the GSM module The control station or hospital

receives the message from the vehicle through the GSM module which helps to initiate

the appropriate action.

2.2 IMPORTANCE OF THIS SYSTEM

We are witnessing several accidents and severe injuries and deaths taking place

on road accidents in our day to day life. Most deaths due to accidents are caused by the

unavailability of sufficient treatments and medicine at the right time. If the vehicle is got

accident on a place where sufficient communication devices and resources are not

available, the problem will become more serious.

If we are able to inform the accident at the right time to right persons we may save many

valuable lives. There comes the importance of this project accident messaging system,

which detects the accident and informs it to the right person with sufficient details about

the place where accident occurred.

ASIET, Kalady Page 6 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

2.3 GENERAL BLOCK DIAGRAM

Satellite <<<< >>>>

<<<< >>>>

Mobi

le

Towe

r

Embedded System GSM

With

GPS Module, GSM Module

and MEMS Accelerometer

Sensor

Vehicle Control Station

Figure:2.1 General block diagram.

2.4 HOW DOES IT WORK

The prime use of the accident messaging system is to track the location of the

vehicle and inform the occurrence of accident with sufficient details like the exact

location and time at which accident happened. The system continuously tracks the exact

location of the vehicle on earth. A GPS receiver in the system helps to locate the

latitudinal and longitudinal position of the vehicle. An accelerometer sensor, connected

to the device helps to identify whether an accident occurred. For this the sensor value is

continuously compared with some safe value given by the user with the help of a

programmed microcontroller. If the accident is sensed, the microcontroller transfers the

ASIET, Kalady Page 7 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

GPS data along with a message of accident to the GSM module connected to the device.

The GSM module then sends this message to another GSM mobile phone whose number

is given by the user in the software.

ASIET, Kalady Page 8 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

3. BLOCK DIAGRAM

MEMS

IC PIC

LCD

MMA 16F877

2260D

GSM

LOGIC

USART

NAND

MAX232 GPS

GATES

ASIET, Kalady Page 9 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

4. REQUIREMENTS

Basic requirements for the project are hardware components and software to

control the overall functioning.

4.1 HARDWARE REQUIREMENTS

Hardware requirements includes,

• A GPS device to locate the vehicle on earth

• An accelerometer sensor to detect the occurrence of the accident

• A GSM modem to transmit the message to the rescuer’s handset

• A microcontroller which controls the overall working of the device incorporating

all

these components.

4.2 SOFTWARE REQUIREMENTS

For the proper functioning of the device, the microcontroller is programmed using

MPLAB IDE v5.2 Compiler software. The software for the device according to the

program flow is written, compiled and simulated on C in MPLAB C-compiler.

ASIET, Kalady Page 10 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

5. CIRCUIT DIAGRAM

ASIET, Kalady Page 11 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

5.1 CIRCUIT DESCRIPTION

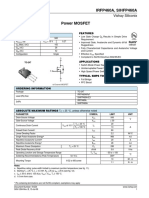

The circuit operations are controlled by the PIC 16F877 microcontroller. It also consists

of an accelerometer which is the MMA 2260D MEMS. The tracking is done by the GPS

receiver and a GSM module is also connected in order to send and receive messages. The

MAX 232 is the interfacing IC used in this circuit. Also an LCD controller and driver

HD44780U is used for the Display purposes. All these sections are explained below. The

power supply section consists of LM7805, diodes and capacitors. The GPS section is

powered with separate input. All the other ICs are powered from the same power supply

unit.

5.1.1 Micro-machined Accelerometer

To monitor the vibrations in the body of the vehicle we use a Micro-machined

Accelerometer- MMA 2260D. A 0.1 µF capacitor (C14) is connected to VDD to

decouple the power source. Place a ground plane beneath the accelerometer to reduce

noise, the ground plane should be attached to all internal VSS terminals. An RC filter of 1

kΩ (R5)and 0.1 µF(C13) is used on the output of the accelerometer to minimize clock

noise (from the switched capacitor filter circuit). Any external power supply switching

frequency should be selected such that they do not interfere with the internal

accelerometer sampling frequency. This will prevent aliasing errors.

ASIET, Kalady Page 12 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Accelerometer with Recommended Connection Diagram

5.1.2 PIC 16F877 Microcontroller

The PIC 16F877 uses a 20MHz crystal. The PIC16F87X can be operated in four different

oscillator modes. The user can program two configuration bits (FOSC1 and FOSC0) to

select one of these four modes

• LP Low Power Crystal

• XT Crystal/Resonator

• HS High Speed Crystal/Resonator

• RC Resistor/Capacitor

In XT, LP or HS modes a crystal or ceramic resonator is connected to the OSC1/CLKIN

and OSC2/CLKOUT pins to establish oscillation. The PIC16F87X Oscillator design

requires the use of a parallel cut crystal. Use of a series cut crystal may give a frequency

out of the crystal manufacturers specifications. When in XT, LP or HS modes, the device

can have an external clock source to drive the OSC1/CLKIN pin.The VDD pin is

connected to +5V. the capacitor C1 is used bypass ac to ground.

The PIC has used in half duplex synchronous mode since the reception and transmission

are not done at the same baud rate. It receives data continuously from GPS receiver at a

baud rate of 9600 and data is transmitted to GSM at a baud rate 115200 if required. Both

of these are connected to the PIC through pin no.26 (RC7) using MAX 232 as interfacing

IC. Therefore to switch from reception (GPS) to transmission (GSM) we use a logic

circuit made of 4 NAND gates. Depending on the state of pin no. 37(RB4) any one of

these are connected and data transfer takes place. The GSM and the GPS receiver is

connected to the interfacing IC.

5.1.3 G- mouse GPS Receiver

ASIET, Kalady Page 13 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

G-Mouse is a total solution GPS receiver (G-Mouse instead below), designed based on

most high sensitivity. This positioning application meets strict needs such as car

navigation, mapping, surveying, security, agriculture and so on. Only clear view of sky

and certain power supply are necessary to the unit. It communicates with other electronic

utilities via compatible dual-channel through MAX-232 or TTL and saves critical

satellite data by built–in backup memory. With low power consumption, the G-Mouse

tracks up to 8 satellites at a time, re-acquires satellite signals in 1 sec and updates position

data every second. 4 power saving mode allows the unit operates with ultra low power

request.

Advantage GPS module has is :-

• The module got high performance CPU Inside, allow users to design different

applications, store in the module, to provide the most economic solution for

anybody.

• High performance receiver tracks up to 8 satellites while providing first fast fix and

low power consumption.

• Compact design ideal for applications with minimal space.

• A rechargeable battery sustains internal clock and memory. The battery is

recharged during normal operation.

5.1.4 GSM Module

ASIET, Kalady Page 14 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

The GSM Module is a simple internal circuit of a mobile which can insert a sim in itself

and send messages. In this particular project the usage can be with a GSM module or

even a mobile handset. For convenience we are using a mobile handset with a data cable.

6. GPS

6.1 INTRODUCTION TO GPS

GPS, the Global Positioning System, is the only system today able to show you

your exact position on Earth at any time, any where, and in any weather. GPS satellites

orbit 11,000 nautical miles above Earth. They are monitored continuously at ground

stations located around the world. The satellites transmit signals that can be detected by

anyone with a GPS receiver.

The first GPS satellite was launched in 1978. The first 10 satellites launched were

developmental satellites, called Block I. From 1989 to 1997, 28 production satellites,

called Block II, were launched; the last 19 satellites in the series were updated versions,

called Block IIA. The launch of the 24th GPS satellite in 1994 completed the primary

system. The third-generation satellite, Block IIR, was first launched in 1997. These

satellites are being used to replace aging satellites in the GPS constellation. The next

generation, Block IIF, is scheduled for its first launch in late 2005.

6.2 ELEMENTS OF GPS

GPS has three parts: the space segment, the user segment, and the control

segment. The space segment consists of a constellation of 24 satellites plus some spares,

each in its own orbit 11,000 nautical miles above Earth. The user segment consists of

receivers, which user can hold in his hand or mount in a vehicle, like car, bus, etc. The

control segment consists of ground stations (five of them, located around the world) that

make sure the satellites are working properly. The master control station at Schriever Air

Force Base, near Colorado Springs, Colorado, runs the system.

ASIET, Kalady Page 15 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Figure 6.1 Elements of GPS

6.3 CONSTELLATION OF SATELLITES

An orbit is one trip in space around Earth. GPS satellites each take 12 hours to

orbit Earth. Each satellite is equipped with an atomic clock so accurate that it keeps time

to within three nanoseconds—that’s 0.000000003 or three-billionths of a second—to let it

broadcast signals that are synchronized with those from other satellites.

The signal travels to the ground at the speed of light. Even at this speed, the signal

takes a measurable amount of time to reach the receiver. The difference between the time

when the signal is received and the time when it was sent, multiplied by the speed of

light, enables the receiver to calculate the distance to the satellite. To calculate its precise

latitude longitude, and altitude, the receiver measures the distance to four separate GPS

satellites.

ASIET, Kalady Page 16 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

6.4 RECEIVERS

GPS receivers can be carried in your hand or be installed on aircraft, ships, tanks,

submarines, cars, and trucks. These receivers detect, decode, and process GPS satellite

signals. More than 100 different receiver models are already in use. The typical hand-

held receiver is about the size of a cellular telephone, and the newer models are even

smaller. The commercial hand-held units distributed to U.S. armed forces personnel

during the Persian Gulf War weighed only 28 ounces (less than two pounds). Since then,

basic receiver functions have been miniaturized onto integrated circuits that weigh about

one ounce.

6.4.1 GROUND STATION

The GPS control segment consists of several ground stations located around the

world:

• A master control station at Schriever Air Force Base in Colorado

• Five unstaffed monitor stations: Hawaii and Kwajalein in the Pacific Ocean; Diego

Garcia in the Indian Ocean; Ascension Island in the Atlantic Ocean; and Colorado

Springs, Colorado.

• Four large ground-antenna stations that send commands and data up to the satellites

and collect telemetry back from them.

ASIET, Kalady Page 17 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

6.5 WORKING OF GPS

Figure 6.2 Working of GPS

The principle behind GPS is the measurement of distance (or “range”) between

the satellites and the receiver. The satellites tell us exactly where they are in their orbits.

It works something like this: If we know our exact distance from a satellite in space, we

know we are somewhere on the surface of an imaginary sphere with a radius equal to the

distance to the satellite radius. If we know our exact distance from two satellites, we

know that we are located somewhere on the line where the two spheres intersect. And, if

we take a third and a fourth measurement from two more satellites, we can find our

location. The GPS receiver processes the satellite range measurements and produces its

position.

GPS uses a system of coordinates called WGS 84, which stands for World

Geodetic System 1984. It produces maps like the ones you see in school, all with a

common reference frame for the lines of latitude and longitude that locate places and

things. Likewise, it uses time from the United States Naval Observatory in Washington,

D.C., to synchronize all the timing elements of the system, much like Harrison's

chronometer was synchronized to the time at Greenwich.

ASIET, Kalady Page 18 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

6.6 GPS IN THIS PROJECT

In this project GPS is used for locating and tracking the vehicle. The GPS module

calculates the geographical position of the module. This helps in detecting the

location/position of the module.

The GPS system we are using here is G-Mouse GPS Receiver, FGPXMSR01.

Figure: 6..3 G-Mouse GPS Receiver, FGPXMSR01.

G-Mouse is a total solution GPS receiver (G-Mouse instead below), designed

based on most high sensitivity FirstGPSTM kernel architecture. This positioning

application meets strict needs such as car navigation, mapping, surveying, security,

agriculture and so on. Only clear view of sky and certain power supply are necessary to

the unit. It communicates with other electronic utilities via compatible dual-channel

through RS-232 or TTL and saves critical satellite data by built–in backup memory. With

low power consumption, the G-Mouse tracks up to 8 satellites at a time, re-acquires

satellite signals in 1 sec and updates position data every second. 4 power-saving mode

allows the unit operates with ultra low power request.

The GPS system functions on the basis of NMEA protocol. The NMEA protocol has

output messages and input messages. The module outputs several datas like Global

ASIET, Kalady Page 19 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

positioning system fixed data, Geographic position latitude/longitude, GNSS DOP and

active satellites, GNSS satellites in view and recommended minimum specific GNSS

data.

The protocol of G-Mouse is designed base on NMEA(National Marine Electronics

Association) 0183 ASCII format. The full protocol is defined in “NMEA 0183, Version

3.01” and “RTCM (Radio Technical Commission for Maritime Services). Through this

protocol, GPS gives the latitude and longitude position of the GPS module. Several

output messages are provided by the module in which we select Recommended Minimum

Specific GNSS Data (RMC).

An example format for the output message according to NMEA protocol will be as

shown.

$GPRMC,161229.487,A,3723.2475,N,12158.3416,W,0.13,309.62,120598, ,*10

Table3.1 RMC Data Format

In our project we receive the GPRMC data from the GPS module and stores in an

array by the software. Then by counting the number of bit positions, we store the latitude

and longitude values separately and attach with the message to be send by the GSM.

ASIET, Kalady Page 20 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

7. GSM

7.1 INTRODUCTION TO GSM

The Global System for Mobile Communications (GSM) is the most popular

standard for Mobile phones in the world. GSM service is used by over 1.5 billion people

across more than 210 countries and territories. The ubiquity of the GSM standard makes

international roaming very common between mobile phone operators, enabling

subscribers to use their phones in many parts of the world. GSM differs significantly

from its predecessors in that both signaling and speech channels are digital, which means

that it is considered a second generation (2G) mobile phone system. This fact has also

meant that data communication was built into the system from very early on. GSM is an

open standard which is currently developed by the 3GPP.

GSM is a cellular network, which means that mobile phones connect to it by

searching for cells in the immediate vicinity. GSM networks operate at various different

radio frequencies. Most GSM networks operate at 900 MHz or 1800 MHz. The exception

to the rule are networks in parts of the Americas (including the USA and Canada) that

operate at 850 MHz or 1900 MHz. In the 900 MHz band the uplink frequency band is

890-915 MHz, and the downlink frequency band is 935-960 MHz. This 25 MHz

bandwidth is subdivided into 124 carrier frequencies, each spaced 200 kHz apart. Time

division multiplexing is used to allow eight speech channels per Radio frequency

channel. There are eight burst periods grouped into what is called a TDMA frame. The

channel data rate is 270.833 kb/s, and the frame duration is 4.615 ms.

From the point of view of the consumer, the key advantage of GSM systems has

been higher digital voice quality and low cost alternatives to making calls such as text

messaging. The advantage for network operators has been the ability to deploy equipment

from different vendors because the open standard allows easy inter-operability. Also, the

standards have allowed network operators to offer roaming services which mean

subscribers can use their phone all over the world.

ASIET, Kalady Page 21 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

7.2 ARCHITECTURE OF THE GSM NETWORK

Figure:7.1 Architecture of GSM network

A GSM network is composed of several functional entities, whose functions and

interfaces are defined. Figure: 3.3.1 shows the layout of a generic GSM network. The

GSM network can be divided into three broad parts. The Mobile Station is carried by the

subscriber; the Base Station Subsystem controls the radio link with the Mobile Station.

The Network Subsystem, the main part of which is the Mobile services Switching Center,

performs the switching of calls between the mobile and other fixed or mobile network

users, as well as management of mobile services, such as authentication. Not shown is

the Operations and Maintenance center, which oversees the proper operation and setup of

ASIET, Kalady Page 22 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

the network. The Mobile Station and the Base Station Subsystem communicate across

the Um interface, also known as the air interface or radio link. The Base Station

Subsystem communicates with the Mobile service Switching Center across the A

interface.

7.2.1 MOBILE STATION

The mobile station (MS) consists of the physical equipment, such as the radio

transceiver, display and digital signal processors, and a smart card called the Subscriber

Identity Module (SIM). The SIM provides personal mobility, so that the user can have

access to all subscribed services irrespective of both the location of the terminal and the

use of a specific terminal. By inserting the SIM card into another GSM cellular phone,

the user is able to receive calls at that phone, make calls from that phone, or receive other

subscribed services.

The mobile equipment is uniquely identified by the International Mobile

Equipment Identity (IMEI). The SIM card contains the International Mobile Subscriber

Identity (IMSI), identifying the subscriber, a secret key for authentication, and other user

information. The IMEI and the IMSI are independent, thereby providing personal

mobility. The SIM card may be protected against unauthorized use by a password or

personal identity number.

7.2.2 BASE STATION SUBSYSTEM

The Base Station Subsystem is composed of two parts, the Base Transceiver

Station (BTS) and the Base Station Controller (BSC). These communicate across the

specified Abis interface, allowing (as in the rest of the system) operation between

components made by different suppliers.

The Base Transceiver Station houses the radio transceivers that define a cell and

handles the radio link protocols with the Mobile Station. In a large urban area, there will

potentially be a large number of BTSs deployed. The requirements for a BTS are

ruggedness, reliability, portability, and minimum cost.

ASIET, Kalady Page 23 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

The Base Station Controller manages the radio resources for one or more BTSs.

It handles radio channel setup, frequency hopping, and handovers, as described below.

The BSC is the connection between the mobile and the Mobile service Switching Center

(MSC). The BSC also translates the 13 kbps voice channel used over the radio link to the

standard 64 kbps channel used by the Public Switched Telephone Network or ISDN.

7.2.3 NETWORK SUBSYSTEM

The central component of the Network Subsystem is the Mobile services

Switching Center (MSC). It acts like a normal switching node of the PSTN or ISDN, and

in addition provides all the functionality needed to handle a mobile subscriber, such as

registration, authentication, location updating, handovers, and call routing to a roaming

subscriber. These services are provided in conjunction with several functional entities,

which together form the Network Subsystem. The MSC provides the connection to the

public fixed network (PSTN or ISDN), and signaling between functional entities uses the

ITUT Signaling System Number 7 (SS7), used in ISDN and widely used in current public

networks.

The Home Location Register (HLR) and Visitor Location Register (VLR),

together with the MSC, provide the call routing and (possibly international) roaming

capabilities of GSM. The HLR contains all the administrative information of each

subscriber registered in the corresponding GSM network, along with the current location

of the mobile. The current location of the mobile is in the form of a Mobile Station

Roaming Number (MSRN) which is a regular ISDN number used to route a call to the

MSC where the mobile is currently located. There is logically one HLR per GSM

network, although it may be implemented as a distributed database.

The Visitor Location Register contains selected administrative information from

the HLR, necessary for call control and provision of the subscribed services, for each

mobile currently located in the geographical area controlled by the VLR. Although each

functional entity can be implemented as an independent unit, most manufacturers of

switching equipment implement one VLR together with one MSC, so that the

geographical area controlled by the MSC corresponds to that controlled by the VLR,

ASIET, Kalady Page 24 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

simplifying the signaling required. Note that the MSC contains no information about

particular mobile stations - this information is stored in the location registers.

The other two registers are used for authentication and security purposes. The

Equipment Identity Register (EIR) is a database that contains a list of all valid mobile

equipment on the network, where each mobile station is identified by its International

Mobile Equipment Identity (IMEI). An IMEI is marked as invalid if it has been reported

stolen or is not type approved. The Authentication Center is a protected database that

stores a copy of the secret key stored in each subscriber's SIM card, which is used for

authentication and ciphering of the radio channel.

ASIET, Kalady Page 25 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

7.2.4 RADIO LINK ASPECTS

The International Telecommunication Union (ITU), which manages the

international allocation of radio spectrum (among other functions) allocated the bands

890-915 MHz for the uplink (mobile station to base station) and 935-960 MHz for the

downlink (base station to mobile station) for mobile networks in Europe. Since this

range was already being used in the early 1980s by the analog systems of the day, the

CEPT had the foresight to reserve the top 10 MHz of each band for the GSM network

that was still being developed. Eventually, GSM will be allocated the entire 2x25 MHz

bandwidth.

Since radio spectrum is a limited resource shared by all users, a method must be

devised to divide up the bandwidth among as many users as possible. The method

chosen by GSM is a combination of Time and Frequency Division Multiple Access

(TDMA/FDMA). The FDMA part involves the division by frequency of the total 25

MHz bandwidth into 124 carrier frequencies of 200 kHz bandwidth. One or more carrier

frequencies are then assigned to each base station. Each of these carrier frequencies is

then divided in time, using a TDMA scheme, into eight time slots. One time slot is used

for transmission by the mobile and one for reception. They are separated in time so that

the mobile unit does not receive and transmit at the same time, a fact that simplifies the

electronics.

Indoor coverage is also supported by GSM and is achieved by using power

splitters to deliver the radio signal from the antenna outdoors to a separate indoor antenna

distribution system. This is typically deployed when a lot of call capacity is needed

indoors, for example in shopping centers or airports. However, this is not a pre-requisite,

since indoor coverage is also provided by in-building penetration of the radio signal.

The modulation used in GSM is Gaussian minimum shift keying (GMSK), a kind of

continuous-phase frequency shift keying. In GMSK, the signal being modulated is

smoothened with a Gaussian low-pass filter prior to being fed to a frequency modulator,

which greatly reduces the interference to neighboring channels.

7.3 GSM IN THIS PROJECT

ASIET, Kalady Page 26 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

In this project GSM module is used to send the message containing the accident

information along with the latitude and longitude position of the module at the time of

accident. For that we use an ordinary GSM mobile hand set. The GSM module can be

controlled by certain commands called AT commands. Through our software we control

the GSM modem to generate and transmit text messages on to another GSM modem

specified in the program.

Example for the AT command are,

AT :- Sends to the module for detecting the proper working of the module.

ATE0 :- Command for turn off the echo.

AT+CMGF=1 :-Command for shifting module into text mode

AT+CMGS=”+91……….” :- Command for connecting to another module.

After sending the AT the module will return an OK message to show the proper

functioning of the module. If OK received then we will send the command ATE0

to the module to turn off the echoing of the commands. Then the command

AT+CMGF=1 shifts the module to the text mode. The module now returns

“>”.Then AT+CMGS = ”+91**********” command to select the number.

If “>” is received from the GSM module, type the SMS data and give Ctrl+Z.

This will send the SMS.

8. MEMS BASED ACCELEROMETER

8.1 INTRODUCTION TO MEMS TECHNOLOGY

Micro-Electro-Mechanical Systems (MEMS) is the integration of mechanical

elements, sensors, actuators, and electronics on a common silicon substrate through

ASIET, Kalady Page 27 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

microfabrication technology. While the electronics are fabricated using integrated circuit

(IC) process sequences (e.g., CMOS, Bipolar, or BICMOS processes), the

micromechanical components are fabricated using compatible "micromachining"

processes that selectively etch away parts of the silicon wafer or add new structural layers

to form the mechanical and electromechanical devices.

MEMS promises to revolutionize nearly every product category by bringing

together silicon-based microelectronics with micromachining technology, making

possible the realization of complete systems-on-a-chip. MEMS is an enabling technology

allowing the development of smart products, augmenting the computational ability of

microelectronics with the perception and control capabilities of microsensors and

microactuators and expanding the space of possible designs and applications.

Microelectronic integrated circuits can be thought of as the "brains" of a system

and MEMS augments this decision-making capability with "eyes" and "arms", to allow

microsystems to sense and control the environment. Sensors gather information from the

environment through measuring mechanical, thermal, biological, chemical, optical, and

magnetic phenomena. The electronics then process the information derived from the

sensors and through some decision making capability direct the actuators to respond by

moving, positioning, regulating, pumping, and filtering, thereby controlling the

environment for some desired outcome or purpose. Because MEMS devices are

manufactured using batch fabrication techniques similar to those used for integrated

circuits, unprecedented levels of functionality, reliability, and sophistication can be

placed on a small silicon chip at a relatively low cost.

ASIET, Kalady Page 28 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

8.1.1 ACCELEROMETERS

MEMS accelerometers are quickly replacing conventional accelerometers for

crash air-bag deployment systems in automobiles. The conventional approach uses

several bulky accelerometers made of discrete components mounted in the front of the

car with separate electronics near the air-bag; this approach costs over $50 per

automobile. MEMS and Nanotechnology has made it possible to integrate the

accelerometer and electronics onto a single silicon chip at a cost between $5 to $10.

These MEMS accelerometers are much smaller, more functional, lighter, more reliable,

and are produced for a fraction of the cost of the conventional macroscale accelerometer

elements.

8.2 PRINCIPLE OF OPERATION

The Motorola accelerometer is a surface micromachined integrated circuit

accelerometer. The device consists of a surface micromachined capacitive sensing cell

(g--cell) and a CMOS signal conditioning ASIC contained in a single integrated circuit

package. The sensing element is sealed hermetically at the wafer level using a bulk

micromachined “cap’’ wafer. The g-cell is a mechanical structure formed from

semiconductor materials (polysilicon) using semiconductor

Processes (masking and etching). It can be modeled as a set of beams attached to a

movable central mass that move between fixed beams. The movable beams can be

deflected from their rest position by subjecting the system to acceleration (Figure). As the

beams attached to the central mass move, the distance from them to the fixed beams on

one side will increase by the same amount that the distance to the fixed beams on the

other side decreases. The change in distance is a mea-sure of acceleration.

ASIET, Kalady Page 29 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Figure: 8.1 simplified transducer model

The g-cell beams form two back--to--back capacitors (Figure). As the central

mass moves with acceleration, the distance between the beams change and each

capacitor’s value will change, (C = NAε /D). Where A is the area of the facing side of

the beam, ε is the dielectric constant, D is the distance between the beams, and N is the

number of beams. The CMOS ASIC uses switched capacitor techniques to measure the

g--cell capacitors and extract the acceleration data from the difference between the two

capacitors. The ASIC also signal conditions and filters (switched capacitor) the signal,

providing a high level output voltage that is ratio-metric and proportional to acceleration.

8.3 ACCELEROMETER IN THIS PROJECT

Here we use the micromachined accelerometer IC - MMA2260D. The chip is

connected on the vehicle to be tracked in a manner that any shake on the vehicle should

be detected by the accelerometer. The block diagram for the chip is as shown below.

Figure: 8.2 Pinout diagram for MMA2260D

ASIET, Kalady Page 30 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Figure: 8.3 block diagram for MMA2260D.

The accelerometer IC produces a DC value from Vout as a result of the vibration

on the IC. This value is converted into digital value by the ADC in the processor and

compared with a user determined safe value by the software to check whether the

accident is occurred.

ASIET, Kalady Page 31 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9. THE MICROCONTROLLER (PIC16F877)

The core of the reader is PIC16f877. It has the name “Peripheral Interface

Controller”. The PIC uses the Harvard architecture. The 16F87X series micro controller

contains flash memory.

Harvard architecture has the program and data memory as separate memories and is

accessed from separate buses; this improves speed over the traditional Von Neumann

architecture in which the program and data are fetched from the same memory using the

same bus.

Harvard Architecture Von Neumann Arch.

Program

Program Data Memory

Memory Memory &

CPU CPU Data

Memory

Figure 4.2 Comparison of Harvard architecture Vs Von Neumann architecture.

ASIET, Kalady Page 32 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.1 PIN DIAGRAM

Figure 9.1 Pinout of PIC16F877

9.2 DEVICE STRUCTURE

Each part of as device can be placed in to one of three groups:

1. Core

2. Peripherals

3. Special features

9.2.1 THE CORE

The core pertains to the basic features that are required to make the device

operate. These include:

1. Device oscillator

2. Reset logic

3. CPU(Central Processing Unit)

4. ALU(Arithmetic and Logic Unit)

ASIET, Kalady Page 33 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

5. Device memory map organization

6. Interrupt operation

Figure 9.2 Block Diagram of PIC 16F877

ASIET, Kalady Page 34 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.2.2 PERIPHERALS

Peripherals are the features that add a differentiation from microprocessors. This

is in interfacing to the external world (such as general purpose I/O LCD drivers, A/D

inputs, and PWM outputs), and internal tasks such as keeping different time bases (such

as timers). The peripherals that are discussed are:

1.LCD

2.TIMER0

3.TIMER1

4. I/O PORTS

5.USART

6.ADC

9.2.3 SPECIAL FEATURES

Special features are the unique features that help to do one or more of the

following things:

• Decrease system cost.

• Increase system reliability.

• Increase design flexibility .

The midrange PIC Micro MCUs offer several features that help to achieve these goals.

The special features discussed are:

1. Device configuration bit.

2. On-chip Power-On Reset (POR).

3. Brown-out Reset (BOR) logic.

4. Watch dog timer.

5. Low power mode (sleep).

ASIET, Kalady Page 35 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.3 MEMORY VARIETIES

Memory technology has no effect on the logical operation of a device. Due to the

different processing step required, some electrical characteristic may vary between

devices with the same feature set / pin out but with different memory technologies. An

example is the electrical characteristic VIL (Input Law Voltage), which may have some

difference between a typical EPROM device and a typical ROM device. Each device has

a variety of frequency ranges and packaging options available. Depending on application

and production requirements, the proper device options can be identified using the

information in the Product Selection System section at the end of each data sheet.

1. C, as in PIC16CXXX. These devices have EPROM Type memory

2. CR, as in PIC16CRXXX. These devices have ROM type memory

3. F, as in PIC16FXXX. These devices have Flash type memory

9.3.1 EPROM

Microchip focuses on Erasable Programmable Read Only Memory (EPROM)

technology to give the customers flexibility throughout their entire design cycle. With

this technology Microchip offers various packaging options as well as services.

9.3.2 READ ONLY MEMORY (ROM) DEVICES

Microchip offers a masked read only memory version of the several of the highest

volume parts, thus giving customers a lower cost option for high volume, mature

products. ROM devices do not have serialization information in the program memory

space.

9.3.3 FLASH MEMORY DEVICES

These devices are electrically erasable, and can therefore be offered in a low cost

plastic package. Being electrically erasable, these devices can be both erased and

reprogrammed without removal from the circuit. A device will have the same

specifications whether it is used for prototype development, pilot programs, or

production.

ASIET, Kalady Page 36 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.4 OSCILLATOR

The PIC16F87X can be operated in four different oscillator modes. The user can

program two configuration bits (FOSC1 and FOSC0) to select one of these four modes:

• LP Low Power Crystal

• XT Crystal/Resonator

• HS High Speed Crystal/Resonator

• RC Resistor/Capacitor

In XT, LP or HS modes a crystal or ceramic resonator is connected to the

OSC1/CLKIN and OSC2/CLKOUT pins to establish oscillation .

Figure 9.3 Crystal / Ceramic Resonator Operation (Hs, Xt or Lp Osc Configuration)

9.5 RESET

9.5.1 POWER ON RESET (POR)

A power on reset pulse is generated on chip when VDD rise is detected to take

advantage of the POR, just tie the MCLR pin directly (or through a resistor) to VDD.

This will eliminate external RC components usually needed to create a Power On Reset.

A minimum rise time for VDD is required. When the device exits the reset condition

(begins normal operation), the device operating parameters (voltage, frequency,

temperature etc.) must be within their operating ranges, otherwise the device will not

function correctly. Ensure the delay is long enough to getting all parameters within

specification.

ASIET, Kalady Page 37 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.5.2 BROWN-OUT RESET (BOR)

On-chip Brown-out Reset Circuitry places the device in to reset when the device

voltage falls below a trip point (ßVDD). This ensures that the device does not continue

program execution outside the valid operation range of the device. Brown-out Resets are

typically used in AC line applications or large battery applications where large loads may

be switched in (such as automotive), and cause the device voltage to temporarily fall

below the specified operating minimum.

9.6 WATCH DOG TIMER

PIC Microcontroller have a Watchdog Timer which can be shut off only through

configuration bits. It runs off its own RC oscillator for added reliability. There are two

timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer

(OST), intended to keep the chip in reset until the crystal oscillator is stable. The other is

the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on

power-up only, designed to keep the part in reset while the power supply stabilizes. With

these two timers on-chip, most applications need no external reset circuitry. During

normal operation, a WDT time-out generates a device RESET (Watchdog Timer Reset).

If the device is in SLEEP mode, a WDT time-out causes the device to wake-up and

continue with normal operation (Watchdog Timer Wake-up). The TO bit in the STATUS

register will be cleared upon a Watchdog Timer time-out.

9.7 LOW POWER MODE (SLEEP)

SLEEP mode is designed to offer a very low current power-down mode. The user

can wake-up from SLEEP through external reset, Watchdog Timer Wake-up, or through

an interrupt. Several oscillator options are also made available to allow the part to fit the

application. The RC oscillator option saves system cost while the LP crystal option saves

power. A set of configuration bits are used to select various options.

9.8 MEMORY ORGANIZATION

There are two blocks in memory organization; Program memory and data

memory. Each block has its own so that access to each block can occur during the same

oscillator cycle. The data memory can further be broken down in to General Purpose

RAM and the Special Function Registers (SFR). The operations of the SFRs that control

the “core” are described here.

ASIET, Kalady Page 38 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.8.1 PROGRAM MEMORY ORGANISATION

The PIC16F87X PIC micros have a 13-bit program counter capable of addressing

an 8K x 14 program memory space. The PIC16F877/876 devices have 8K x 14 words of

FLASH program memory and the PIC16F873/874 devices have 4K x 14. Accessing a

location above the physically implemented address will cause a wraparound. The reset

vector is at 0000h and the interrupt vector is at 0004h.

9.8.2 ARCHITECTURAL PROGRAM MEMORY & STACK

Figure9.4 PIC 16F877 Program Memory Map and Stack

9.8.3 DATA MEMORY ORGANISATION

The data memory is partitioned into multiple banks which contain the General

Purpose Registers and the Special Function Registers. Bits RP1 and RP0 are the bank

select bits.

ASIET, Kalady Page 39 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Figure 9.5 Bank Selection

Each bank extends up to 7Fh (128 bytes). The lower locations of each bank are

reserved for the Special Function Registers. Above the Special Function Registers are

General Purpose Registers, implemented as static RAM. All implemented banks contain

special function registers. Some “high use” special function registers from one bank may

be mirrored in another bank for code reduction and quicker access.

STATUS Register

ASIET, Kalady Page 40 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.8.4 GENERAL PURPOSE REGISTER FILE

The register file can be accessed either directly or indirectly through the File

Select Register FSR.

9.8.4.1 SPECIAL FUNCTION REGISTERS

The Special Function Registers are registers used by the CPU and Peripheral

Modules for controlling the desired operation of the device. These registers are

implemented as static RAM. SFR (Special Function Registers) are allocated at 32 bytes

from the head of each bank. After the 33rd byte is the register area which is possible to

use freely. The size is 96 bytes of each bank. However, bank 3 and bank 4 are the

contents which are the same as bank 0 and bank 1 respectively (the mirror). So, the size

which can be substantively used is 192 bytes for 2 banks.

The special function registers can be classified into two sets; core (CPU) and

peripheral

9.9 PORTS

Some pins for these I/O ports are multiplexed with an alternate function for the

peripheral features on the device. In general, when a peripheral is enabled, that pin may

not be used as a general purpose I/O pin. There are three ports –PORTA, PORTB,

PORTC, PORTD and PORTE.

9.9.1 PORTA AND THE TRISA REGISTER

PORTA is a 6-bit wide bi-directional port. The corresponding data direction

register is TRISA. Setting a TRISA bit (=1) will make the corresponding PORTA pin an

input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a

TRISA bit (=0) will make the corresponding PORTA pin an output, i.e., put the contents

of the output latch on the selected pin. Reading the PORTA register reads the status of

the pins whereas writing to it will write to the port latch. All write operations are read-

modify-write operations. Therefore a write to a port implies that the port pins are read,

this value is modified, and then written to the port data latch. Pin RA4 is multiplexed

with the Timer0 module clock input to become the RA4/T0CKI pin. The RA4/T0CKI pin

is a Schmitt Trigger input and an open drain output. All other RA port pins have TTL

input levels and full CMOS output drivers. Other PORTA pins are multiplexed with

analog inputs and analog VREF input. The operation of each pin is selected by

ASIET, Kalady Page 41 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

clearing/setting the control bits in the ADCON1 register (A/D Control Register1). The

TRISA register controls the direction of the RA pins, even when they are being used as

analog inputs. The user must ensure the bits in the TRISA register are maintained set

when using them as analog inputs.

9.9.2 PORTB AND THE TRISB REGISTER

PORTB is an 8-bit wide bi-directional port. The corresponding data direction

register is TRISB. Setting a TRISB bit (=1) will make the corresponding PORTB pin an

input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a

TRISB bit (=0) will make the corresponding PORTB pin an output, i.e., put the contents

of the output latch on the selected pin. Three pins of PORTB are multiplexed with the

Low Voltage Programming function; RB3/PGM, RB6/PGC and RB7/PGD.

Each of the PORTB pins has a weak internal pull-up. A single control bit can turn on all

the pull-ups. This is performed by clearing bit RBPU (OPTION_REG<7>). The weak

pull-up is automatically turned off when the port pin is configured as an output. The pull-

ups are disabled on a Power-on Reset.

Four of PORTB’s pins, RB7:RB4, have an interrupt on change feature. Only pins

configured as inputs can cause this interrupt to occur (i.e. any RB7:RB4 pin configured as

an output is excluded from the interrupt on change comparison). The input pins (of

RB7:RB4) are compared with the old value latched on the last read of PORTB. The

“mismatch” outputs of RB7:RB4 are OR’ed together to generate the RB Port Change

Interrupt with flag bit RBIF (INTCON<0>). This interrupt can wake the device from

SLEEP. The user, in the interrupt service routine, can clear the interrupt in the following

manner:

a) Any read or write of PORTB. This will end the mismatch condition.

b) Clear flag bit RBIF.

A mismatch condition will continue to set flag bit RBIF. Reading PORTB will

end the mismatch condition, and allow flag bit RBIF to be cleared. The interrupt on

change feature is recommended for wake-up on key depression operation and operations

where PORTB is only used for the interrupt on change feature. Polling of PORTB is not

recommended while using the interrupt on change feature.

ASIET, Kalady Page 42 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.9.3 PORTC AND THE TRISC REGISTER

PORTC is an 8-bit wide bi-directional port. The corresponding data direction

register is TRISC. Setting a TRISC bit (=1) will make the corresponding PORTC pin an

input, i.e., put the corresponding output driver in a hi-impedance mode. Clearing a

TRISC bit (=0) will make the corresponding PORTC pin an output, i.e., put the contents

of the output latch on the selected pin.PORTC is multiplexed with several peripheral

functions. PORTC pins have Schmitt Trigger input buffers.

When the I2C module is enabled, the PORTC (3:4) pins can be configured with

normal I2C levels or with SMBUS levels by using the CKE bit (SSPSTAT <6>). When

enabling peripheral functions, care should be taken in defining TRIS bits for each

PORTC pin. Some peripherals override the TRIS bit to make a pin an output, while other

peripherals override the TRIS bit to make a pin an input. Since the TRIS bit override is in

effect while the peripheral is enabled, read-modify write instructions (BSF, BCF,

XORWF) with TRISC as destination should be avoided. The user should refer to the

corresponding peripheral section for the correct TRIS bit settings.

9.9.4 ANALOG TO DIGITAL CONVERTER

PIC16F877

The PIC analog-to-digital converter has the idealized transfer function. It converts

an input voltage to an 8-bit number. The input voltage is scaled against a reference

voltage, Vref, producing the 8-bit output.

Working

Configure the A/D module:

Configure analog pins/voltage reference and

digital I/O (ADCON1)

Select A/D input channel (ADCON0)

Select A/D conversion clock (ADCON0)

Turn on A/D module (ADCON0)

Configure A/D interrupt (if desired):

ASIET, Kalady Page 43 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Clear ADIF bit

Set ADIE bit

Set PEIE bit

Set GIE bit

Wait the required acquisition time.

Start conversion:

Set GO/DONE bit (ADCON0)

Wait for A/D conversion to complete, by either:

Polling for the GO/DONE bit to be cleared

(With interrupts enabled); OR

Waiting for the A/D interrupts

Read A/D result register pair (ADRESH: ADRESL) clears bit ADIF if required.

For the next conversion, go to step 1 or step 2,

As required. The A/D conversion time per bit is

Defined as TAD. A minimum wait of 2TAD is

Required before the next acquisition starts.

ASIET, Kalady Page 44 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Figure 9.6 ADC

ASIET, Kalady Page 45 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.10 LCD DISPLAY

LCDs are the materials, which combine both the properties of both liquids and

crystals. Rather than having melting points, they have a temp range within which the

molecules are almost as mobile as they would be in liquid, but are grouped together in an

ordered form similar to a crystal .LCD would not generate light but scatter light. It

consumes less power.

Recent LCDs are field effect LCDs. They are based on optical action of polarized

light on properly oriented liquid crystal. LCD consists of 2 glass panels within the liquid

crystal material sand witched between them. The inner surface of glass plates are coated

with transparent electrodes which defines the character, symbols or patterns to be

displayed. The polymeric layers are present in between the electrodes and the liquid

crystal which makes the liquid crystal molecules to maintain a defined orientation angle.

The polarizer would rotate the light rays passing through them to a defined angle, in a

particular direction.

When the LCD is in OFF state, the 2 polarizer’s and the liquid crystals rotates the

light rays, such that the light rays come out the LCD without any orientation and hence

the LCD appear to be transparent. When sufficient light is applied to the electrodes, the

liquid crystal molecules would be aligned in specific direction. The light rays passing

through the LCD would be rotated by the polarizer which would result in

activating/highlighting the desired character .The LCDs are light weight with a few

millimeter thickness. They are compatible with low power electronic circuits. The LCD

display used here is HD44780U dot matrix display. The LCD It is 5*7 matrix display. It

is a 16*2 display. The data we are sending are put into Data Display RAM. At power on

the Data Display RAM is empty. After that the data is displayed. The maximum size of

DDRAM is 80 bytes. There are two rows each of 40 bytes. But at a particular time 16 at

top and 16 at bottom can be displayed. There is a pointer (address counter) .The address

counter is initially zero. The data to be displayed are put into location pointed by the

address counter. It is automatically incremented. There is a register select, which decides

whether it is a data or command.

If RS=1, then it is a data. If RS=0, then it is a command. Then the controller

processes it. After each command or data send to LCD it takes some time for execution.

ASIET, Kalady Page 46 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

During this time the LCD won’t take any data. There is a busy signal given by the LCD.

Busy signal is MSB of the data bus. So the user has to call the data bus to see that busy is

low before sending next data. For reliable Performance LCD has to be initialized. At

power on microcontroller sends some commands to LCD for proper initialization.

The commands for LCD initialization are

38- Two row 8-bit interface.

01-clear display. It clears DDRAM

0C-turns off display cursor

06- Increment the cursor position automatically

LCD accepts any command or data only if it is enabled. The EN signal has to be

made high and then send data or command and then disable it.

ASIET, Kalady Page 47 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

9.11 UNIVERSAL SYNCHRONOUS ASYNCHRONOUS

RECEIVER TRANSMITTER (USART)

The Universal Synchronous Asynchronous Receiver Transmitter (USART) module

is one of the two serial I/O modules. (USART is also known as a Serial Communications

Interface or SCI). The USART can be configured as a full duplex asynchronous system

that can communicate with peripheral devices such as CRT terminals and personal

computers, or it can be configured as a half duplex synchronous system that can

communicate with peripheral devices such as A/D or D/A integrated circuits, serial

EEPROMs etc. The USART can be configured in the following modes:

• Asynchronous (full duplex)

• Synchronous - Master (half duplex)

• Synchronous - Slave (half duplex)

Bit SPEN (RCSTA<7>) and bits TRISC<7:6> have be set in order to configure

pins RC6/TX/CK and RC7/RX/DT as the Universal Synchronous asynchronous

Receiver Transmitter.The USART module also has a multi-processor communication

capability using 9-bit address detection.

TXSTA-TRANSMIT STATUS AND CONTROL REGISTER

bit 7: CSRC: Clock Source Select bit

Asynchronous mode

Don’t care

Synchronous mode

1 = Master mode (Clock generated internally from BRG)

0 = Slave mode (Clock from external source)

bit 6: TX9: 9-bit Transmit Enable bit

1 = Selects 9-bit transmission

0 = Selects 8-bit transmission

ASIET, Kalady Page 48 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

bit 5: TXEN: Transmit Enable bit

1 = Transmit enabled

0 = Transmit disabled

Note: SREN/CREN overrides TXEN in SYNC mode.

bit 4: SYNC: USART Mode Select bit

1 = Synchronous mode

0 = Asynchronous mode

bit 3: Unimplemented: Read as '0'

bit 2: BRGH: High Baud Rate Select bit

Asynchronous mode

1 = High speed

0 = Low speed

Synchronous mode

Unused in this mode

bit 1: TRMT: Transmit Shift Register Status bit

1 = TSR empty

0 = TSR full

bit 0: TX9D: 9th bit of transmit data. Can be parity bit.

RXSTA-RECEIVE STATUS AND CONTROL REGISTER

bit 7: SPEN: Serial Port Enable bit

1 = Serial port enabled (Configures RC7/RX/DT and RC6/TX/CK pins as serial port

pins)

ASIET, Kalady Page 49 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

0 = Serial port disabled

bit 6: RX9: 9-bit Receive Enable bit

1 = Selects 9-bit reception

0 = Selects 8-bit reception

bit 5: SREN: Single Receive Enable bit

Asynchronous mode

Don’t care

Synchronous mode - master

1 = Enables single receive

0 = Disables single receive

This bit is cleared after reception is complete.

Synchronous mode - slave

Unused in this mode

bit 4: CREN: Continuous Receive Enable bit

Asynchronous mode

1 = Enables continuous receive

0 = Disables continuous receive

Synchronous mode

1 = Enables continuous receive until enable bit CREN is cleared (CREN overrides

SREN)

0 = Disables continuous receive

bit 3: ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1)

1 = Enables address detection, enable interrupt and load of the receive burffer when

RSR<8>

0 = Disables address detection, all bytes are received, and ninth bit can be used as parity

bit

bit 2: FERR: Framing Error bit

1 = Framing error (Can be updated by reading RCREG register and receive next valid

byte)

0 = No framing error

ASIET, Kalady Page 50 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

bit 1: OERR: Overrun Error bit

1 = Overrun error (Can be cleared by clearing bit CREN)

0 = No overrun error

bit 0: RX9D: 9th bit of received data (Can be parity bit)

USART Asynchronous Mode

In this mode, the USART uses standard non-return-tozero (NRZ) format (one start

bit, eight or nine data bits, and one stop bit). The most common data format is 8 bits. An

on-chip, dedicated, 8-bit baud rate generator can be used to derive standard baud rate

frequencies from the oscillator. The USART transmits and receives the LSb first. The

USART’s transmitter and receiver are functionally independent, but use the same data

format and baud rate. The baud rate generator produces a clock either x16 or x64 of the

bit shift rate, depending on bit BRGH (TXSTA<2>). Parity is not supported by the

hardware, but can be implemented in software (and stored as the ninth data bit).

Asynchronous mode is stopped during SLEEP. Asynchronous mode is selected by

clearing bit SYNC (TXSTA<4>).The USART Asynchronous module consists of the

following important elements:

• Baud Rate Generator

• Sampling Circuit

• Asynchronous Transmitter

• Asynchronous Receiver

9.11.1 USART ASYNCHRONOUS TRANSMITTER

The USART transmitter block diagram is shown . The heart of the transmitter is

the transmit (serial) shift register (TSR). The shift register obtains its data from the

read/write transmit buffer, TXREG. The TXREG register is loaded with data in software.

The TSR register is not loaded until the STOP bit has been transmitted from the previous

load. As soon as the STOP bit is transmitted, the TSR is loaded with new data from the

TXREG register (if available). Once the TXREG register transfers the data to the TSR

register (occurs in one TCY), the TXREG register is empty and flag bit TXIF (PIR1<4>)

is set. This interrupt can be enabled/disabled by setting/clearing enable bit TXIE

ASIET, Kalady Page 51 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

( PIE1<4>). Flag bit TXIF will be set, regardless of the state of enable bit TXIE and

cannot be cleared in software. It will reset only when new data is loaded into the TXREG

register. While flag bit TXIF indicates the status of the TXREG register, another bit

TRMT (TXSTA<1>) shows the status of the TSR register. Status bit TRMT is a read

only bit, which is set when the TSR register is empty. No interrupt logic is tied to this bit,

so the user has to poll this bit in order to determine if the TSR register is empty.

Transmission is enabled by setting enable bit TXEN(TXSTA<5>). The actual

transmission will not occur until the TXREG register has been loaded with data and the

baud rate generator (BRG) has produced a shift clock (Figure 10-2). The transmission can

also be started by first loading the TXREG register and then setting enable bit TXEN.

Normally, when transmission is first started, the TSR register is empty. At that point,

transfer to the TXREG register will result in an immediate transfer to TSR, resulting in an

empty TXREG. A back-to-back transfer is thus possible Clearing enable bit TXEN

during a transmission will cause the transmission to be aborted and will reset the

transmitter. As a result, the RC6/TX/CK pin will revert to hi-impedance.In order to select

9-bit transmission, transmit bit TX9 (TXSTA<6>) should be set and the ninth bit should

be written to TX9D (TXSTA<0>). The ninth bit must be written before writing the 8-bit

data to the TXREG register.This is because a data write to the TXREG register can result

in an immediate transfer of the data to the TSR register (if the TSR is empty). In such a

case, an incorrect ninth data bit may be loaded in the TSR register.

ASIET, Kalady Page 52 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Steps to follow when setting up an Asynchronous Transmission:

1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is

desired, set bit BRGH

2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

3. If interrupts are desired, then set enable bit TXIE.

4. If 9-bit transmission is desired, then set transmit bit TX9.

5. Enable the transmission by setting bit TXEN, which will also set bit TXIF.

6. If 9-bit transmission is selected, the ninth bit should be loaded in bit TX9D.

7. Load data to the TXREG register (starts transmission).

9.11.2 USART ASYNCHRONOUS RECEIVER

The receiver block diagram is shown.. The data is received on the RC7/RX/DT

pin and drives the data recovery block. The data recovery block is actually a high speed

shifter operating at x16 times the baud rate, whereas the main receive serial shifter

operates at the bit rate or at FOSC.Once synchronous is selected, reception is enabled by

setting bit CREN (RCSTA<4>).The heart of the receiver is the receive (serial) shift

register (RSR). After sampling the STOP bit, the received data in the RSR is transferred

to the RCREG register (if it is empty). If the transfer is complete, flag bit RCIF

(PIR1<5>) is set. The actual interrupt can be enabled/ disabled by setting/clearing enable

bit RCIE (PIE1<5>).

Flag bit RCIF is a read only bit which is cleared by the hardware. It is cleared

when the RCREG register has been read and is empty. The RCREG is a double buffered

register (i.e. it is a two deep FIFO). It is possible for two bytes of data to be received and

transferred to the RCREG FIFO and a third byte to begin shifting to the RSR register. On

the detection of the STOP bit of the third byte, if he RCREG register is still full, the

overrun error bit OERR (RCSTA<1>) will be set. The word in the RSR will be lost. The

RCREG register can be read twice to retrieve the two bytes in the FIFO. Overrun bit

OERR has to be cleared in software. This is done by resetting the receive logic (CREN is

cleared nd then set). If bit OERR is set, transfers from the RSR register to the RCREG

ASIET, Kalady Page 53 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

register are inhibited, so it is essential to clear error bit OERR if it is set. Framing error

bit FERR (RCSTA<2>) is set if a stop bit is detected as clear. Bit FERR and the 9th

receive bit are buffered the same way as the receive data. Reading the RCREG will load

bits RX9D and FERR with new values, therefore it is essential for the user to read the

RCSTA register before reading RCREG register in order not to lose the old FERR and

RX9D information.

Steps to follow when setting up an Asynchronous Reception:

1. Initialize the SPBRG register for the appropriate baud rate. If a high speed baud rate is

desired, set bit BRGH.

2. Enable the asynchronous serial port by clearing bit SYNC and setting bit SPEN.

3. If interrupts are desired, then set enable bit RCIE.

4. If 9-bit reception is desired, then set bit RX9.

5. Enable the reception by setting bit CREN.

6. Flag bit RCIF will be set when reception is complete and an interrupt will be generated

if enable bit RCIE is set.

7.Read the RCSTA register to get the ninth bit (if enabled) and determine if any error

occurred during reception.

8. Read the 8-bit received data by reading the RCREG register.

9. If any error occurred, clear the error by clearing enable bit CREN.

ASIET, Kalady Page 54 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

10. SOFTWARE

10.1 FLOW CHART

Start

Initialize variables and

registers for ADC,

USART,LDC

Give the

name of

project on

LCD

Initialize GSM module

using AT commands.

Switch it to text mode.

Switch to GPS

receiver.Read data

from GPS receiver and

store the required data.

Read the sensor value.

Switch to GSM module.

No sensor Yes send the message

value ,vehicle no.,and data

>safe from GPS(position) to

level the specified cell

number.

ASIET, Kalady Page 55 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

10.2 PROGRAM

11. CONCLUSION

This accident messaging system is a very important accessory to sense the

accidents at the time of occurrence. Now a day we can see that lot of life spoil in every

accidents. By using our system we can start rescue operations within a few minutes. Thus

we can save lot of lives.We may hope that future technologies will bring efficient and

reliable operation of the device. We dedicate this project to the people who lost their lives

in road accidents.

ASIET, Kalady Page 56 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

ADVANTAGES

Information can be send to the control station immediately.

Tracks the position of the vehicle.

Saves life.

Device is compact in size.

DRAWBACKS

Needs thorough knowledge about complex low level language.

Expensive GPS module.

ASIET, Kalady Page 57 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

APPENDIX

13.1 INSTRUCTION SET OF PIC16F877

ADDWF Add W and f

Syntax: [label] ADDWF f, d

Operands: 0 ≤ f ≤ 127

d € [0,1]

Operation: (W) + (f) → destination

Status Affected: C, DC, Z

Description: Add the contents of the W register with register ‘f ’. If‘d’ is 0 the results is

stored in the W register. If‘d’ is 1 the result is stored back in register ‘f ’.

ANDWF AND W with f

Syntax: [label] ANDWF f,d

Operands: 0 ≤ f ≤ 127

d € [0,1]

Operation: (W).AND. (f) → destination

Status Affected: Z

Description: AND the contents of the W register with register ‘f ’. If‘d’ is 0 the

results is stored in the W register. If‘d’ is 1 the result is stored back in register ‘f ’.

CLRF Clear f

ASIET, Kalady Page 58 of 73

Dept. of Electronics and Communication Engg.

Accident Alert System

Syntax: [label] CLRF f

Operands: 0 ≤ f ≤ 127

Operation: 00h → f

Status Affected: Z

Description: The contents of the register ‘f’ are cleared and the Z bit is sets stored in