DAC Utilizing ADC

Diunggah oleh

elfrichDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

DAC Utilizing ADC

Diunggah oleh

elfrichHak Cipta:

Format Tersedia

AUTHOR: VASILIOS THEODOROU KEYWORDS: ADC, DAC, PULL-UP

DESIGN NOTE

#033

DAC Utilizing ADC

This document is originally distributed by AVRfreaks.net, and may be distributed, reproduced, and modified without restrictions. Updates and additional design notes can be found at: www.AVRfreaks.net

Introduction

This design note describes a way to produce an analog voltage which is proportional to an 10-bit digital word. In other words, the design note describes how we can create a Digital-to-Analog Converter by utilizing the Analog-to-Digital Converter as well as some other hardware peripherals which are already present in several members of the AVR family. As it is commonly known the AVR microcontrollers does not include any kind of integrated DAC. However there are many ways to build DACs using vital resources of the micro, i.e., a free output port or a PWM channel on the accompanying timer. Obviously the DAC should be attended of a kind of software which is absolutely necessary for the proper operation. Clearly DAC can be implemented only in those devices which have an internal ADC (ATtiny15, AT90S4433, AT90S8535). For the operation of the DAC only an external RC network is required. Typical values for the components of the net are 10K and 100 nF for the resistor and the capacitor respectively. The unconnected resistor lead must be connected to an unused I/O line (in our code PORTA.0). The common lead of the resistor and the capacitor which is the VOUT of the DAC must be connected simultaneously to an ADC input (in our code PORTA.1/ADC1). The remaining capacitor lead goes to ground. The software operates the ADC in Free Running mode. Thus the valuable hardware resources such as Timer, PWM and the comparator are not involved in the DAC operation. Only the ADC interrupt complete vector is needed which in many cases is not a huge trade-off. While the Analog-to-Digital conversion is complete the corresponding interrupt is invoked and the interrupt service routine is executed. In that routine the 10bit result is compared to the desired output voltage. In case that the output voltage is smaller than the desired the internal pull-up of PORTA.0 pin is activated and the capacitor is charged via the resistor. The pull-up is deactivated in case the desired voltage is achieved or the output voltage is bigger than those expected. In the second case the capacitor is discharged gradually via the resistor. The output ripple can be trimmed to acceptable levels for a specific application. However note that the above described DAC is not ideal. Moreover the ripple varies in relation to the desired output voltage due to the non linear nature of the capacitor charge. At any case the ripple can be eliminated by setting the ADC prescaler to an appropriate value.

Overview

www.AVRfreaks.net

1 Design Note #033 Date: 06/02

Figure 1. RC Network

PORTA.0 10 K PORTA.1/ADC1 VOUT 100nF

AVR

Code

;-------------------------------------------------------------; Author:Robotechnics Laboratories/Vasilios Theodorou ; Project name:DAC utilizing ADC ; Last modification date: 14/5/2002 ;-------------------------------------------------------------.include "c:\microcon\avrtools\appnotes\8535def.inc" ;-------------------------------------------------------------.def .def .def .equ .cseg .org .org 0x00 rjmp ADCCaddr rjmp start: ldi out ldi out ldi out ldi out temp,low(RAMEND) SPL,temp temp,high(RAMEND) SPH,temp temp,0 porta,temp temp,0b00000000 ddra,temp ;Porta as input ADC_INT ;Initialize Stack Pointer start temp temp1 temp2 DAC_val =r16 =r17 =r18 =750

;--------------------------------------------------------------

;--------------------------------------------------------------

;ADC initialization ldi out ldi out temp,0b00000001 ADMUX,temp temp,0b10101000 ADCSR,temp

www.AVRfreaks.net

Design Note #033 Date: 06/02

sei sbi ADCSR,ADSC

; Global interrupt enable

main: rjmp main ;-------------------------------------------------------------;ADC complete interrupt service routine ADC_INT: in in subi sbci brpl temp1,ADCL temp2,ADCH temp1,low(DAC_val) temp2,high(DAC_val) ad_lo

sbi rjmp ad_lo: cbi ad_end: reti

PORTA,0 ad_end

PORTA,0

;-------------------------------

Design Note #033 Date: 06/02

www.AVRfreaks.net

Anda mungkin juga menyukai

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 1Penilaian: 2.5 dari 5 bintang2.5/5 (3)

- Linear IC Applications: A Designer's HandbookDari EverandLinear IC Applications: A Designer's HandbookPenilaian: 4 dari 5 bintang4/5 (1)

- MT-019 Tutorial: DAC Interface FundamentalsDokumen14 halamanMT-019 Tutorial: DAC Interface FundamentalsEric KerrBelum ada peringkat

- Experiment No. 4 ADC PDFDokumen16 halamanExperiment No. 4 ADC PDFRia Cordova0% (1)

- Applications of 8085 Microprocessor Dac InterfaceDokumen4 halamanApplications of 8085 Microprocessor Dac InterfaceSai PrakashBelum ada peringkat

- Unipolar To Bipolar Analog Voltage ConversionDokumen20 halamanUnipolar To Bipolar Analog Voltage ConversionGautam MonipatroBelum ada peringkat

- DLC LAB - 10 - Student - ManualDokumen8 halamanDLC LAB - 10 - Student - ManualImtiaj SajinBelum ada peringkat

- DLC Lab - 10Dokumen7 halamanDLC Lab - 10Didarul Alam AlifBelum ada peringkat

- ADC Interfacing With MicrocontrollersDokumen9 halamanADC Interfacing With MicrocontrollersLuis MezaBelum ada peringkat

- Lesson Adc PWMDokumen36 halamanLesson Adc PWMDavidRubeomBelum ada peringkat

- Introduction To Analog To Digital Converters (ADC)Dokumen9 halamanIntroduction To Analog To Digital Converters (ADC)diether.gozumBelum ada peringkat

- Using DE0-Nano ADC-1Dokumen17 halamanUsing DE0-Nano ADC-1Sylwester MBelum ada peringkat

- Adc 0804Dokumen5 halamanAdc 0804gouttBelum ada peringkat

- DEC LAB 06 (Design of A Digital To Analog Converter)Dokumen9 halamanDEC LAB 06 (Design of A Digital To Analog Converter)anon_776365175Belum ada peringkat

- Precision DAC - AC SpecsDokumen17 halamanPrecision DAC - AC SpecsAvinash BadanikaiBelum ada peringkat

- ADC TutorialDokumen17 halamanADC TutorialNagabhushanam KoduriBelum ada peringkat

- Applying The New CMOS Micro-Dac: National Semiconductor Application Note 271 Tim Regan September 1981Dokumen12 halamanApplying The New CMOS Micro-Dac: National Semiconductor Application Note 271 Tim Regan September 1981Beroxi MihaiBelum ada peringkat

- Adc - DacDokumen4 halamanAdc - DacShaheer TariqBelum ada peringkat

- Virtex Analog To Digital Converter: Application NoteDokumen8 halamanVirtex Analog To Digital Converter: Application NoteTulasi RadhikaBelum ada peringkat

- FINAL Documentation For EmbdedDokumen11 halamanFINAL Documentation For EmbdedakashkirtyBelum ada peringkat

- Noninverting Circuit For High-To-Low Voltage Level Translation Very ImportantDokumen7 halamanNoninverting Circuit For High-To-Low Voltage Level Translation Very Importantsung quekBelum ada peringkat

- Dec Exp 6 Student ManualDokumen5 halamanDec Exp 6 Student ManualSakib MahmudBelum ada peringkat

- Digital To Analog Converters NotesDokumen12 halamanDigital To Analog Converters Noteszoluska xyzBelum ada peringkat

- 8 A-D ConverterDokumen30 halaman8 A-D Converterneoloader145Belum ada peringkat

- Using ADC (Analog To Digital Converter) of AVR MicrocontrollerDokumen6 halamanUsing ADC (Analog To Digital Converter) of AVR MicrocontrollerfreeBelum ada peringkat

- BI Technologies R2R Resistor Ladder NetworksDokumen6 halamanBI Technologies R2R Resistor Ladder NetworksChethan JayasimhaBelum ada peringkat

- 10-Analog To Digital ConverterDokumen41 halaman10-Analog To Digital ConverterSamuel ChristianBelum ada peringkat

- Interfacing With Data Converters and Steeper MotorDokumen28 halamanInterfacing With Data Converters and Steeper Motorsatyanarayana12Belum ada peringkat

- (Model No:VBMB - 002) : 8-Bit Digital To Analog Converter Interface BoardDokumen56 halaman(Model No:VBMB - 002) : 8-Bit Digital To Analog Converter Interface BoardSanthanu Surendran100% (1)

- DAC80508ZRTET A Pin-Compatible Buffered-Voltage-Output Digital-To-Analog ConverterDokumen5 halamanDAC80508ZRTET A Pin-Compatible Buffered-Voltage-Output Digital-To-Analog ConverterjackBelum ada peringkat

- Design and Simulation of DAC On The Basis of Capacitor ArrayDokumen4 halamanDesign and Simulation of DAC On The Basis of Capacitor ArrayAmitBelum ada peringkat

- Digital System Design I DACDokumen9 halamanDigital System Design I DACعبد الحكم زهيرBelum ada peringkat

- Multiplying Dacs: Flexible Building BlocksDokumen8 halamanMultiplying Dacs: Flexible Building BlocksLucas McCauleyBelum ada peringkat

- Analog To Digital (ADC) and Digital To Analog (DAC) ConvertersDokumen12 halamanAnalog To Digital (ADC) and Digital To Analog (DAC) ConvertersIoana IoanaBelum ada peringkat

- Design of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTADokumen22 halamanDesign of A Pipelined 8b 10MSPS Analog To Digital Converter From System To OTAZarion JacobsBelum ada peringkat

- Sboa 558Dokumen10 halamanSboa 558Can IlicaBelum ada peringkat

- ADC On A PICDokumen4 halamanADC On A PICDurgesh Kumar Singh100% (1)

- Digital-to-Analog Analog-to-Digital Conversions: Microprocessor InterfaceDokumen34 halamanDigital-to-Analog Analog-to-Digital Conversions: Microprocessor Interfaceeugen lupuBelum ada peringkat

- 5.AD and DA ConvertersDokumen7 halaman5.AD and DA ConvertersAkram TahaBelum ada peringkat

- ADC Measurement DetailDokumen9 halamanADC Measurement DetailMuhammad SiddiqueBelum ada peringkat

- Adc Dac InterfacingDokumen25 halamanAdc Dac InterfacingSuchetha SriBelum ada peringkat

- Applications of Handshake ModeDokumen3 halamanApplications of Handshake Modevyshnu3006Belum ada peringkat

- MAX5072/3 Switching Power Supply Clock ConfigurationDokumen13 halamanMAX5072/3 Switching Power Supply Clock ConfigurationJc Jayamanikandan BBelum ada peringkat

- APSP - Lecture Notes 2Dokumen7 halamanAPSP - Lecture Notes 2Manjula sBelum ada peringkat

- Boost Converter Using The PIC16F753 Analog Features: Performance SpecificationsDokumen9 halamanBoost Converter Using The PIC16F753 Analog Features: Performance SpecificationsSheik Ashiq AmeerBelum ada peringkat

- Ad5308 5318 5328 PDFDokumen28 halamanAd5308 5318 5328 PDFAndres Fernandez FernandezBelum ada peringkat

- DiDokumen10 halamanDipakojidastavimBelum ada peringkat

- How Do Adcs Work?: Back PrintDokumen5 halamanHow Do Adcs Work?: Back Printmilostar6Belum ada peringkat

- AD7998BRU-0 S Small-Footprint TSSOP FPGA DesignDokumen5 halamanAD7998BRU-0 S Small-Footprint TSSOP FPGA DesignjackBelum ada peringkat

- Interfacing To The Parallel PortDokumen2 halamanInterfacing To The Parallel Portdavid reyesBelum ada peringkat

- Flyback Converter Design ThesisDokumen8 halamanFlyback Converter Design Thesisleanneuhlsterlingheights100% (2)

- Adc Dac Converter NewDokumen50 halamanAdc Dac Converter NewJaya PaulBelum ada peringkat

- AVR Hardware Design ConsiderationsDokumen14 halamanAVR Hardware Design ConsiderationsAmarnath M Damodaran100% (1)

- DAC&ADC (EngineeringDuniya - Com)Dokumen24 halamanDAC&ADC (EngineeringDuniya - Com)ramanaidu10% (1)

- El Amraouiyine ImadDokumen22 halamanEl Amraouiyine ImadImad EL AmraouiyineBelum ada peringkat

- Intel Processor Power Delivery DesignDokumen13 halamanIntel Processor Power Delivery DesignE.I.OSEBelum ada peringkat

- Signal Limiter For Power Amplifiers: (Formerly Application Note 103)Dokumen9 halamanSignal Limiter For Power Amplifiers: (Formerly Application Note 103)SaverioCorBelum ada peringkat

- 16-Bit, Quad Channel, Ultra-Low Glitch, Voltage Output Digital-to-Analog Converter With 2.5V, 2ppm/ C Internal ReferenceDokumen50 halaman16-Bit, Quad Channel, Ultra-Low Glitch, Voltage Output Digital-to-Analog Converter With 2.5V, 2ppm/ C Internal ReferenceCarlos Garduño RBelum ada peringkat

- Digital-to-Analog Analog-to-Digital: Interface Part IV MicroprocessorDokumen30 halamanDigital-to-Analog Analog-to-Digital: Interface Part IV MicroprocessorVineeth KumarBelum ada peringkat

- Reference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Dari EverandReference Guide To Useful Electronic Circuits And Circuit Design Techniques - Part 2Belum ada peringkat

- Efficient C Coding For AVRDokumen15 halamanEfficient C Coding For AVRapi-3740925Belum ada peringkat

- Examples of Programming in MatlabDokumen12 halamanExamples of Programming in Matlabmilad100% (1)

- Running Labview in MatlabDokumen5 halamanRunning Labview in MatlabelfrichBelum ada peringkat

- MATLAB Symbolic Math ToolboxDokumen300 halamanMATLAB Symbolic Math ToolboxelfrichBelum ada peringkat

- Matlab Training - Basic Control TheoryDokumen10 halamanMatlab Training - Basic Control TheoryhamedBelum ada peringkat

- (2001) Ebook - Electronics and Circuit Analysis Using Matlab - Theory - DiodesDokumen41 halaman(2001) Ebook - Electronics and Circuit Analysis Using Matlab - Theory - DiodeselfrichBelum ada peringkat

- Chemical Process Control A First Course With Matlab - P.C. Chau PDFDokumen255 halamanChemical Process Control A First Course With Matlab - P.C. Chau PDFAli NassarBelum ada peringkat

- Mathematics - Fourier Transforms Using MATLABDokumen16 halamanMathematics - Fourier Transforms Using MATLABapi-3833675100% (2)

- Shallow Liquid Simulation Using Matlab (2001 Neumann)Dokumen34 halamanShallow Liquid Simulation Using Matlab (2001 Neumann)Sofia ManuelBelum ada peringkat

- GyroscopeDokumen7 halamanGyroscopeRajesh SarkarBelum ada peringkat

- AVR Boot LoaderDokumen7 halamanAVR Boot LoaderelfrichBelum ada peringkat

- Ebook - Atmel Avr AssemblerDokumen20 halamanEbook - Atmel Avr AssemblerelfrichBelum ada peringkat

- The Complete Smith Chart: Black Magic DesignDokumen1 halamanThe Complete Smith Chart: Black Magic DesignelfrichBelum ada peringkat

- Winavr Avr GCCDokumen40 halamanWinavr Avr GCCelfrichBelum ada peringkat

- Creating Non-Blocking Timers in AVRDokumen4 halamanCreating Non-Blocking Timers in AVRelfrichBelum ada peringkat

- Intefacing Avr Keyboard Doc2532Dokumen11 halamanIntefacing Avr Keyboard Doc2532Andy MarioBelum ada peringkat

- Avr Libc User Manual 1.4.4Dokumen270 halamanAvr Libc User Manual 1.4.4m_a_h_rBelum ada peringkat

- Stepper Motor ControllerDokumen3 halamanStepper Motor Controllerelfrich100% (3)

- SCT Steppers HY200Dokumen16 halamanSCT Steppers HY200guanteBelum ada peringkat

- Ic697pwr710 - Power Supply Module 55W PDFDokumen7 halamanIc697pwr710 - Power Supply Module 55W PDFchaparalBelum ada peringkat

- Diodo 1N47XXDokumen3 halamanDiodo 1N47XXDaniel ReyBelum ada peringkat

- Yashica FlashDokumen17 halamanYashica FlashEnrique RichardBelum ada peringkat

- ShimDLL - 2020 09 12 - 19 02 10 - 0718Dokumen52 halamanShimDLL - 2020 09 12 - 19 02 10 - 0718Анатолий РябоконьBelum ada peringkat

- C264 Enhw C30Dokumen46 halamanC264 Enhw C30Dang JinlongBelum ada peringkat

- Em-Hse-F028 Rev.0 Monthly Inspection of Full Body Harness and LanyardDokumen7 halamanEm-Hse-F028 Rev.0 Monthly Inspection of Full Body Harness and Lanyardsitaram75Belum ada peringkat

- Bootable Usb Windows 10Dokumen3 halamanBootable Usb Windows 10Rajan BabuBelum ada peringkat

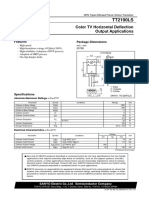

- TT2190LS: Color TV Horizontal Deflection Output ApplicationsDokumen4 halamanTT2190LS: Color TV Horizontal Deflection Output ApplicationsFreddyBelum ada peringkat

- Mdb-02 VD Calculation - 30042019Dokumen31 halamanMdb-02 VD Calculation - 30042019shrikanth5singhBelum ada peringkat

- VCS Commands TutorialDokumen41 halamanVCS Commands TutorialGanji AmarendharBelum ada peringkat

- Berklee Music Production Handbook PDFDokumen15 halamanBerklee Music Production Handbook PDFDebbie Wong100% (2)

- Dokumen - Tips Ready Admit Card Cooch Behar Without Admit Card Will Not Be Allowed For WrittenDokumen410 halamanDokumen - Tips Ready Admit Card Cooch Behar Without Admit Card Will Not Be Allowed For WrittenCavya DealsBelum ada peringkat

- Pick-Up Current, Plug Setting Multiplier (PSM) and Time Setting Multiplier (TSM) - Electrical ConceptsDokumen7 halamanPick-Up Current, Plug Setting Multiplier (PSM) and Time Setting Multiplier (TSM) - Electrical ConceptsrazakhanBelum ada peringkat

- Phase Relay Control RM17TG SchneiderDokumen2 halamanPhase Relay Control RM17TG SchneiderSevtunus BangunBelum ada peringkat

- Sony CDX-G3100UE, G3100UV, G3150UP, G3150UV PDFDokumen38 halamanSony CDX-G3100UE, G3100UV, G3150UP, G3150UV PDFboroda2410Belum ada peringkat

- Lab Manual of Computer GraphicsDokumen4 halamanLab Manual of Computer GraphicsniksritikBelum ada peringkat

- OSN 8800 6800 3800 V100 Routine Maintenance 06Dokumen26 halamanOSN 8800 6800 3800 V100 Routine Maintenance 06terenteBelum ada peringkat

- 16 Electrical General:: Item Unit Cost Total Cost No. S.R S.R Remarks Div. Description of Material Unit QuantityDokumen4 halaman16 Electrical General:: Item Unit Cost Total Cost No. S.R S.R Remarks Div. Description of Material Unit QuantityjatinBelum ada peringkat

- PHY547 - LAb Manual-2019Dokumen26 halamanPHY547 - LAb Manual-2019zulhaimirasheedBelum ada peringkat

- 2953 Vol-4 PDFDokumen271 halaman2953 Vol-4 PDFAbhayKumarBelum ada peringkat

- MKT053 Fa22-2300 MadrasDokumen2 halamanMKT053 Fa22-2300 MadrasrawassatBelum ada peringkat

- Usage: Universal Programmable Poe Injector (P/N I0Atpi24)Dokumen4 halamanUsage: Universal Programmable Poe Injector (P/N I0Atpi24)jimpomaBelum ada peringkat

- Trimble Gps in STDokumen65 halamanTrimble Gps in STMohamedAlAmineBelum ada peringkat

- Io TDokumen19 halamanIo TAchmad Fahrul Aji100% (2)

- AO4466 N-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionDokumen4 halamanAO4466 N-Channel Enhancement Mode Field Effect Transistor: Features General DescriptionErick V. BlancoBelum ada peringkat

- Classification of Incandescent BulbDokumen31 halamanClassification of Incandescent BulbLorica John LuisBelum ada peringkat

- Chem331 2015 StudentNotes BDokumen32 halamanChem331 2015 StudentNotes BVikram VickyBelum ada peringkat

- ZTE UMTS UR15 License Management SolutionDokumen23 halamanZTE UMTS UR15 License Management Solutionmickyalemu100% (1)

- QuesDokumen3 halamanQuesAkhilesh ChaudhryBelum ada peringkat

- Publison InfernalDokumen2 halamanPublison InfernalShane SandersBelum ada peringkat