RR210204 Switching Theory & Logic Design

Diunggah oleh

sivabharathamurthyDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

RR210204 Switching Theory & Logic Design

Diunggah oleh

sivabharathamurthyHak Cipta:

Format Tersedia

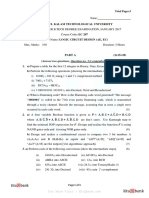

Code No.

: RR 210204

RR

II B.Tech I Semester (RR) Supplementary Examinations, November 2011

SWITCHING THEORY AND LOGIC DESIGN

(Common to Electrical & Electronics Engineering, Electronics Communication Engineering, Computer Science & Engineering, Electronics & Instrumentation Engineering, Information Technology, Electronics & Control Engineering, Electronics & Computer Engineering, Computer Science & Systems Engineering and Biomedical Engineering)

Time: 3 hours Answer any FIVE Questions All Questions carry equal marks

Max Marks: 80

1. (a) Write the following binary numbers in signed 1s complement form and signed 2s complement form using 16 bit registers. i. ii. iii. iv. +1001010 -11110000 -11001100.1 +100000011.111

(b) Perform N1+N2,N1+(-N2) for the following 8 bit numbers expressed in a 2s complement representation. Verify your answers by using decimal addition and subtraction i. N1=00110010, N2=11111101 ii. N1=10001110, N2=00001101 [10+6] 2. (a) Simplify the function using Karnaugh map method F (A,B,C,D) = (4,5,7,12,14,15)+ d(3,8,10). (b) Give three possible ways to express the function F = A B D + A B C D + ABD + ABCD with eight or less literals. 3. Implement the function F with the following two level forms (a) NAND-AND, (b) AND-NOR, (c) OR-NAND and (d) NOR-OR F (A, B, C, D) = (0,1,2,3,4,8,9,12) [16] 4. (a) Show how a 16-to-1 mux can be realized using 4-to-1 muxes. (b) Implement the function f(a,b,c)= a.b + using the 4-to-1 mux. b.c [8+8] 1 of 2 [8+8]

Code No. : RR 210204

RR

5. (a) Draw the circuit diagram of J-K ip op with NAND gates with positive edge triggering and explain its operation with the help of truth table. How race around condition is eliminated. (b) Realize D-latch using R-S latch. How it is dierent from D-ip op. Draw the circuit using NAND gates and explain. [8+8] 6. A sequential circuit has three D ip-ops, A, B, C and one input x.. It is described by the following ip-ops input functions DA = (BC 1 + B 1 C)x + (BC + B 1 C 1 )x1 DB=A DC=B (a) Derive the state stable for the circuit. (b) Draw two state diagrams one for x=0, and the other for x=1. [16] 7. What are the conditions for the two machines are to be equivalent? For the machine given below, nd the equivalence partition and a corresponding reduced machine in standard form: PS A B C D E F G NS,Z X=0 X=1 F,0 B,1 G,0 A,1 B,0 C,1 C,0 B,1 D,0 A,1 E,1 F,1 E,1 G,1 [16] 8. (a) Draw the state diagram and the state table of the control unit conditions given below. Draw the equivalent ASM chart leaving the state box empty. i. from 00 state, if x = 1 , it goes to 01 state and if x = 0, it remains in the same state 00. ii. from 01 state, if y = 1, it goes to 11 state and if y = 0, it goes to 10 state. iii. from 10 stae, if x = 1 and y = 0, it remains in the same state 10 and if x = 1 and y = 1, it goes to 11 state, and if x = 0, it goes to 00 state. iv. from 11 state, if x = 1, y = 0, it goes to 10 state and if x = 1, and y = 1, it remains in the same state, and if x = 0, it goes to 00 state. (b) Design the control using PLA and register.for the above problem. [8+8]

Anda mungkin juga menyukai

- Rr210203 Switching Theory and Logic DesignDokumen8 halamanRr210203 Switching Theory and Logic DesignSrinivasa Rao G100% (2)

- Rr210203 Switching Theory and Logic DesignDokumen9 halamanRr210203 Switching Theory and Logic DesignSrinivasa Rao GBelum ada peringkat

- 21 - 2010 - Nov - R09 - STLDDokumen8 halaman21 - 2010 - Nov - R09 - STLDvasuvlsiBelum ada peringkat

- Answer Two Questions, Question No. 3 Is CompulsoryDokumen3 halamanAnswer Two Questions, Question No. 3 Is CompulsoryABHILESH G KBelum ada peringkat

- Instructions To StudentsDokumen9 halamanInstructions To StudentsOmar Magdy AbdelbakyBelum ada peringkat

- Practice Problems - 1: Department of Electrical EngineeringDokumen2 halamanPractice Problems - 1: Department of Electrical EngineeringMalay Kumar MohantaBelum ada peringkat

- STLD Question BankDokumen6 halamanSTLD Question Bankrachasaikiran0% (1)

- Nov 2019Dokumen6 halamanNov 2019ponniBelum ada peringkat

- Switching Theory and Logic DesignDokumen8 halamanSwitching Theory and Logic DesignSubrahmanyam VjsBelum ada peringkat

- 21 - 2011 - Dec - R09 - STLDDokumen8 halaman21 - 2011 - Dec - R09 - STLDvasuvlsiBelum ada peringkat

- 9A04306 Digital Logic DesignDokumen4 halaman9A04306 Digital Logic DesignsivabharathamurthyBelum ada peringkat

- Logic AssignmentDokumen4 halamanLogic AssignmentYeshiwas KefaleBelum ada peringkat

- Homework 1 (DLC)Dokumen3 halamanHomework 1 (DLC)Aamir KhanBelum ada peringkat

- Digital Logic DesignDokumen4 halamanDigital Logic DesignShareef KhanBelum ada peringkat

- 9A04401 Switching Theory & Logic DesignDokumen4 halaman9A04401 Switching Theory & Logic DesignsivabharathamurthyBelum ada peringkat

- STLD Regular Jntu Question Papers 2008Dokumen9 halamanSTLD Regular Jntu Question Papers 2008anjaneyulud100% (1)

- UNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Dokumen18 halamanUNIT WISE QUEST DIGITAL LOGIC DESIGN - GIET 2019 II - I (3rd Sem)Deepak NaiduBelum ada peringkat

- Assingnment# 1Dokumen8 halamanAssingnment# 1Tayyab AbbasBelum ada peringkat

- EE8351 Iq 16 Marks PDFDokumen7 halamanEE8351 Iq 16 Marks PDFdeepika senthilBelum ada peringkat

- 9A04401 Switching Theory & Logic DesignDokumen4 halaman9A04401 Switching Theory & Logic DesignsivabharathamurthyBelum ada peringkat

- R7210504 Digital Logic DesignDokumen2 halamanR7210504 Digital Logic DesignsivabharathamurthyBelum ada peringkat

- r05220403 Switching Theory and Logic DesignDokumen8 halamanr05220403 Switching Theory and Logic DesignSRINIVASA RAO GANTABelum ada peringkat

- DLD Da1Dokumen38 halamanDLD Da1Navin Rs0% (1)

- 9A04306 Digital Logic DesignDokumen4 halaman9A04306 Digital Logic DesignsivabharathamurthyBelum ada peringkat

- Rajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterDokumen37 halamanRajagiri School of Engineering and Technology: Rajagiri Valley, Kakkanad. Third SemesterAmrita VenkitaramaniBelum ada peringkat

- Fundamentals of Digital System DesignDokumen2 halamanFundamentals of Digital System DesignsubramanianBelum ada peringkat

- STLD 2009 RegularDokumen4 halamanSTLD 2009 RegularrangerBelum ada peringkat

- Assignment (EEE 323) For 2017-18 BatchDokumen2 halamanAssignment (EEE 323) For 2017-18 BatchMaruf MorshedBelum ada peringkat

- Digital 16 Marks.Dokumen4 halamanDigital 16 Marks.Saranya PrabhuBelum ada peringkat

- 9a04306-Digital Logic DesignDokumen1 halaman9a04306-Digital Logic DesignSheikh Noor MohammadBelum ada peringkat

- Epc Questions - Cs8351 Digital Principles and System DesignDokumen2 halamanEpc Questions - Cs8351 Digital Principles and System DesignaltaBelum ada peringkat

- Sir Syed University of Engineering & Technlogy, Karachi LDST Final 2012Dokumen2 halamanSir Syed University of Engineering & Technlogy, Karachi LDST Final 2012Faisal Yazdanie0% (1)

- Question Paper Code:: Y Abcababc + + +Dokumen3 halamanQuestion Paper Code:: Y Abcababc + + +karthick VijayanBelum ada peringkat

- Important 16 Mark Questions-19!1!2024Dokumen5 halamanImportant 16 Mark Questions-19!1!2024FLOWERBelum ada peringkat

- Digital Circuit Design-ECE 2026 Digital AssignmentDokumen1 halamanDigital Circuit Design-ECE 2026 Digital AssignmentDesta Yakob Doda 18BML0121Belum ada peringkat

- Digital Paper1Dokumen5 halamanDigital Paper1Iyyakutti GanapathiBelum ada peringkat

- DigitalDokumen2 halamanDigitalVikrant SahuBelum ada peringkat

- KEE401 ASSIGNMENTS and QUESTION BANKDokumen17 halamanKEE401 ASSIGNMENTS and QUESTION BANKPrince VermaBelum ada peringkat

- Digital Q BankDokumen17 halamanDigital Q BankMuhamad FaizalBelum ada peringkat

- Logic Design Jan 2010 ESDokumen2 halamanLogic Design Jan 2010 ESPrasad C MBelum ada peringkat

- 113BU032016Dokumen2 halaman113BU032016mushahedBelum ada peringkat

- Emergency Digital ExerciseDokumen2 halamanEmergency Digital ExerciseAmy DavenportBelum ada peringkat

- Question Bank M Tech 2ND Sem Batch 2018Dokumen31 halamanQuestion Bank M Tech 2ND Sem Batch 2018king khanBelum ada peringkat

- BMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsDokumen3 halamanBMS College of Engineering, Bangalore-560019: December 2015 Semester End Main ExaminationsrameshBelum ada peringkat

- 07a4ec09 STLDDokumen6 halaman07a4ec09 STLDSRINIVASA RAO GANTABelum ada peringkat

- R13 Nov 2016Dokumen2 halamanR13 Nov 2016Anil Kumar BBelum ada peringkat

- Digital System Design QuestionsDokumen5 halamanDigital System Design Questionsvijay4u4allBelum ada peringkat

- Final Exam SampleDokumen4 halamanFinal Exam Samplemaithuong85Belum ada peringkat

- 15A04306 Digital Logic Design4Dokumen2 halaman15A04306 Digital Logic Design4Lakshmi PrashanthBelum ada peringkat

- DCD DaDokumen28 halamanDCD Dakathi50% (2)

- S T L DDokumen12 halamanS T L DMohan Krishna0% (1)

- DD Co QuestionsDokumen8 halamanDD Co QuestionsRohit M ABelum ada peringkat

- Obtain The 9's and 10's Complement ofDokumen3 halamanObtain The 9's and 10's Complement ofNandha Kizor VBelum ada peringkat

- Digital Electronics 2: Sequential and Arithmetic Logic CircuitsDari EverandDigital Electronics 2: Sequential and Arithmetic Logic CircuitsPenilaian: 5 dari 5 bintang5/5 (1)

- Tables of Racah Coefficients: Mathematical Tables SeriesDari EverandTables of Racah Coefficients: Mathematical Tables SeriesBelum ada peringkat

- Computer Vision in Vehicle Technology: Land, Sea, and AirDari EverandComputer Vision in Vehicle Technology: Land, Sea, and AirBelum ada peringkat

- R7410407 Operating SystemsDokumen1 halamanR7410407 Operating SystemssivabharathamurthyBelum ada peringkat

- Control Systems (CS) Notes As Per JntuaDokumen203 halamanControl Systems (CS) Notes As Per Jntuasivabharathamurthy100% (3)

- 07A4EC01 Environmental StudiesDokumen1 halaman07A4EC01 Environmental StudiessivabharathamurthyBelum ada peringkat

- SSC Social Textbook (AP)Dokumen100 halamanSSC Social Textbook (AP)sivabharathamurthyBelum ada peringkat

- R7410506 Mobile ComputingDokumen1 halamanR7410506 Mobile ComputingsivabharathamurthyBelum ada peringkat

- SSC Telugu (FL) (AP)Dokumen232 halamanSSC Telugu (FL) (AP)sivabharathamurthyBelum ada peringkat

- R7311205 Distributed DatabasesDokumen1 halamanR7311205 Distributed DatabasessivabharathamurthyBelum ada peringkat

- 9A05707 Software Project ManagementDokumen4 halaman9A05707 Software Project ManagementsivabharathamurthyBelum ada peringkat

- R5410201 Neural Networks & Fuzzy LogicDokumen1 halamanR5410201 Neural Networks & Fuzzy LogicsivabharathamurthyBelum ada peringkat

- R7311506 Operating SystemsDokumen1 halamanR7311506 Operating SystemssivabharathamurthyBelum ada peringkat

- R7312301 Transport Phenomena in BioprocessesDokumen1 halamanR7312301 Transport Phenomena in BioprocessessivabharathamurthyBelum ada peringkat

- 9A14503 Principles of Machine DesignDokumen8 halaman9A14503 Principles of Machine DesignsivabharathamurthyBelum ada peringkat

- 9A13701 Robotics and AutomationDokumen4 halaman9A13701 Robotics and AutomationsivabharathamurthyBelum ada peringkat

- Code: R7311306: (Electronics & Control Engineering)Dokumen1 halamanCode: R7311306: (Electronics & Control Engineering)sivabharathamurthyBelum ada peringkat

- R5310204 Power ElectronicsDokumen1 halamanR5310204 Power ElectronicssivabharathamurthyBelum ada peringkat

- R7310506 Design & Analysis of AlgorithmsDokumen1 halamanR7310506 Design & Analysis of AlgorithmssivabharathamurthyBelum ada peringkat

- R7311006 Process Control InstrumentationDokumen1 halamanR7311006 Process Control InstrumentationsivabharathamurthyBelum ada peringkat

- R7310106 Engineering GeologyDokumen1 halamanR7310106 Engineering GeologysivabharathamurthyBelum ada peringkat

- R7310206 Linear Systems AnalysisDokumen1 halamanR7310206 Linear Systems AnalysissivabharathamurthyBelum ada peringkat

- R7310306 Heat TransferDokumen1 halamanR7310306 Heat Transfersivabharathamurthy100% (1)

- 9A23501 Heat Transfer in BioprocessesDokumen4 halaman9A23501 Heat Transfer in BioprocessessivabharathamurthyBelum ada peringkat

- 9A21506 Mechanisms & Mechanical DesignDokumen8 halaman9A21506 Mechanisms & Mechanical DesignsivabharathamurthyBelum ada peringkat

- 9A15502 Digital System DesignDokumen4 halaman9A15502 Digital System Designsivabharathamurthy100% (1)

- R7310406 Digital CommunicationsDokumen1 halamanR7310406 Digital CommunicationssivabharathamurthyBelum ada peringkat

- R5310406 Digital CommunicationsDokumen1 halamanR5310406 Digital CommunicationssivabharathamurthyBelum ada peringkat

- 9A05505 Operating SystemsDokumen4 halaman9A05505 Operating SystemssivabharathamurthyBelum ada peringkat

- 9A10505 Principles of CommunicationsDokumen4 halaman9A10505 Principles of CommunicationssivabharathamurthyBelum ada peringkat

- 9A02505 Electrical Machines-IIIDokumen4 halaman9A02505 Electrical Machines-IIIsivabharathamurthyBelum ada peringkat

- 9A04504 Digital IC ApplicationsDokumen4 halaman9A04504 Digital IC ApplicationssivabharathamurthyBelum ada peringkat

- 9A03505 Heat TransferDokumen4 halaman9A03505 Heat TransfersivabharathamurthyBelum ada peringkat

- Types of CCTVDokumen12 halamanTypes of CCTVpradeeplava950Belum ada peringkat

- Harden's Spices Model For Biochemistry in Medical CurriculumDokumen10 halamanHarden's Spices Model For Biochemistry in Medical CurriculumGlobal Research and Development Services100% (1)

- KPODokumen18 halamanKPOjohnrichardjasmineBelum ada peringkat

- Chapter 1 AnswersDokumen3 halamanChapter 1 Answersdeerhntr22Belum ada peringkat

- COOLANT Komatsu PDFDokumen16 halamanCOOLANT Komatsu PDFdarwin100% (1)

- TA - 031 - en General Information For Diaphragm SealsDokumen5 halamanTA - 031 - en General Information For Diaphragm Sealstudonghoa tmpBelum ada peringkat

- Lab 11&12Dokumen9 halamanLab 11&12Divyashini MohanBelum ada peringkat

- FORCE CatalogueDokumen85 halamanFORCE CatalogueMaterialsOne100% (1)

- Performance of Gesture Controlled DroneDokumen11 halamanPerformance of Gesture Controlled DroneKrishna SivaBelum ada peringkat

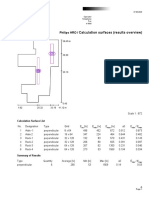

- Calculation Surfaces (Results Overview) : Philips HRODokumen4 halamanCalculation Surfaces (Results Overview) : Philips HROsanaBelum ada peringkat

- Cscope Maps - VimDokumen3 halamanCscope Maps - VimGaurav SharmaBelum ada peringkat

- Maintenance and Repair Instructions TM 124/11: Spring-Applied Sliding Caliper Brake FSG110 With Hub CenteringDokumen11 halamanMaintenance and Repair Instructions TM 124/11: Spring-Applied Sliding Caliper Brake FSG110 With Hub CenteringNik100% (1)

- Composition Code ExampleDokumen3 halamanComposition Code ExampleREBEL USMANBelum ada peringkat

- A01 04 Assessmentk UndercarriageDokumen7 halamanA01 04 Assessmentk UndercarriageMARIO DEL PINO MUÑOZBelum ada peringkat

- TM - A5ck, CC, CM - y PDFDokumen102 halamanTM - A5ck, CC, CM - y PDFslipargolokBelum ada peringkat

- Pre Joining Formalities Campus Medical FormDokumen18 halamanPre Joining Formalities Campus Medical Formrafii_babu1988Belum ada peringkat

- Changing Out The Injector Seals On A 2007 PJ Ford Ranger 3.0 TDCiDokumen3 halamanChanging Out The Injector Seals On A 2007 PJ Ford Ranger 3.0 TDCiAgustinus D100% (3)

- TM 9-792 M21 AMMUNITION TRAILERDokumen128 halamanTM 9-792 M21 AMMUNITION TRAILERAdvocate100% (1)

- Est-Pergola Octogonal 21-03-2022Dokumen1 halamanEst-Pergola Octogonal 21-03-2022Victor MuñozBelum ada peringkat

- Catalog07 PDFDokumen13 halamanCatalog07 PDFdeig15050% (2)

- Acetic 2520acid 2520 Energy 2520balanceDokumen6 halamanAcetic 2520acid 2520 Energy 2520balancembeni0751Belum ada peringkat

- 29-Horizontal Subsea Xmas Tree enDokumen2 halaman29-Horizontal Subsea Xmas Tree encarthik_rajaBelum ada peringkat

- B. Tech. Electrical and Electronics EngineeringDokumen105 halamanB. Tech. Electrical and Electronics EngineeringKarthik NagarajanBelum ada peringkat

- Electrical Power Systems Wadhwa 15Dokumen1 halamanElectrical Power Systems Wadhwa 15ragupaBelum ada peringkat

- Account Statement: Karthikeyan S 47asumugaflats, Kamarajarstreet Oragadam Ambattur, Ambattur ChennaiDokumen2 halamanAccount Statement: Karthikeyan S 47asumugaflats, Kamarajarstreet Oragadam Ambattur, Ambattur ChennaiKarthikeyan MallikaBelum ada peringkat

- Growth of Escherichia Coli in A 5 Litre Batch Fermentation VesselDokumen15 halamanGrowth of Escherichia Coli in A 5 Litre Batch Fermentation VesselAs'ad Mughal100% (2)

- ABB SWBD VD4 Brochure PDFDokumen6 halamanABB SWBD VD4 Brochure PDFanand_girgaonkarBelum ada peringkat

- Managerial Communication - (MC) - SEM I-GTUDokumen93 halamanManagerial Communication - (MC) - SEM I-GTUkeyurBelum ada peringkat

- Resume Executive Summary ExampleDokumen5 halamanResume Executive Summary ExampleSathish GunasekarBelum ada peringkat

- D20S-7 Sb1159e01 PDFDokumen678 halamanD20S-7 Sb1159e01 PDFGORDBelum ada peringkat