A Sic

Diunggah oleh

mdbelalrshdDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

A Sic

Diunggah oleh

mdbelalrshdHak Cipta:

Format Tersedia

9 Design Flow

Figure 1.10 shows the sequence of steps to design an ASIC; we call this a design flow . The steps are listed below (numbered to correspond to the labels in Figure 1.10) with a brief description of the function of each step.

FIGURE 1.10 ASIC design flow.

1. Design entry. Enter the design into an ASIC design system,

2.

3. 4. 5. 6. 7.

either using a hardware description language ( HDL ) orschematic entry . Logic synthesis. Use an HDL (VHDL or Verilog) and a logic synthesis tool to produce a netlist a description of the logic cells and their connections. System partitioning. Divide a large system into ASIC-sized pieces. Prelayout simulation. Check to see if the design functions correctly. Floorplanning. Arrange the blocks of the netlist on the chip. Placement. Decide the locations of cells in a block. Routing. Make the connections between cells and blocks.

8. Extraction. Determine the resistance and capacitance of the

interconnect. 9. Postlayout simulation. Check to see the design still works with the added loads of the interconnect. Steps 14 are part of logical design , and steps 59 are part of physical design . There is some overlap. For example, system partitioning might be considered as either logical or physical design. To put it another way, when we are performing system partitioning we have to consider both logical and physical factors. Chapters 914 of this book is largely about logical design and Chapters 1517 largely about physical design.

9 Universal Logic : Mux to Logic gates conversion

Posted by Nityanand Dubey on January 7, 2010

We have seen the universal gates in out previous posts. The NAND and NOR are called the universal gates because they can create any of the logic gates. There is an another concept called Universal Logic, Universal logic can also be used to create any of the logic gates. MUX and Decoders are called Universal Logic In this post, we will see haw a 2:1 MUX can be used to create different logic gates. 1. Designing an Inverter using 2:1 MUX. To design an inverter using 2:1 mux, we have to use the input as the select line of the MUX and the zeroth select line would be tied with Logic 1 and First select line would be tired with Logic 0, Now when the select line (Input) goes to 1 the out put will be 0 ( inverted). Image : MUX to inverter -

2:1 mux as an inverter

2. Designing an AND Gate using 2:1 MUX. To design an AND using 2:1 mux, we need to tie the zeroth input to Logic 0 and the First input to the one of the input of the AND Gate. The other input of AND gate would be connected with the select line of the MUX. Now, the out put of the MUX would be 1 only if the both of the inputs are 1 otherwise it would be 0 for all conditions. Image : MUX to AND Gate -

2:1 MUX as an AND gate

3. Designing an OR Gate using 2:1 MUX.

To design an OR using 2:1 mux, we need to tie the First input to Logic 1 and the Zeroth input to the one of the input of the OR Gate. The other input of OR gate would be connected with the select line of the MUX. Now, the output of the MUX would be 1 when any oth the two inputs would be 1 otherwise it would be 0 for all conditions. Image : MUX to OR Gate -

2:1 MUX as an OR Gate

4. Designing an NOR Gate using 2:1 MUX. To design the NOR using 2:1 mux, we need to tie the Zeroth input of mux to one of the input of NOR and another input of MUX is tied to 0 . The another input of NOR gate would be applied to the select line of the MUX. Now, the output of the MUX would be AB = (A+B). which is as same as the output of NOR Gate. Image : MUX to NOR Gate -

2:1 mux as a NOR Gate

5. Designing an NAND Gate using 2:1 MUX. To design the NAND using 2:1 mux, we need to combine the AND Gate and inverter implementation 6. Designing an XOR Gate using 2:1 MUX. To design the XOR using 2:1 mux, we need to tie the Zeroth input of mux to one of the input of XOR and another input of MUX to the inverted of first input. The another input of XOR gate would be applied to the select line of the MUX. Now, the output of the MUX would be AB + AB which is as same as the output of XOR Gate. Image : MUX to XOR Gate -

2:1 Mux as a XOR gate

7. Designing an XNOR Gate using 2:1 MUX. To design the XNOR using 2:1 mux, we need to tie the First input of mux to one of the input of XOR and another input of MUX to the inverted of first input. The another input of XOR gate would be applied to the select line of the MUX. Now, the output of the MUX would be AB + AB which is as same as the output of XNOR Gate. Image : MUX to XNOR Gate -

2:1 mux as a XNOR Gate

ASIC's are usually classified into one of three categories: full-custom, semi-custom, and structured. Full-custom ASIC's are those that are entirely tailor-fitted to a particular application from the very start. Since its ultimate design and functionality is pre-specified by the user, it is manufactured with all the photolithographic layers of the device already fully defined, just like most off-the-shelf general purpose IC's. The use of predefined masks for manufacturing leaves no option for circuit modification during fabrication, except perhaps for some minor finetuning or calibration. This means that a full-custom ASIC can not be modified to suit different applications, and is generally produced as a single, specific product for a particular application only. Semi-custom ASIC's, on the other hand, can be partly customized to serve different functions within its general area of application. Unlike full-custom ASIC's, semi-custom ASIC's are designed to allow a certain degree of modification during the manufacturing process. A semicustom ASIC is manufactured with the masks for the diffused layers already fully defined, so the transistors and other active components of the circuit are already fixed for that semi-custom ASIC design. The customization of the final ASIC product to the intended application is done by varying the masks of the interconnection layers, e.g., the metallization layers. Structured or Platform ASIC's, which belong to a relatively new ASIC classification, are those which have been designed and produced from a tightly defined set of: 1) design methodologies; 2) intellectual properties (IP's); and 3) well-characterized silicon, aimed at shortening the design cycle and minimizing the development costs of the ASIC. A

platform ASIC is built from a group of 'platform slices', with a 'platform slice' being defined as a pre-manufactured device, system, or logic for that platform. Each slice used by the ASIC may be customized by varying its metal layers. The 're-use' of pre-manufactured and pre-characterized platform slices simply means that platform ASIC's are not built from scratch, thereby minimizing design cycle time and costs.

Anda mungkin juga menyukai

- Designing An Inverter Using 2:1 MUXDokumen3 halamanDesigning An Inverter Using 2:1 MUXbrk_318Belum ada peringkat

- C CCC CCC C CC C CDokumen6 halamanC CCC CCC C CC C CMd Rizwan AhmadBelum ada peringkat

- Lab 7Dokumen6 halamanLab 7Minh NamBelum ada peringkat

- Vlsi Design Lab ManualDokumen33 halamanVlsi Design Lab Manualjitu123456789100% (1)

- Jana_22BLC1032.docxDokumen26 halamanJana_22BLC1032.docxjanardhanan1711Belum ada peringkat

- Round-Robin Arbiter Design and Generation: Eung S. Shin, Vincent J. Mooney III and George F. RileyDokumen6 halamanRound-Robin Arbiter Design and Generation: Eung S. Shin, Vincent J. Mooney III and George F. RileyKulbhushan ThakurBelum ada peringkat

- DEL - Experiment-1.3 (Switch)Dokumen4 halamanDEL - Experiment-1.3 (Switch)Dk BossBelum ada peringkat

- Experiment 1.3 Bablu KUMAR (DIGITAL)Dokumen6 halamanExperiment 1.3 Bablu KUMAR (DIGITAL)Bablu RaazBelum ada peringkat

- From Discrete Logic To FpgasDokumen31 halamanFrom Discrete Logic To FpgasObaid Aamir Kiyani100% (1)

- Delayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofDokumen13 halamanDelayed Branch Logic: Texas Instruments TMS320 Is A Blanket Name For A Series ofnomadcindrellaBelum ada peringkat

- Lab 1Dokumen13 halamanLab 1Sopno GhuriBelum ada peringkat

- A3-001-B Cmos Adder Design: Module AssignmentDokumen16 halamanA3-001-B Cmos Adder Design: Module AssignmentNabilah AzizBelum ada peringkat

- Physics ProjectDokumen6 halamanPhysics ProjectAdhithyaBelum ada peringkat

- Design and Layout of Half and Full AdderDokumen7 halamanDesign and Layout of Half and Full Adderunity123d deewBelum ada peringkat

- UNIT-3 Gate Level Design NotesDokumen22 halamanUNIT-3 Gate Level Design NotesPallavi Ch100% (2)

- Dsduv Slides 2Dokumen52 halamanDsduv Slides 2Tarun MovvaBelum ada peringkat

- Design and Simulation of 2:1 Mux Using Multiple Logic GatesDokumen58 halamanDesign and Simulation of 2:1 Mux Using Multiple Logic Gatesdurga manisha100% (1)

- Fpga Programming Using Verilog HDL LanguageDokumen89 halamanFpga Programming Using Verilog HDL LanguageSidhartha Sankar Rout0% (1)

- Efficient Designs of Low Power 32nm XOR-XNOR Gate Using CMOS InvertersDokumen4 halamanEfficient Designs of Low Power 32nm XOR-XNOR Gate Using CMOS InverterserpublicationBelum ada peringkat

- Lab Manual Logic Design 1-2Dokumen23 halamanLab Manual Logic Design 1-2akahBelum ada peringkat

- Vlsi Design Lab ManualDokumen14 halamanVlsi Design Lab ManualAntonio LeonBelum ada peringkat

- CMOS Inverter and Gates Layout in MicrowindDokumen27 halamanCMOS Inverter and Gates Layout in Microwindnagarjun3802Belum ada peringkat

- Deld End Sem 5,6Dokumen6 halamanDeld End Sem 5,6The GK TalksBelum ada peringkat

- Lab4 Sheet AludesignDokumen7 halamanLab4 Sheet AludesignSANJEEV MALLICKBelum ada peringkat

- CMOS Inverter Layout Generation and SimulationDokumen19 halamanCMOS Inverter Layout Generation and SimulationRajesh HarikrishnanBelum ada peringkat

- Ver I Log TutorialDokumen18 halamanVer I Log Tutorialritam yadavBelum ada peringkat

- Layout ExamplesDokumen13 halamanLayout Examplesnazibhd786Belum ada peringkat

- Pap 2Dokumen4 halamanPap 2saravanany5kBelum ada peringkat

- Cse 3 2 Vlsi Unit 4 PDFDokumen44 halamanCse 3 2 Vlsi Unit 4 PDF9966299828100% (1)

- 16-Bit Adder and 3-Bit Comparator DesignDokumen6 halaman16-Bit Adder and 3-Bit Comparator DesignKelvin HuiBelum ada peringkat

- Lab 9 Comb CKT With MUX and DEC Full PackageDokumen4 halamanLab 9 Comb CKT With MUX and DEC Full PackageLoveWorldCanadaBelum ada peringkat

- Digital Logic Fundamentals for ElectronicsDokumen25 halamanDigital Logic Fundamentals for ElectronicsYadana1Belum ada peringkat

- Assignment LAB1Dokumen22 halamanAssignment LAB1midunBelum ada peringkat

- Chapter 6: Digital Components: ObjectivesDokumen17 halamanChapter 6: Digital Components: ObjectivesSteffany RoqueBelum ada peringkat

- DEE6113 - Practical Work5 PDFDokumen7 halamanDEE6113 - Practical Work5 PDFFonzBahariBelum ada peringkat

- 111固態電子實驗 Project PDFDokumen8 halaman111固態電子實驗 Project PDF一二三Belum ada peringkat

- Mijena Khalil AESDokumen32 halamanMijena Khalil AEShung kungBelum ada peringkat

- UNIT 4ADokumen20 halamanUNIT 4Asofiashaik414Belum ada peringkat

- EEE 304 Experiment No. 04 Name of The Experiment: Design of Decoder/Encoder/Multiplexer CircuitDokumen5 halamanEEE 304 Experiment No. 04 Name of The Experiment: Design of Decoder/Encoder/Multiplexer CircuitAurongo NasirBelum ada peringkat

- EEE 304 - Exp4 PDFDokumen5 halamanEEE 304 - Exp4 PDFAurongo NasirBelum ada peringkat

- VTU LD Lab ManualDokumen5 halamanVTU LD Lab ManualManjesh ShettyBelum ada peringkat

- VLSI Design Advanced Lab ManualDokumen74 halamanVLSI Design Advanced Lab ManualShiraz HusainBelum ada peringkat

- Logic GateDokumen21 halamanLogic GateArup DeyBelum ada peringkat

- Cmos Technology Team MembersDokumen8 halamanCmos Technology Team MembersMuhammad Tayyab MadniBelum ada peringkat

- Project AssignmentDokumen2 halamanProject AssignmentbatoolBelum ada peringkat

- Vlsi Es Lab Manual 4TH Year 2018 PDFDokumen103 halamanVlsi Es Lab Manual 4TH Year 2018 PDFబొమ్మిరెడ్డి రాంబాబుBelum ada peringkat

- 08 - IP Communication - E0510aDokumen13 halaman08 - IP Communication - E0510aWindy Ban100% (1)

- Introduction-to-XOR-GateDokumen13 halamanIntroduction-to-XOR-Gatedhruvivirani2611Belum ada peringkat

- ECE 301 - Digital Electronics: NAND and NOR Circuits, Multi-Level Logic Circuits, and Multiple-Output Logic CircuitsDokumen30 halamanECE 301 - Digital Electronics: NAND and NOR Circuits, Multi-Level Logic Circuits, and Multiple-Output Logic CircuitsVIKH33Belum ada peringkat

- TP3 Basic GatesDokumen19 halamanTP3 Basic GatesYasmine KessabBelum ada peringkat

- DCS-2 Practical File Part-1Dokumen26 halamanDCS-2 Practical File Part-1ykr007Belum ada peringkat

- Logic Gate - WikipediaDokumen11 halamanLogic Gate - WikipediayugalkishorBelum ada peringkat

- Question Bank - Digital Logic CircuitDokumen14 halamanQuestion Bank - Digital Logic CircuitthamizmaniBelum ada peringkat

- VHDL ProgramsDokumen30 halamanVHDL ProgramsVijay Singh100% (1)

- Application of Logic Gates: - Application Note - Andrew Herman ECE480 - Team 5 3/30/2007Dokumen7 halamanApplication of Logic Gates: - Application Note - Andrew Herman ECE480 - Team 5 3/30/2007Norazdila Mohd SallehBelum ada peringkat

- B.Tech, Ece Vlsi Design Lab: Part-A List of Experiments: S.No. Name of The ExperimentDokumen103 halamanB.Tech, Ece Vlsi Design Lab: Part-A List of Experiments: S.No. Name of The ExperimentMohammedAbdulAzeemBelum ada peringkat

- Labs-VLSI Lab ManualDokumen56 halamanLabs-VLSI Lab ManualAbdul Basit Awan50% (2)

- ElectroencephalogramDokumen21 halamanElectroencephalogramananthadiga100% (1)

- Parallel AdderDokumen20 halamanParallel AddermdbelalrshdBelum ada peringkat

- Synchronous Digital SystemDokumen6 halamanSynchronous Digital SystemmdbelalrshdBelum ada peringkat

- Bootstrapped Full-Swing CMOS Driver For Low Supply Voltage OperationDokumen2 halamanBootstrapped Full-Swing CMOS Driver For Low Supply Voltage OperationmdbelalrshdBelum ada peringkat

- Risc and PentiumDokumen28 halamanRisc and PentiumMohabbatRJBelum ada peringkat

- Assignment 3Dokumen3 halamanAssignment 3Tayyab Abbas100% (1)

- Finite State Machine Design: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998Dokumen47 halamanFinite State Machine Design: Prith Banerjee Ece C03 Advanced Digital Design Spring 1998VIKRAMBelum ada peringkat

- Digital Adder Circuits Review Power Delay Area Transistor CountDokumen15 halamanDigital Adder Circuits Review Power Delay Area Transistor CountDeepak SharmaBelum ada peringkat

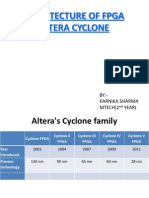

- Architecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)Dokumen29 halamanArchitecture of Fpga Altera Cyclone: BY:-Karnika Sharma Mtech (2 Year)karnika143100% (1)

- Aa VQ 3: MSL V C×WZ I Wwwruvj WWFVBMDokumen40 halamanAa VQ 3: MSL V C×WZ I Wwwruvj WWFVBMMd. Zahir UddinBelum ada peringkat

- Sisteme de Prelucrare Numerica Cu ProcesoareDokumen189 halamanSisteme de Prelucrare Numerica Cu ProcesoareDonFedoBelum ada peringkat

- CMOS Digital VLSI Design Periodical Test ReviewDokumen4 halamanCMOS Digital VLSI Design Periodical Test ReviewDarwinBelum ada peringkat

- Unit-5 QBDokumen28 halamanUnit-5 QBekvblsa vksvlijierigbBelum ada peringkat

- Unit 117 Digital and Analogue Devices and CircuitsDokumen4 halamanUnit 117 Digital and Analogue Devices and Circuits0dkBelum ada peringkat

- Technical Reference Manual (TRM) : Psoc Mixed Signal ArrayDokumen542 halamanTechnical Reference Manual (TRM) : Psoc Mixed Signal ArrayArie LitbakBelum ada peringkat

- Harvard ArchitectureDokumen16 halamanHarvard ArchitecturesheikmydeenBelum ada peringkat

- LPC17xx User ManualDokumen809 halamanLPC17xx User ManualJohn Paul100% (1)

- 8085 Addressing Modes: Dayanand KDokumen16 halaman8085 Addressing Modes: Dayanand KBhavya Babu100% (1)

- High-power NPN transistor specsDokumen3 halamanHigh-power NPN transistor specsJavier Mendoza CastroBelum ada peringkat

- MALP Unit 3 29092015 065135AMDokumen15 halamanMALP Unit 3 29092015 065135AMN LOKESWARIBelum ada peringkat

- Eceg3202 - Computer Architecture and OrganizationDokumen41 halamanEceg3202 - Computer Architecture and OrganizationAnonymous AFFiZnBelum ada peringkat

- Computer Organization-Single CycleDokumen23 halamanComputer Organization-Single Cyclev2brotherBelum ada peringkat

- St Joseph's College student's term paper on 8086 MicroprocessorDokumen37 halamanSt Joseph's College student's term paper on 8086 MicroprocessorWren D'silvaBelum ada peringkat

- Micro P Test 2 SkemaDokumen3 halamanMicro P Test 2 Skemasemuty92Belum ada peringkat

- Review Review Technology Technology: Advancements AdvancementsDokumen9 halamanReview Review Technology Technology: Advancements AdvancementsFatih KarabacakBelum ada peringkat

- Gate-Level AnalysisDokumen12 halamanGate-Level AnalysisSaiprasanth KilaruBelum ada peringkat

- DDHDLDokumen68 halamanDDHDLManoj VarmaBelum ada peringkat

- Put Question Paper (Ec-302)Dokumen3 halamanPut Question Paper (Ec-302)Anonymous eWMnRr70qBelum ada peringkat

- Introduction 1Dokumen5 halamanIntroduction 1Hogr RgohBelum ada peringkat

- Amlogic S905X S905L GPIO User Guide V0.2-WesionDokumen13 halamanAmlogic S905X S905L GPIO User Guide V0.2-WesionGugu ZumzumBelum ada peringkat

- Verilog QuestionsDokumen22 halamanVerilog Questionsnaren_reddysBelum ada peringkat

- Understanding the MIPS Processor PipelineDokumen149 halamanUnderstanding the MIPS Processor Pipelineayylmao kekBelum ada peringkat

- Computer Organisation Structure Components Arithmetic CPUDokumen2 halamanComputer Organisation Structure Components Arithmetic CPUsatyanarayana197Belum ada peringkat

- Basic GateDokumen5 halamanBasic Gatemsjunaid02Belum ada peringkat