Microprocessor 80386

Diunggah oleh

Chanthini VinayagamDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Microprocessor 80386

Diunggah oleh

Chanthini VinayagamHak Cipta:

Format Tersedia

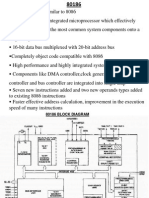

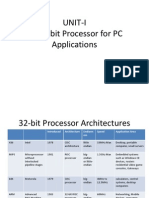

80386 Some of the limitations of the 80286 microprocessor are that it has only a 16-bit ALU, its maximum

segment size is 64 Kbytes, and it cannot easily be switched back and forth between real and protected modes. The Intel 80386 microprocessor was designed to overcome these limits, wile maintaining software compatibility with the 80286 and earlier processors. The 80386 has a 32-bit ALU, so it can operate directly on 32-bit data words. 80386 segments can be as large as 4 Gbytes and a program can have as many as 16,384 segments. The virtual address space then is 16,384 segments * 4 Gbytes, or about 64 Tbytes. A 32-bit address bus allows an 80386 to address up to 4 Gbytes of physical memory. The 80386 has a virtual 8086 mode, which allows it to easily switch back and forth between 80386 protected-mode tasks and 8086 real-mode tasks. The 80386 processor is available in two different versions, the 386DX and the 386SX. The 386DX has a 32-bit address bus and a 32-bit data bus. 80386 architecture is shown in figure 5.5. It is packaged in the 132-pin ceramic pin grid array package, the 386DX, which is packaged in the 100-pin flatpack are shown in figure 5.6, has the same internal architecture as the 386SX, but it has only a 24-bit address bus and a 16-bit data bus. The lower cost package and the ease of interfacing to 8-bit and 16-bit memory and peripherals make the 386SX suitable for us in lower cost systems. The trade-off here, of course, is that the 386SX address range and memory transfer rate are lower than those of the 386DX. The clock signal applied to the 386 CLK2 input is internally divided by 2 to produce the clock signal, which actually drives processor operations. The 386 address bus consists of the A2-A31 address lines and the byte enable lines BE0# BE3#. The BE0#-BE3# lines are decoded from internal address signals A0 and A1 and function very similarly to the way A0 and BHE function in an 8086 or 80286 system. The 386 has a 32-bit data bus, so memory can be set up as four byte-wide banks. The BE0# - BE3# signals function as enables for the four banks. These individual enables allow the 386 to transfer bytes, words, or double words to and from memory. Incidentally, the # symbol after the BE signal names indicates that these signals are active low.

The bus cycle definition signals identify the type of operation that is occurring during a bus cycle. The WR/R# signal indicates whether read or write operation is taking place and the D/C# indicates whether the bus operation is a data read/write or a control-word transfer such as an op-code fetch. M/IO# indicates whether the operation is a memory or a direct input/output operation. Incidentally, the 386 direct I/O port structure is simply an extension of the 8086 and 80286 port structures to include 32-bit ports. Simple 32-bit I/O ports can be constructed by connecting 8-bit I/O port devices such as the 8255A in parallel. A 386 can use an IN or OT instruction followed by an 8-bit port address to address up to 256 8-bit ports, 128 16-bit ports or 64 32-bit ports. Using the DX register to hold a 16-bit port address, a 386 can access up to 64K 8-bit ports, 32K 16-bit ports, or 8K 32-bit ports. The PEREQ signal is output by a coprocessor such as an 80387 floating point processor to tell the 386 to fetch the first part of a data word for the coprocessor. The coprocessor will then take over the buses and read the rest of the data word. The BUSY# signal is used by the coprocessor to prevent the 386 from going on with its next instruction before the coprocessor is finished with the current instruction. If the ERROR# signal is asserted by a coprocessor, the 386 will performs type 16 exception. Regarding the Vcc and ground connections, note in Figure 5.7 that the 386 has a large number of Vcc pins. It also has a large number of ground connections labeled Vss. These pins are all connected to the appropriate power plane in the PC board. The RESET, NMI, INTR, HOLD, and HLDA inputs function similarly to the way they do in earlier processors. The final group of 386 signals to discuss is the bus control group. The READY# signal is used to insert wait states in bus cycles as needed to interface with slow memory and I/O devices. The BS16# input allows the 386 to work with a 16-bit and/or a 32-bit data bus. If BS16# is asserted, the 386 will transfer data only on the lower half of the 32-bit data bus. If BS16# is asserted and a 32-bit operand is being read from a 16-bit wide memory, the 386 will automatically generate a second bus cycle to read the second word. The ADS# signal will be asserted when valid addresses, BE signals, and bus cycle definition signals are present on the buses. The 386 address bus is not multiplexed, so an 8086-type ALE signal is not needed.

However, in some 386 system the ADS# signal is used to transfer the address to the outputs of external latches for a scheme called address pipelining. The principle of address pipeline is that if an address is held on the outputs of external latches, the 386 can remove the old address from its address pins and output the address for the next operation earlier in the bus cycle. External control circuitry asserts the next address signal, NA#, to tell the 386 when to output the address for the next operation. Incidentally, the 386 contains a large amount of built-in self-test (BIST) circuitry. If the 386 BUSY# input is held low while RESET is held low, the processor will automatically test about 60 percent of its internal circuitry. The self-test requires about 2 power 20 CLK2 cycles. If the 386 passes all tests, a signature of all 0s will be left in the EAX register. The 80386 supports overall eleven addressing modes to facilitate efficient execution of higher level language programs. The 80386 has all the addressing modes, which were available with 80286. In case of all those modes, the 80386 can now have 32-bit immediate or 32-bit register operands or displacements. Besides these, the 80386 has a family of scaled modes. N case of scaled modes, any of the index register values can be multiplied by a valid scale factor to obtain the displacement. The valid scale factors re 1,2,4, and 8. The different scaled modes are discussed as follows. Scaled Indexed Modes : Contents of an index register are multiplied by a scale factor that may be added further to get the operand offset. Example: Mov EBX, LIST [ESI * 2 ] Based Scaled Indexed Mode: Contents of an index register are multiplied by a scale factor and then added to base register to obtain the offset. Example: Mov EBX, [EDX*4 ] [ECX] Based Scaled Indexed Mode with Displacement: The contents of an index register are multiplied by a scaling factor and the result is added to a base register and a displacement to get the offset of an operand Example: Mov EAX, LIST [ESI * 2 ] [EBX + 0800] The displacement may be any 8-bit or 32-bit immediate number. The base and index register may be any general purpose register except ESP.

The 80386 supports the following 17 data types. discussed here in brief. 1. Bit 2. Bit Field A group of at the most 32 bits

Each data type is

3. Bit string A string of contiguous bits of maximum 4Gbytes in length. 4. Signed Byte Signed bytedata 5. Unsigned Byte Unsigned bytedata 6. Integer word Signed 16-bit data 7. Long Integer 32-bit signed data represented in 2s complement form 8. Unsigned Integer word Unsigned 16-bit data 9. Unsigned Long Integer Unsigned 32-bit data 10. Signed Quad word A signed 64-bit data or four word data. 11. Unsigned Quad word An unsigned 64-bit data. 12. Offset A 16 or 32-bit displacement that references a memory location using any of the addressing modes 13. Pointer This consists of a pair of 16-bit selector and 16/32 bit offset. 14. Character An ASCII equivalent to any of the alphanumeric or control characters. 15. Strings- These are the sequence of bytes, words or double words. A string may contain minimum one byte and maximum 4 Giagabytes. 16. BCD decimal digits from 0-9 represented by unpacked bytes 17. Packed BCD This represents two packed BCD digits using a byte, i.e. form 00 to 99. The instruction set of 80386 contains all the instructions supported by 80286. The 80286 instructions are designed to operate with 8-bit or 16-bit data, while the same mnemonics for 80386 instructions set may be executed over 32-bit operands, besides 8-bit and 16-bitoperands. The newly added instructions may be categorized into the following functional groups. 1. Bit scan instructions BSF (bit scan forward), BSR (bit scan reverse) 2. Bit test instruction BT ( test a bit), BTC (test a bit and complement), BTR (test and reset a bit) and BTS ( test and set a bit). 3. Conditional set byte instructions SET ( Set on Overflow), SETNO (set on no overflow), and so on.

4. Shift double instructions- SHLD (shift left double), SHRD (shift right double) 5. Control transfer via gates instructions -.

Anda mungkin juga menyukai

- 8086 Third Term TopicsDokumen46 halaman8086 Third Term TopicsgandharvsikriBelum ada peringkat

- 80286 Processor Features for MultitaskingDokumen4 halaman80286 Processor Features for MultitaskingxorxorxorBelum ada peringkat

- NotesDokumen21 halamanNotesShinisg Vava50% (2)

- G MPMC U4 Rit 150 CopiesDokumen19 halamanG MPMC U4 Rit 150 CopiesBobby SatyaBelum ada peringkat

- Contents:: Salient Features of 80386 Functional Block Diagram of 80836 Pin Description of 8086Dokumen26 halamanContents:: Salient Features of 80386 Functional Block Diagram of 80836 Pin Description of 8086ajayBelum ada peringkat

- Registers and memory segmentation in 8086 microprocessorDokumen7 halamanRegisters and memory segmentation in 8086 microprocessorANIRUDDHA PAULBelum ada peringkat

- Microprocessor 80486Dokumen6 halamanMicroprocessor 80486Gaurav BisaniBelum ada peringkat

- Introduction to the 8086 MicroprocessorDokumen11 halamanIntroduction to the 8086 MicroprocessorYogesh KuteBelum ada peringkat

- Intel 8086 CPU Assembly LanguageDokumen4 halamanIntel 8086 CPU Assembly LanguageAparnaaBelum ada peringkat

- Intel 8086 Microprocessor Architecture GuideDokumen9 halamanIntel 8086 Microprocessor Architecture Guidedz15dzBelum ada peringkat

- and 80486Dokumen28 halamanand 80486sangeetaranjan0% (1)

- Chapter 3: Intel 8086Dokumen135 halamanChapter 3: Intel 8086singhrps8483% (6)

- Advanced Microprocessors: 80386 FeaturesDokumen14 halamanAdvanced Microprocessors: 80386 FeaturesSwamy NallabelliBelum ada peringkat

- Unit 2 16 Bit Microprocessors 8086/8088Dokumen33 halamanUnit 2 16 Bit Microprocessors 8086/8088Asha GusainBelum ada peringkat

- Unit 2Dokumen55 halamanUnit 2Shubhankit SinghBelum ada peringkat

- 8086 Bus Interface Unit and Execution Unit ElementsDokumen5 halaman8086 Bus Interface Unit and Execution Unit ElementsAndreas Pitziolis100% (1)

- Intel 80486 Microprocessor Architecture and FeaturesDokumen8 halamanIntel 80486 Microprocessor Architecture and FeaturesLALRAZBelum ada peringkat

- Advanced Microprocessor Presentation 4Dokumen21 halamanAdvanced Microprocessor Presentation 4Ubaid SaudagarBelum ada peringkat

- Address Multiplexing - Hardware Structure of 8086Dokumen57 halamanAddress Multiplexing - Hardware Structure of 8086Mike ThomsonBelum ada peringkat

- Minimum & Maximum Mode SystemsDokumen15 halamanMinimum & Maximum Mode Systemsrajesh5500Belum ada peringkat

- Organization of Intel 8086Dokumen10 halamanOrganization of Intel 8086Ashok ChakriBelum ada peringkat

- MP Viva Questions With AnswersDokumen13 halamanMP Viva Questions With AnswersDeepti ChandrasekharanBelum ada peringkat

- CS18303 Microprocessor and Microcontroller Lecture NotesDokumen160 halamanCS18303 Microprocessor and Microcontroller Lecture NotesDeepak SrinivasBelum ada peringkat

- Introduction to Microprocessor ArchitectureDokumen49 halamanIntroduction to Microprocessor ArchitectureVuggam VenkateshBelum ada peringkat

- Final ENCE 455 - ADVANCED MICROPROCESSOR SYSTEMS AND INTERFACING EXAMS - NOV 2021Dokumen8 halamanFinal ENCE 455 - ADVANCED MICROPROCESSOR SYSTEMS AND INTERFACING EXAMS - NOV 2021Crentsil KwayieBelum ada peringkat

- New Text DocumentDokumen15 halamanNew Text DocumentKanaan JalalBelum ada peringkat

- I Am Intel 8086Dokumen8 halamanI Am Intel 8086AB ESPORTSBelum ada peringkat

- Unit-I: - 80386 IntroductionDokumen74 halamanUnit-I: - 80386 IntroductionOmkar MarkadBelum ada peringkat

- Internal Architecture 8086Dokumen3 halamanInternal Architecture 8086firoz83% (6)

- MP-MC R16 - Unit-4Dokumen14 halamanMP-MC R16 - Unit-4satyanarayana12Belum ada peringkat

- Microprocessor Lab Viva Questions With AnswersDokumen13 halamanMicroprocessor Lab Viva Questions With AnswersTanvir KalhaBelum ada peringkat

- Architecture of 8086 MicroprocessorDokumen17 halamanArchitecture of 8086 MicroprocessorsreenimolBelum ada peringkat

- 80486Dokumen34 halaman80486Manoj RayBelum ada peringkat

- Unit 3 MicroprocessorDokumen155 halamanUnit 3 MicroprocessorHUISCIBelum ada peringkat

- Mic ProjectDokumen15 halamanMic Projectsudarshan sonawaneBelum ada peringkat

- AMI CHP 1 32bit 80386 FinalDokumen59 halamanAMI CHP 1 32bit 80386 FinalAliBelum ada peringkat

- 80386Dokumen89 halaman80386chandanayadav849050% (2)

- Explore the 80386SX Processor BusDokumen4 halamanExplore the 80386SX Processor Busmar_barudjBelum ada peringkat

- 354 39 Solutions Instructor Manual 13 Intel 8086 Microprocessor Architecture Features Signals Chapter 13Dokumen3 halaman354 39 Solutions Instructor Manual 13 Intel 8086 Microprocessor Architecture Features Signals Chapter 13Saravanan JayabalanBelum ada peringkat

- MP Unit-8 VtuDokumen10 halamanMP Unit-8 VtuBmvpBelum ada peringkat

- Microprocesser AssignmentDokumen15 halamanMicroprocesser AssignmentMukul RanaBelum ada peringkat

- Microprocessor NotesDokumen140 halamanMicroprocessor NotesSaquibh ShaikhBelum ada peringkat

- Microprocessor 80386Dokumen40 halamanMicroprocessor 80386eshwar_worldBelum ada peringkat

- 8086 Microprocessor Cheatsheet GuideDokumen17 halaman8086 Microprocessor Cheatsheet Guidedz15dzBelum ada peringkat

- The Complete Understanding of Microprocessors and Intro To ARMDokumen56 halamanThe Complete Understanding of Microprocessors and Intro To ARMasimBelum ada peringkat

- Introduction To Microprocessors and Processor Organization: 1. 8086 Microprocessor FeaturesDokumen41 halamanIntroduction To Microprocessors and Processor Organization: 1. 8086 Microprocessor FeaturesYash DagaBelum ada peringkat

- The 80386 MicroprocessorsDokumen24 halamanThe 80386 MicroprocessorsSourcecode BeeBelum ada peringkat

- Computer Architecture: Assignment: 80X86 FamilyDokumen17 halamanComputer Architecture: Assignment: 80X86 FamilyAnjan KumarBelum ada peringkat

- Microprocessors Memory Addressing and RegistersDokumen8 halamanMicroprocessors Memory Addressing and RegistersSaloniVarshneyBelum ada peringkat

- 6Dokumen35 halaman6Ankit Sethia100% (3)

- Adigrat University: Submitted To Inst. Mehari.G (Ass - Prof) SUBMISSION DATE 23/05/2011 E.CDokumen14 halamanAdigrat University: Submitted To Inst. Mehari.G (Ass - Prof) SUBMISSION DATE 23/05/2011 E.CGoitom HaileBelum ada peringkat

- Intel 8086 Microprocessor ArchitectureDokumen16 halamanIntel 8086 Microprocessor Architecturelu4rohitBelum ada peringkat

- MicroprocessorDokumen103 halamanMicroprocessorUbaid SaudagarBelum ada peringkat

- 2019-CPE-27 Microprocessor Assignment No 1Dokumen12 halaman2019-CPE-27 Microprocessor Assignment No 1Haalim MBelum ada peringkat

- Unit 1&3Dokumen18 halamanUnit 1&3Sreekanth PagadapalliBelum ada peringkat

- Microprocessor Unit-1 PART ADokumen12 halamanMicroprocessor Unit-1 PART ASasi BhushanBelum ada peringkat

- Architecture of 80386Dokumen39 halamanArchitecture of 80386Jaimon JacobBelum ada peringkat

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDari EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationBelum ada peringkat

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Dari EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Belum ada peringkat

- GM DietDokumen8 halamanGM DietChanthini Vinayagam100% (1)

- Understand the BCG growth-share matrix with this guideDokumen5 halamanUnderstand the BCG growth-share matrix with this guideChanthini VinayagamBelum ada peringkat

- StorytellingDokumen5 halamanStorytellingChanthini VinayagamBelum ada peringkat

- 30 Days Push Up ChallengeDokumen3 halaman30 Days Push Up ChallengeChanthini VinayagamBelum ada peringkat

- ModuleDokumen26 halamanModuleSantosh KumarBelum ada peringkat

- Basic Introduction Communicable DiseaseDokumen15 halamanBasic Introduction Communicable DiseaseChanthini VinayagamBelum ada peringkat

- Mohr V WilliamDokumen5 halamanMohr V WilliamChanthini VinayagamBelum ada peringkat

- Perception Online NotesDokumen13 halamanPerception Online NotesChanthini VinayagamBelum ada peringkat

- A Survey of TQM Application in Healthcare - Case Analysis: Chanthini.VDokumen15 halamanA Survey of TQM Application in Healthcare - Case Analysis: Chanthini.VChanthini VinayagamBelum ada peringkat

- ABCs of CPR: A Simple Life-Saving ProcedureDokumen3 halamanABCs of CPR: A Simple Life-Saving ProcedureChanthini VinayagamBelum ada peringkat

- Common Prefixes and SuffixesDokumen2 halamanCommon Prefixes and SuffixesChanthini Vinayagam100% (1)

- Concept and Principles of HomeopathyDokumen2 halamanConcept and Principles of HomeopathyChanthini VinayagamBelum ada peringkat

- MANAGING InfectionDokumen11 halamanMANAGING InfectionHumayun KhanBelum ada peringkat

- Cardinal Utility ApproachDokumen5 halamanCardinal Utility ApproachChanthini VinayagamBelum ada peringkat

- Sterilization Methods and PrinciplesDokumen11 halamanSterilization Methods and PrinciplesChanthini VinayagamBelum ada peringkat

- Approaches of MGMTDokumen17 halamanApproaches of MGMTChanthini VinayagamBelum ada peringkat

- Adv N Disadv of Privatisation of Health Sector in IndiaDokumen5 halamanAdv N Disadv of Privatisation of Health Sector in IndiaChanthini VinayagamBelum ada peringkat

- MotivationDokumen234 halamanMotivationChanthini VinayagamBelum ada peringkat

- Concepts and Principles of AyurvedaDokumen4 halamanConcepts and Principles of AyurvedaChanthini VinayagamBelum ada peringkat

- MBE NotesDokumen154 halamanMBE NotesSimson SimBelum ada peringkat

- Pharmaceutical Sterilization MethodsDokumen21 halamanPharmaceutical Sterilization MethodsSiva Raman100% (1)

- First Aid - CPR - AED Adult Ready ReferenceDokumen12 halamanFirst Aid - CPR - AED Adult Ready Referenceadamiam100% (1)

- The International Network of Health Promoting Hospitals and Health CareDokumen24 halamanThe International Network of Health Promoting Hospitals and Health CareChanthini Vinayagam100% (1)

- Highlights of National Health Policy 2002Dokumen5 halamanHighlights of National Health Policy 2002manasranjanpradhanBelum ada peringkat

- PhysiotherapyDokumen2 halamanPhysiotherapyChanthini VinayagamBelum ada peringkat

- Change Management Leadership GuideDokumen30 halamanChange Management Leadership GuideChanthini Vinayagam100% (2)

- 50 Home Remedies For Treating WrinklesDokumen5 halaman50 Home Remedies For Treating WrinklesChanthini VinayagamBelum ada peringkat

- Change Management Leadership GuideDokumen30 halamanChange Management Leadership GuideChanthini Vinayagam100% (2)

- Cupcake RecipesDokumen15 halamanCupcake RecipesChanthini VinayagamBelum ada peringkat

- Spru301c - Manual Ccs - Code Composer StudioDokumen126 halamanSpru301c - Manual Ccs - Code Composer StudioJandfor Tansfg ErrottBelum ada peringkat

- Living in The IT ERA PrelimsDokumen4 halamanLiving in The IT ERA PrelimsMiks Solon43% (7)

- Biology Test Series According to Smart SyllabusDokumen23 halamanBiology Test Series According to Smart SyllabusSaim ShahidBelum ada peringkat

- Slide-5 (8086 Maximum Mode)Dokumen13 halamanSlide-5 (8086 Maximum Mode)Hafsaa Binte HarunBelum ada peringkat

- Optimize B064 Series Service Mode DocumentDokumen212 halamanOptimize B064 Series Service Mode DocumentXelcop RojasBelum ada peringkat

- USB Pinout and WiringDokumen4 halamanUSB Pinout and WiringnelsonhooverBelum ada peringkat

- 994-0078 - D20 D200 Installation and Operations Guide V200 R7 PDFDokumen132 halaman994-0078 - D20 D200 Installation and Operations Guide V200 R7 PDFrommel76Belum ada peringkat

- Jul 08Dokumen61 halamanJul 08c_nghiaBelum ada peringkat

- Sri Vidya College of Engineering & Technology, Virudhunagar: Designed For Individual UseDokumen30 halamanSri Vidya College of Engineering & Technology, Virudhunagar: Designed For Individual UsevanithaBelum ada peringkat

- System Hardware Overview LectureDokumen45 halamanSystem Hardware Overview LectureHéctor RodríguezBelum ada peringkat

- Design AMBA-AXI Protocol VHDL SoCDokumen4 halamanDesign AMBA-AXI Protocol VHDL SoCBethuna Sayed100% (1)

- Bus System E65 745iDokumen51 halamanBus System E65 745iJean-Baptiste BulliardBelum ada peringkat

- NetBackup DeviceConfig GuideDokumen203 halamanNetBackup DeviceConfig GuidesanchetanparmarBelum ada peringkat

- Service Manual Atmos AtmosafeDokumen32 halamanService Manual Atmos AtmosafedhcastanoBelum ada peringkat

- Computer Organization & Architecture (KCA 105) : DR Manmohan Mishra Associate Professor MCA, DepartmentDokumen87 halamanComputer Organization & Architecture (KCA 105) : DR Manmohan Mishra Associate Professor MCA, DepartmentDolly SrivastavaBelum ada peringkat

- Twister V 06 FrenchDokumen103 halamanTwister V 06 FrenchDaud Jiong KIM100% (2)

- Infineon-AN75705 Getting Started With EZ-USB FX3-UserManual-V11 00-EnDokumen49 halamanInfineon-AN75705 Getting Started With EZ-USB FX3-UserManual-V11 00-EnvvviiinnnoooBelum ada peringkat

- CHS NC II Exam GuideDokumen10 halamanCHS NC II Exam GuideKristine CapaoBelum ada peringkat

- CTSiDokumen114 halamanCTSiAnzi100% (6)

- CO - Chap 1Dokumen33 halamanCO - Chap 1Nidhi SrivastavaBelum ada peringkat

- Structural Units in Embedded ProcessorDokumen12 halamanStructural Units in Embedded ProcessorAJITH KANNANBelum ada peringkat

- TMS320C5x: By-D.Jenny SimpsolinDokumen28 halamanTMS320C5x: By-D.Jenny SimpsolinjennybunnyomgBelum ada peringkat

- Generic Megarac SP-X Firmware: Engineering Unit Test DocumentDokumen12 halamanGeneric Megarac SP-X Firmware: Engineering Unit Test DocumentPreethi KalaiselvamBelum ada peringkat

- A Master Boot RecordDokumen4 halamanA Master Boot RecordmacakenaBelum ada peringkat

- PACiS GTW EN O C80Dokumen170 halamanPACiS GTW EN O C80paradiseparasBelum ada peringkat

- 03 FA31323EN32GA0 fmx2 PDFDokumen50 halaman03 FA31323EN32GA0 fmx2 PDFkalwar98esBelum ada peringkat

- Hardware Components Inside a Computer CaseDokumen33 halamanHardware Components Inside a Computer CaseRIZALDY CANTOBelum ada peringkat

- Memory BIST Tutorial PDFDokumen22 halamanMemory BIST Tutorial PDFSiva SreeramdasBelum ada peringkat

- CS401 MCQs Assembly Language ProgrammingDokumen44 halamanCS401 MCQs Assembly Language Programminginbox_kansal547967% (48)

- Register Transfer and MicrooperationsDokumen33 halamanRegister Transfer and Microoperationssara_loloBelum ada peringkat

- ST7920 Chinese LCD Controller with Built-in FontsDokumen49 halamanST7920 Chinese LCD Controller with Built-in FontsteveliskalvelisBelum ada peringkat