Ec1207 7

Diunggah oleh

BaskyDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Ec1207 7

Diunggah oleh

BaskyHak Cipta:

Format Tersedia

LOGICAL INSTRUCTIONS

Opcode Operand Explanation Instruction of Description The contents of the operand (register or memory) are M compared with the contents of the accumulator. Both contents are preserved . The result of the comparison is shown by setting the flags of the PSW as follows: R CMP M Compare register or memory with if (A) < (reg/mem): carry accumulator if (A) = (reg/mem): zero if (A) > (reg/mem): carry and zero flags are reset Example: CMP B or CMP M The second byte (8-bit data) is compared with the contents of the accumulator. The values being compared remain unchanged. The result of the comparison is shown by setting the flags of the PSW as follows: CPI 8-bit data Compare immediate if (A) < data: carry with accumulator if (A) = data: zero if (A) > data: carry and zero flags are reset Example: CPI 89H The contents of the accumulator are logically ANDed with M the contents of the operand (register or memory), and the result is placed in the accumulator. Logical AND register If the operand is a memory location, its address is specified by the contents of or memory with HL registers. S, Z, P are modified to reflect the result of the operation. CY is reset. AC is set. accumulator Example: ANA B or ANA M Logical immediate accumulator The contents of the accumulator are logically ANDed with 8-bit data (operand) and the result is placed in AND accumulator. S, Z, P are modified to reflect the result of with operation. CY is reset. AC is set. Example: ANI 86H R XRA M 8-bit data R ORA M 8-bit data none The contents of the accumulator are Exclusive ORed with M the contents of Exclusive OR the operand (register or memory), and the result is placed in the accumulator. register or memory If the operand is a memory location, its address is specified by the contents of with accumulator HL registers. S, Z, P are modified to reflect the result of the operation. CY and AC are reset.Example: XRA B or XRA M Exclusive immediate accumulator OR The contents of the accumulator are Exclusive ORed with the 8-bit data with (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY and AC are reset.Example: XRI 86H the the the flag flag is is set set flag flag is is set set

R ANA M

ANI

8-bit data

XRI

The contents of the accumulator are logically ORed with M the contents of the Logical OR register operand (register or memory), and the result is placed in the accumulator. If or memory with the operand is a memory location, its address is specified by the contents of accumulator HL registers. S, Z, P are modified to reflect the result of the operation. CY and AC are reset.Example: ORA B or ORA M Logical immediate accumulator OR The contents of the accumulator are logically ORed with the 8-bit data with (operand) and the result is placed in the accumulator. S, Z, P are modified to reflect the result of the operation. CY and AC are reset.Example: ORI 86H

ORI

RLC

Each binary bit of the accumulator is rotated left by one position. Bit D7 is Rotate accumulator placed in the position of D0 as well as in the Carry flag. CY is modified left according to bit D7. S, Z, P, AC are not affected.Example: RLC Each binary bit of the accumulator is rotated right by one position. Bit D0 is Rotate accumulator placed in the position of D7 as well as in the Carry flag. CY is modified right according to bit D0. S, Z, P, AC are not affected.Example: RRC Rotate accumulator Each binary bit of the accumulator is rotated left by one position through the left through carry Carry flag. Bit D7 is placed in the Carry flag, and the Carry flag is placed in the

RRC RAL

none none

least significant position D0. CY is modified according to bit D7. S, Z, P, AC are not affected. Example: RAL RAR none Each binary bit of the accumulator is rotated right by one position through the Rotate accumulator Carry flag. Bit D0 is placed in the Carry flag, and the Carry flag is placed in the right through carry most significant position D7. CY is modified according to bit D0. S, Z, P, AC are not affected.Example: RAR Complement accumulator The contents of the accumulator are complemented. No flags are affected. Example: CMA The Carry flag is complemented. No other flags are affected. CMC none Complement carry Example: CMC Set Carry STC none Set Carry Example: STC

CMA

none

CONTROL INSTRUCTIONS

Opcode Operand Explanation Instruction No operation of Description No operation is performed. The instruction is fetched and decoded. However no operation is executed. Example: NOP HLT none Halt and enter wait The CPU finishes executing the current instruction and halts any further execution. An state interrupt or reset is necessary to exit from the halt state. Example: HLT DI none Disable interrupts The interrupt enable flip-flop is reset and all the interrupts except the TRAP are disabled. No flags are affected. Example: DI The interrupt enable flip-flop is set and all interrupts are enabled. No flags are affected. After a system reset or the acknowledgement of an interrupt, the interrupt enable flipflop is reset, thus disabling the interrupts. This instruction is necessary to reenable the interrupts (except TRAP). Example: EI This is a multipurpose instruction used to read the status of interrupts 7.5, 6.5, 5.5 and read serial data input bit. The instruction loads eight bits in the accumulator with the following interpretations. Example: Interrupt masked if bit = 1 RIM none Read interrupt mas

NOP

none

EI

none

Enable interrupts

SID I7

SERIAL INPUT DATA BIT

I6

I5

IE

7.5

6.5

5.5

Interrupt enable flip-flop is set if bit =1 Interrupts pending if

SIM

none

This is a multipurpose instruction and used to implement the 8085 interrupts 7.5, 6.5, 5.5, and serial data output. The instruction interprets the accumulator contents as Set interrupt mask follows. Example: SIM

Anda mungkin juga menyukai

- Projects With Microcontrollers And PICCDari EverandProjects With Microcontrollers And PICCPenilaian: 5 dari 5 bintang5/5 (1)

- Control of DC Motor Using Different Control StrategiesDari EverandControl of DC Motor Using Different Control StrategiesBelum ada peringkat

- 8085 Instruction Set Logical Instruction Control Instruction Branch InstructionDokumen8 halaman8085 Instruction Set Logical Instruction Control Instruction Branch InstructionJayant ChoudharyBelum ada peringkat

- Lec - 5 Micro MustDokumen29 halamanLec - 5 Micro Mustajf3215Belum ada peringkat

- Arithmetic Instructions PDFDokumen2 halamanArithmetic Instructions PDFAhmedBelum ada peringkat

- Instruction Set 8085Dokumen15 halamanInstruction Set 8085MuhammadAli VellaniBelum ada peringkat

- Instruction Set of 8085Dokumen82 halamanInstruction Set of 8085Bibin LeeBelum ada peringkat

- 8085 Instruction SetDokumen12 halaman8085 Instruction Setkushal basuBelum ada peringkat

- 8085 Instruction SetDokumen14 halaman8085 Instruction SetRahul GroverBelum ada peringkat

- 8085 Instruction SetDokumen15 halaman8085 Instruction SetJaya BagariaBelum ada peringkat

- Lec - 4 Micro MustDokumen36 halamanLec - 4 Micro Mustajf3215Belum ada peringkat

- 8085 Instructions - Arithmetic: InstructionDokumen4 halaman8085 Instructions - Arithmetic: InstructionBaskyBelum ada peringkat

- Instructionset 8085Dokumen15 halamanInstructionset 8085TobiUchihaBelum ada peringkat

- Opcodes 8085Dokumen9 halamanOpcodes 8085Abd Ur Rehman NiaziBelum ada peringkat

- Ee 2354 Model Ans KeyDokumen25 halamanEe 2354 Model Ans KeyHusamHaskoBelum ada peringkat

- 3 - Z80 Intsruction Set and Programming TechniquesDokumen8 halaman3 - Z80 Intsruction Set and Programming TechniquesMohamed Ouail CHARAOUIBelum ada peringkat

- Unit 2 MPDokumen121 halamanUnit 2 MPAmjad HussainBelum ada peringkat

- Logical Instructions5Dokumen23 halamanLogical Instructions5ihg9Belum ada peringkat

- Instruction Set of 8085 Compatibility ModeDokumen82 halamanInstruction Set of 8085 Compatibility ModeParth MadanBelum ada peringkat

- Instruction SET OF 8085: Bsc-It CrackedDokumen90 halamanInstruction SET OF 8085: Bsc-It CrackedtbijleBelum ada peringkat

- Instruction Set of 8085Dokumen81 halamanInstruction Set of 8085mohit mishraBelum ada peringkat

- By: Dr. Anil Swarnkar Assistant Professor Department of Electrical Engineering, MNIT, JaipurDokumen115 halamanBy: Dr. Anil Swarnkar Assistant Professor Department of Electrical Engineering, MNIT, Jaipurpankajkthr100% (2)

- Unit 2Dokumen166 halamanUnit 2rohanrec92Belum ada peringkat

- 8085 Instruction SetDokumen75 halaman8085 Instruction SetInfinity Star GamingBelum ada peringkat

- 05 - Instruction Set of 8085 and QuestionsDokumen110 halaman05 - Instruction Set of 8085 and Questionsgill1234jassiBelum ada peringkat

- Instruction Set of 8085 - GDLCDokumen82 halamanInstruction Set of 8085 - GDLCkaushikei22Belum ada peringkat

- 8051 Architecture FullDokumen39 halaman8051 Architecture FullRaja RajBelum ada peringkat

- Ce089 Aaryan Parpyani Csa Lab02Dokumen12 halamanCe089 Aaryan Parpyani Csa Lab02Aaryan parpyani.Belum ada peringkat

- Control Instructions: Opcode Operand Explanation of Instruction DescriptionDokumen15 halamanControl Instructions: Opcode Operand Explanation of Instruction DescriptionVishesh ShrivastavaBelum ada peringkat

- CAT II Answer Key Year/Sem: III/VI Part A: Institute of TechnologyDokumen27 halamanCAT II Answer Key Year/Sem: III/VI Part A: Institute of TechnologyHusamHaskoBelum ada peringkat

- Different Groups of Instructions in Instruction Set of 8088/8086Dokumen13 halamanDifferent Groups of Instructions in Instruction Set of 8088/8086Beny NurmandaBelum ada peringkat

- Ee6502 MM Eee VST Au Units IIDokumen19 halamanEe6502 MM Eee VST Au Units IIRaad AljuboryBelum ada peringkat

- 8085 Instruction SetDokumen122 halaman8085 Instruction Setgokulchandru100% (1)

- Laboratory Manual Microprocessor 8085: SL - No. Name of The Experiments NoDokumen25 halamanLaboratory Manual Microprocessor 8085: SL - No. Name of The Experiments NobhaswatiBelum ada peringkat

- The 8085 Instruction SetDokumen30 halamanThe 8085 Instruction SetSindu RangaswamyBelum ada peringkat

- Ec522 8051 04Dokumen125 halamanEc522 8051 04Anurag BansalBelum ada peringkat

- BGK MPMC Unit-4 Q and ADokumen9 halamanBGK MPMC Unit-4 Q and AMallesh ArjaBelum ada peringkat

- Poriyaan 1tQbxcNyzLs68k-HEpHbduw6uMliQ220NDokumen19 halamanPoriyaan 1tQbxcNyzLs68k-HEpHbduw6uMliQ220NS. GobikaBelum ada peringkat

- Unit 2Dokumen18 halamanUnit 2Vasunthara DBelum ada peringkat

- 8085 Lab ManualDokumen19 halaman8085 Lab Manualgurupatel279Belum ada peringkat

- Logical OperationsDokumen6 halamanLogical OperationsLysergic WarNrumorBelum ada peringkat

- Microprocessor 8085 Lab ManualDokumen29 halamanMicroprocessor 8085 Lab Manualmichaeledem_royal100% (1)

- 202004021910157352aksingh Phy MicroprocessorDokumen20 halaman202004021910157352aksingh Phy MicroprocessorAviBelum ada peringkat

- Addressing Modes & Instruction SetDokumen39 halamanAddressing Modes & Instruction SetlekaBelum ada peringkat

- 2a. CS602 Microprocessor and Microcontroller - SoftwareDokumen44 halaman2a. CS602 Microprocessor and Microcontroller - SoftwareRehan NightBelum ada peringkat

- Addressing Modes and Instructions in 8085Dokumen18 halamanAddressing Modes and Instructions in 8085Ishmeet KaurBelum ada peringkat

- 8051 InstructionsDokumen24 halaman8051 InstructionsMurali VannappanBelum ada peringkat

- Microprocessors (Bcst601)Dokumen61 halamanMicroprocessors (Bcst601)surbhiBelum ada peringkat

- Microprocessor 8085, 86, 51 Instruction SetDokumen15 halamanMicroprocessor 8085, 86, 51 Instruction SetDeepak DennisonBelum ada peringkat

- Machine Architecture (Instruction Set 8085)Dokumen11 halamanMachine Architecture (Instruction Set 8085)Shubham KediaBelum ada peringkat

- Addressing Modes & Instructions Set of 8051 Micro ControllerDokumen29 halamanAddressing Modes & Instructions Set of 8051 Micro ControllerNittur Nanjundaswamy NagendraBelum ada peringkat

- Lab03 Lab04 MPDokumen29 halamanLab03 Lab04 MPCarlton ChongBelum ada peringkat

- 8051 InstructionsDokumen24 halaman8051 Instructionssasitharan33Belum ada peringkat

- Instruction Set of 8051Dokumen17 halamanInstruction Set of 8051Amarjeet KumarBelum ada peringkat

- Phu Luc 4 Mo Ta Tap Lenh Vi Dieu Khien MCS-51 - Smith.N StudioDokumen40 halamanPhu Luc 4 Mo Ta Tap Lenh Vi Dieu Khien MCS-51 - Smith.N StudioSmith Nguyen StudioBelum ada peringkat

- lệnh 8051Dokumen71 halamanlệnh 8051Kim MạnhBelum ada peringkat

- Familiarization With Logical InstructionsDokumen2 halamanFamiliarization With Logical InstructionsSagar TimalsinaBelum ada peringkat

- Instruction Set of 8085Dokumen81 halamanInstruction Set of 8085Tanmoy DeyBelum ada peringkat

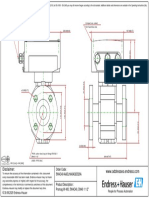

- 5W4C40 AADLHA0AQD320A Endress+HauserConsultAG 2DDrawing 09 30 2020Dokumen1 halaman5W4C40 AADLHA0AQD320A Endress+HauserConsultAG 2DDrawing 09 30 2020BaskyBelum ada peringkat

- 5002 325 00GCB01 &etc010 006851 - R03Dokumen36 halaman5002 325 00GCB01 &etc010 006851 - R03BaskyBelum ada peringkat

- Working at Height Risk AssessmentDokumen9 halamanWorking at Height Risk AssessmentBasky0% (1)

- 10W80 FC0A1AA0A4AA Endress+HauserConsultAG 2DDrawing 09 30 2020Dokumen1 halaman10W80 FC0A1AA0A4AA Endress+HauserConsultAG 2DDrawing 09 30 2020BaskyBelum ada peringkat

- Risk Assessment Guide 1Dokumen3 halamanRisk Assessment Guide 1BaskyBelum ada peringkat

- Emotron vfx2 0 - Manual - 01 5326 01r1.enDokumen222 halamanEmotron vfx2 0 - Manual - 01 5326 01r1.enBaskyBelum ada peringkat

- Catalog-Basket ScreenDokumen2 halamanCatalog-Basket ScreenBaskyBelum ada peringkat

- Embedded System Lab Manual Final Complete FinalDokumen110 halamanEmbedded System Lab Manual Final Complete FinalBasky100% (5)

- Ee6801 Scad MSMDokumen93 halamanEe6801 Scad MSMBasky100% (1)

- SS Question BankDokumen6 halamanSS Question BankbinukirubaBelum ada peringkat

- EC6302 Digital Electronics 2 Marks With AnswersDokumen18 halamanEC6302 Digital Electronics 2 Marks With AnswersBasky40% (5)

- Firstyear Online Submission Instructions InstallationDokumen27 halamanFirstyear Online Submission Instructions InstallationBaskyBelum ada peringkat

- Me2255 Introduction To TransistorDokumen12 halamanMe2255 Introduction To TransistorBaskyBelum ada peringkat

- 8085 Instructions - Arithmetic: InstructionDokumen4 halaman8085 Instructions - Arithmetic: InstructionBaskyBelum ada peringkat

- Cs 1028 Wireless NetworksDokumen4 halamanCs 1028 Wireless NetworksBaskyBelum ada peringkat

- Ec 1354 Vlsi DesignDokumen5 halamanEc 1354 Vlsi Designdhasarathan_rajaBelum ada peringkat

- RojaDokumen3 halamanRojaBaskyBelum ada peringkat

- IndiaDokumen18 halamanIndiaBaskyBelum ada peringkat

- Embedded Systems BooksDokumen1 halamanEmbedded Systems BooksBaskyBelum ada peringkat

- ER-260 265 AU User ManualDokumen109 halamanER-260 265 AU User ManualRadu Baciu-NiculescuBelum ada peringkat

- STRSW ILT D8CADM REV03 - LabSetupGuideDokumen8 halamanSTRSW ILT D8CADM REV03 - LabSetupGuideJayakanthBelum ada peringkat

- Modul SMK Kelas Xii Semester 1Dokumen39 halamanModul SMK Kelas Xii Semester 1Anonymous DSPDrcT100% (2)

- PM0019l - Explosion-Proof LAK Series BeaconsDokumen2 halamanPM0019l - Explosion-Proof LAK Series BeaconsImran TajBelum ada peringkat

- Fundamentals of The Matrix Converter TechnologyDokumen7 halamanFundamentals of The Matrix Converter Technologylizard_007Belum ada peringkat

- Manual Plant 4D Athena SP2 - Installation-MasterDokumen65 halamanManual Plant 4D Athena SP2 - Installation-Masterjimalt67Belum ada peringkat

- EN - JaZUp User Guide 2.4 PDFDokumen17 halamanEN - JaZUp User Guide 2.4 PDFDeterette Deterettek0% (1)

- Cleco CorporationDokumen8 halamanCleco CorporationneelgalaBelum ada peringkat

- Analogue and Digital Electronics - Student WorkbookDokumen53 halamanAnalogue and Digital Electronics - Student WorkbookBluff FlersBelum ada peringkat

- Documentation Banana Island+PSD+3DDokumen10 halamanDocumentation Banana Island+PSD+3DdededuduBelum ada peringkat

- 3RG7843 enDokumen62 halaman3RG7843 enRaj ChavanBelum ada peringkat

- Salwico Cargo Addressable Installation Manual EDokumen74 halamanSalwico Cargo Addressable Installation Manual EAshish DharjiyaBelum ada peringkat

- Strategic Goods Control Order ADokumen284 halamanStrategic Goods Control Order Ahongping85Belum ada peringkat

- Diodes and Resistors Data SheetDokumen2 halamanDiodes and Resistors Data SheetAlex SouzaBelum ada peringkat

- Parts ManualDokumen26 halamanParts ManualsleonBelum ada peringkat

- MS309 Manual - V1.01 PDFDokumen32 halamanMS309 Manual - V1.01 PDFtidchong prakoonmongkoneBelum ada peringkat

- The Doremi SeismographDokumen11 halamanThe Doremi SeismographRandy Achmad SaputraBelum ada peringkat

- Lathe Controller 990Dokumen128 halamanLathe Controller 990Shabbir HussainBelum ada peringkat

- TOA Ev20rDokumen24 halamanTOA Ev20rCheco PachecoBelum ada peringkat

- Device ManagementDokumen57 halamanDevice Managementjobster1967Belum ada peringkat

- Cisco Aironet 2700 Series Access Points: High Density Experience (HD Experience)Dokumen10 halamanCisco Aironet 2700 Series Access Points: High Density Experience (HD Experience)juanBelum ada peringkat

- 2012 06 Openwells Mobile For Workovers Data Sheet PDFDokumen2 halaman2012 06 Openwells Mobile For Workovers Data Sheet PDFWilman Ardila BarbosaBelum ada peringkat

- Asian Development Foundation College: Lesson No.: 1 Hardware BasicsDokumen6 halamanAsian Development Foundation College: Lesson No.: 1 Hardware Basicsjan niño villacorteBelum ada peringkat

- Programming1 - In-Java PDFDokumen147 halamanProgramming1 - In-Java PDFPedjaBelum ada peringkat

- Unit 1 - Lab 1-FlowchartDokumen6 halamanUnit 1 - Lab 1-FlowchartSon DavidBelum ada peringkat

- Oxford EQ ManualDokumen29 halamanOxford EQ ManualCasar1973Belum ada peringkat

- Overview Presentation - It Essentials - CCNADokumen37 halamanOverview Presentation - It Essentials - CCNAEuber ChaiaBelum ada peringkat

- OMNI User ManualDokumen113 halamanOMNI User ManualStruggle HardBelum ada peringkat

- En ACS880 Winder CTRL PRG FW A A4Dokumen520 halamanEn ACS880 Winder CTRL PRG FW A A4Dražen ŠukecBelum ada peringkat

- Heroes Every Child Should Know by Mabie, Hamilton Wright, 1845-1916Dokumen185 halamanHeroes Every Child Should Know by Mabie, Hamilton Wright, 1845-1916Gutenberg.orgBelum ada peringkat