Alphanumeric App Notes

Diunggah oleh

Jose PerezDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Alphanumeric App Notes

Diunggah oleh

Jose PerezHak Cipta:

Format Tersedia

Application Notes

Intelligent Alphanumeric Application Notes Intelligent Alphanumeric Displays

Interface Specications

Specications for AND Intelligent Alphanumeric displays are given in this section. The LCD controller used is the HD44780 or equivalent. AND671GST/GST-LED AND471GST/GST-LED AND481GST/GST-LED AND491GST/GST-LED AND501GST/GST-LED AND731GST/GST-LED AND771GST/GST-LED AND721GST/GST-LED AND591GST/GST-LED AND791GST/GST-LED 16 characters x 1 line 16 characters x 2 lines 16 characters x 2 lines 16 characters x 2 lines 20 characters x 2 lines 16 characters x 4 lines 24 characters x 2 lines 20 characters x 4 lines 40 characters x 2 lines 40 characters x 4 lines Terminal Characteristics Input Terminal E Input Terminals RS, R/W

Terminal Characteristics I/O Terminals DB0 to DB7

Connector Pin Assignments (except for AND791GST) Pin No. Signal Function 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15* 16* GND VDD VO RS R/W E DBO DB1 DB2 DB3 DB4 DB5 DB6 DB7 LED LED LED Anode (For LED option) LED Cathode (For LED option) Data Bus DB0-DB7 is for 8 bit operation Ground +5 Power Supply LCD Drive Voltage H Data Input L Command Input Read/Write Enable When input is at the intermediate level with CMOS, excessive current ows through the input circuit to the power supply. To avoid this, input level must be xed at high or low.

* See specic mechanical drawing for details.

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

12/17/99

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

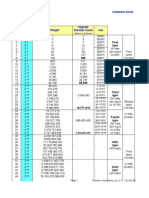

Character Position and Character Address

For each device, the relationship between character position and character address is straightforward. A hexadecimal code for each character position in each device is given in the following charts. Character positions are numbered from left to right beginning in the top left corner as you view the device from the front. AND671

Character Position DD RAM (Hex) Add. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 00 01 02 03 04 05 06 07 40 41 42 43 44 45 46 47

AND491, 481, 471

Character Position DD RAM (Hex) Add. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Character Position 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F DD RAM (Hex) Add. 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F

AND501

Character Position DD RAM (Hex) Add. Character Position DD RAM (Hex) Add. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53

AND731

Character Position 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 Character Position 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 DD RAM (Hex) Add. 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F Character Position 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 DD RAM (Hex) Add. 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F Character Position 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64

DD RAM (Hex) Add. 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F

DD RAM (Hex) Add. 50 51 52 53 54 55 56 57 58 59 5A 5B 5C 5D 5E 5F

AND771

Character Position DD RAM (Hex) Add. Character Position DD RAM (Hex) Add. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 14 15 16 17 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 41 42 43 44 45 46 47 48 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57

AND591

Character Position 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 DD RAM (Hex) Add. 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0E 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 Character Position 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80

DD RAM (Hex) Add. 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57 58 59 5A 5B 5C 5D 5E 5F 60 61 62 63 64 65 66 67

AND721

Character Position DD RAM (Hex) Add. Character Position DD RAM (Hex) Add. Character Position DD RAM (Hex) Add. Character Position DD RAM (Hex) Add. 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0F 10 11 12 13 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80 54 55 56 57 58 59 5A 5B 5C 5D 5E 5F 60 6 62 63 64 65 66 67

AND791

Character Position 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40 DD RAM (Hex) Add. 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0E 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 Character Position 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80

DD RAM (Hex) Add. 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57 58 59 5A 5B 5C 5D 5E 5F 60 61 62 63 64 65 66 67 Character Position 1 2 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 32 33 34 35 36 37 38 39 40

DD RAM (Hex) Add. 00 01 02 03 04 05 06 07 08 09 0A 0B 0C 0D 0E 0E 10 11 12 13 14 15 16 17 18 19 1A 1B 1C 1D 1E 1F 20 21 22 23 24 25 26 27 Character Position 41 42 43 44 45 46 47 48 49 50 51 52 53 54 55 56 57 58 59 60 61 62 63 64 65 66 67 68 69 70 71 72 73 74 75 76 77 78 79 80

DD RAM (Hex) Add. 40 41 42 43 44 45 46 47 48 49 4A 4B 4C 4D 4E 4F 50 51 52 53 54 55 56 57 58 59 5A 5B 5C 5D 5E 5F 60 61 62 63 64 65 66 67

Note: Address locations for Lines 1 & 2 are controlled by E1, and lines 3 & 4 are controlled by E2.

12/17/99

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Timing

Timing Characteristics (Data Read)

Timing Characteristics (TA = 25C) Data Write Value Item Symbol Min. Max Enable Cycle Time Enable Pulse Width Enable Rise/Fall Time Set Up Time Address Hold Time Data Set Up Time Data Hold Time Data Read Item Enable Cycle Time Enable Pulse Width Enable Rise/Fall Time Set Up Time Address Hold Time Data Delay Time Data Hold Time Symbol tCYCE PWEH tEr, tEf tAS tAH tDDR tDHR 20 140 10 320 Value Min. 1000 450 25 Max. tCYCE PWEH tEr, tEf tAS tAH tDSW tH 140 10 195 10 1000 450 25 -

Unit

ns

Data Transfer Example

Data can be sent in the either two cycles of 4-bit data or one cycle of 8-bit data, a scheme that suits 4-bit or 8-bit CPUs. Data that is 8-bits long is transferred using 8 data lines of DB0 to DB7. 8-Bit Data Transfer Example

Unit

ns

Timing Characteristics (Data Write)

Data that is 4 bits long is transferred by using only 4 lines of DB7 to DB4DB3 to DB0 are not used. Data transfer between the module and a 4-bit CPU is completed when the high order 4 bits are transferred rst, followed by the low order 4 bits. 4-Bit Data Transfer Example

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

12/17/99

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Command List Command Code Command Clear display(3) RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 0 0 0 0 0 0 0 0 0 1 Description Clear display and return cursor to home position (Address 0). Return cursor to home position (Address 0). Also return display being shifted to original position. DD RAM contents remain the same. Set cursor move direction and specify whether to shift display. These operations are performed during data write. Set ON/OFF of entire display (D), dresser ON/OFF (C), and blinking of cursor position B Move cursor and shift display without changing DD RAM contents. Set interface data length (DL) number of display lines (L) and character font (F). Set CG RAM address, CG RAM data is sent and received after this setting. Set DD RAM address. DD RAM data is sent and received after this setting. Read Busy ag (BF) indicating internal operation is being performed and reads address counter contents. Write Data from DD RAM or CG RAM. Read Data from DD RAM or CG RAM. Execution Time (Max.)(1) 1.64ms Execution Time (Max.)(2) 4.9ms

Return Home

1.64ms

4.8ms

Entry Mode Set

I/D

40s

120s

Display ON/OFF Control Cursor and Display Shift(4) Function Set Set RAM Address Set DD RAM Address Read Busy Flag & Address Write Data to CG or DD RAM Read Data to CG or DD RAM

40s

120s

0 0 0 0

0 0 0 0

0 0 0 1

0 0 1

0 1

1 DL

S/C R/L N ACG ADD F

X X

X X

40s 40s 40s 40s

120s 120s 120s 120s

BF

AC

40s

120s

1 1

0 1

Write Data Read Data : Increment I/D = 0 Decrement : Accompanies display shift : Display shift S/C = 0 Cursor move : Shift to the right : Shift to the left : 8 bits DL = 0: 4 bits : 2 lines N = 0: 1 line : 5 x 10 dots F = 0: 5 x 7 dots : Internally operating : Can accept instruction

40s 40s

120s 120s

I/D = 1 S=1 S/C = 1 R/L = 1 R/L = 0 DL = 1 N =1 F=1 BF = 1 BF = 0

X = Don't Care

DD RAM CG RAM ACG ADD AC

: Display Data RAM : Character Gen RAM : CG RAM Address : DD RAM Address corresponds to Cursor Address : Address Counter used for DD and CG RAM Address.

Notes: 1. Applies to AND491, AND481, AND491, and AND501. 2. Applies to AND591, AND731, AND721, AND771. 3. The repeat time interval of command Clear Display must be 13ms minimum (5 x 7 dot font) and 18ms minimum (5 x 10 dot font). 4. Commands Cursor and Display Shift are invalid for the AND671.

12/17/99

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Function of Registers

The following paragraphs describe the function of the registers.

Instruction Register and Data Register Display Data RAM (DD RAM)

The built-in controller has two 8-bit registers, an Instruction Register (IR) and a Data Register (DR). The IR stores commands such as display clear and cursor shift, or address information of display data RAM (DD RAM), and character generator RAM (CG RAM). The IR can be written to by a CPU, but a CPU cannot read this register. The DR temporarily stores data to be written into the DD RAM or the CG RAM. Data written into the DR is automatically sent to the DD RAM or the CG RAM as an internal operation. The DR is also used for data storage when reading data from the DD RAM or the CG RAM. When address information is written into the IR, data is transferred to the DR from the DD RAM or the CG RAM as an internal operation. Then, the CPU reads the DR and data transfer is completed. After the CPU reads the DR, data of the DD RAM or the CG RAM at the next address is sent to DR for the next reading. Register Selector (RS) signals select these two registers. Register Selection RS R/W Operation 0 0

Write commands to IR. Read of a Busy Flag (DB7) and Address Counter (DBO to DB6) DR Write as internal operations (DR DD or CG RAM) DR Read as internal operations (DD or CG RAM DR)

The display data RAM (DD RAM) stores display data represented in 8-bit character codes. The relationship between the DD RAM address and display position on the LCD Display is described by a series of tables under the paragraph Character Position and Character Address on page 3 of this section.

Commands

The command code is the signal through which the LCD module is accessed through the CPU. The LCD module begins operation upon receipt of the code input. Because the internal processing operation of the LCD module is started with a timing that does not affect the LCD display, the busy status continues longer than the CPU cycle time. Under the busy status (when the busy ag is set to 1), the LCD module does not execute any commands other than the busy ag read. Accordingly, the CPU has to verify that the busy ag is set to 0 prior to the input of the command code. Clear Display RS Code 0 R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 0 0 0 0 0 0 0 0 1

Enable (E)

Write space code 20 (hexadecimal) into all the DD RAM addresses. The cursor returns to address 0 (DD RAM Address = 00H) and the display, if it has been shifted, returns to the original position. In other words, the display disappears and the cursor goes to the left edge of the rst line. Return Home RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 0 0 0 0 0 0 0 0 1 X

Busy Flag (BF)

Return the cursor to character position 1 (DD RAM Address = 00H) and returns the display to the original position if it has been shifted (S in the instruction register is 1). The DD RAM contents remain unchanged. X = Dont care Entry Mode Set RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code I/D: 0 0 0 0 0 0 0 1 I/D S

When the Busy Flag is 1, the LCD module is in the internal operation mode, and the next instruction is not accepted at this time. As shown in the Command List on page 5 of this section, the Busy Flag is shown in DB7 when RS = 0 and R/ W = 1. The next instruction must be written after checking that the Busy Flag is 0.

Address Counter (AC)

The address counter (AC) assigns DD and CG RAM address. When an instruction for address setting is written in IR, the address information is sent from IR to AC. Selection of either the DD or CG RAM is also determined by an instruction. After writing into (or reading from) DD or CG RAM display data, AC is automatically incremented by 1 (or decremented by 1). Data in address counters (AC) are in DB6 to DBO when RS = 0 and R/W = 1, as shown in the table entitled Command List on page 5 of this section. S:

Increment (I/D = 1) or decrement (I/D = 0) the DD RAM address by one upon writing a character code into the DD RAM or reading a character code from the DD RAM. The cursor moves to the right when I/D = 1, and to the left when I/D = 0. When writing to the DD RAM, shift the entire display to the right (when l/D = 0, S = 1) or to the left (when ID = 1, S = 1). Therefore, the cursor looks as if it stood still and only the display moves. Display is not shifted when reading from the DD RAM. Display is not shifted when S = 0.

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

12/17/99

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Display ON/OFF Control RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code D: 0 0 0 0 0 0 1 D C B Module Type Number No. of Character N F Display Font Lines

Duty Ratio

AND Model No. AND471, AND481, AND491, AND501, AND591, AND671, AND771 AND721, AND731, AND791

Display is turned ON when D = 1 and OFF when D = 0. When display is turned off due to D = 0, the display data remains in the DD RAM and they can be displayed immediately by setting D = 1. The cursor is displayed when C = 1 and not displayed when C = 0. Even if the cursor disappears, the function of I/D does not change during display data write. The cursor is displayed at the 8th line when the 5 x 7 dots character font is selected. The character at the cursor position blinks when B = 1. The blink is done by switching between all black dots and display characters at 0.4 second interval. The cursor and the blink can be set concurrently.

5 x 7 Dots

1/16

C:

5 x 7 Dots

1/16

Set CG RAM Address RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 0 0 0 1 A A A A A A

B:

Cursor or Display Shift RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 0 0 0 0 0 1 S/C R/L X X

Set the CG RAM address to a binary number of AAAAAA in the address counter. After execution of this instruction, all the data from MPU is written into the CG RAM and all the data is read from CG RAM. Set DD RAM Address RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 0 0 1 An A A A A A A

Shift the cursor position or display position to the right or the left without writing or reading the display data. This function can be used for correction or search of display. S/C 0 0 1 1 R/L 0 1 0 1 Function Shift the cursor position to the left. (AC is decremented by one.) Shift the cursor position to the right. (AC is incremented by one.) Shift the entire display to the left. The cursor follows the display shift. Shift the entire display to the right. The Cursor follows the display shift.

Set the DD RAM address to a binary number of AnAAAAAA in the address counter (An = 0 for the rst line, An = 1 for the second line). After execution of this instruction, all the data from MPU is written into the DD RAM and all the data is read from DD RAM. Read Busy Flag and Address RS R/W DB7 DB6 DB5 DB4 DB3 DB2 091 DB0 Code 0 1 BF A A A A A A A

Function Set RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code DL: 0 0 0 0 1 DL N F X X

Read Busy Flag (BF) and the value of the address counter (AAAAAAA). The condition BF = 1 indicates that an internal operation is going on and the next command is not accepted until BF becomes 0. You must check the BF status before the next write operation. The address counter generates the CG or DD RAM address. Write Data to CG RAM or DD RAM RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 1 D D D D D D D D D

Sets the interface data length. Data is sent or received in 8-bit length (DB7 to DB0) when DL = 1 and 4-bit length (DB7 to DB4) when DL = 0. When 4bit length is selected, data must be sent or received in two cycles. Set number of display lines. Set character font. The 5 x 7 dots character font is selected when F = 0. While 5 x 10 dots character font is selected when F = 1 and N = 0.

N: F:

Write binary 8-bit data DDDDDDDD to the CG RAM or the DD RAM. Whether the CG RAM or the DD RAM is to be written is determined by the previous designation (CG RAM address setting or DD RAM address setting). After writing, the address is automatically incremented or decremented by one according to entry mode. Display shift also follows the entry mode.

12/17/99

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Read Data from CG RAM or DD RAM RS R/W DB7 DB6 DB5 DB4 DB3 DB2 DB1 DB0 Code 1 1 D D D D D D D D 5 x 7 Dots Character Pattern CG RAM Character Code Address (DD RAM Data) 7 6 5 4 3 2 1 0 5 4 3 2 1 0 0 0 0 0 1 0 0 0 0 X 0 0 0 0 0 0 0 1 1 0 1 0 1 1 1 1 0 0 0 0 0 1 0 0 0 0 X 0 0 1 0 0 1 0 1 1 0 1 0 1 1 1 1 X = Don't care Notes: 1. 2. Character code bits 0 to 2 correspond to CG RAM address bits 3 to 5 (3 bits: 8 types). CG RAM address bits 0 to 2 designate character pattern line position. The 8th line is the cursor position and the display is presented in logical OR with cursor. Character pattern row positions correspond to CG RAM data bits 0 to 4, as shown in the gure (bit 4 is at the left end). Since the CG RAM data bits 5 to 7 are not used for the display, they can be used as general data RAM. As shown in the above table CG RAM character patterns are selected when character code bits 4 to 7 are all 0. However, since character code bit 3 is the Don't care bit, the display in the character pattern, for example, is selected by character code 00 or 08. A 1 for CG RAM data corresponds to selection for display and a 0 for non-selection.

Read binary 8-bit data DDDDDDDD from the CG RAM or the DD RAM. Whether the CG RAM or the DD RAM is to be read is determined by the previous designation. Prior to inputting this read command, either the CG RAM address set command or the DD RAM address set command must be executed. If it is not done, the rst data read is invalid, and the second data read of the next address can be read normally. After reading, the address is automatically incremented or decremented by one according to the entry mode. However, display shift is not performed regardless of entry mode.

Character Patterns and Character Codes

The relationship between character patterns and character codes is explained in the following paragraphs.

Character Generator ROM (CG ROM)

0 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1

Character Pattern (CG RAM Data) 7 6 5 4 3 2 1 0 XXX 0 0 0 0 0 XXX 0 0 0 0 0 XXX 0 1 0 0 1 XXX 1 0 1 0 1 XXX 1 0 0 1 0 XXX 1 0 0 1 0 XXX 0 1 1 0 1 XXX 0 0 0 0 0 XXX 0 0 0 0 0 XXX 0 0 0 0 0 XXX 0 1 1 1 0 XXX 1 0 0 0 1 XXX 1 0 0 0 1 XXX 0 1 0 1 0 XXX 1 1 0 1 1 XXX 0 0 0 0 0

The character generator ROM generates 5 x 7 dot (160 kinds) character patterns or 5 x 10 dot (32 kinds) character patterns from an 8-bit DD RAM character code signal. When the 8-bit character code of the CG ROM is written into the DD RAM, the character pattern of the CG ROM corresponding to the code is displayed on the LCD display position corresponding to the DD RAM address. The table entitled Character Pattern and Character Code on page 9 of this section shows the relation between character patterns and character codes. Note: AND671, AND471, AND481, AND491, AND501, AND591, AND771, AND731, AND721 and AND791 can only use 5 x 7 dot character patterns.

Character Generator RAM (CG RAM)

3.

4.

The character generator RAM is used for original character patterns other than for the CG ROM. The CG RAM has the capacity (64 bytes = 512 bits) to write 8 types of character patterns with 5x7 font, and 4 types with S x 10 font. When displaying character patterns stored in the CG RAM, write 8-bit character codes (00 to 07 or 02 to OF; hex.) on the left side as shown in the table entitled Character Pattern and Character Code on page 9 of this section. The table entitled 5 x 7 Dots Character Pattern on page 8 of this section shows the relation between CG RAM addresses and data and display patterns for 5 x 7 dots.

Address, Character Code, and Character Pattern

5.

The following tables list the relationships between CG RAM address, character code (DD RAM), and character pattern (CG RAM) for two character patterns.

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

12/17/99

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Character Pattern and Character Code

12/17/99

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Initialization (Reset)

The following paragraphs describe initialization stepts.

Automatic Initialization

The LCD module is automatically initialized when power is turned on (using internal reset circuit). The following commands are executed during initialization. The busy ag is kept in the busy state (BF does not equal 1) until initialization ends. The busy state is kept about 10ms after VDD level reaches 4.5V. 1. 2. Clear display Function set: Data length of interface with MPU: 8-bit (DL-1) LCD: 1-line display (N = 0) Character font: 5 x 7 dots (F = 0) Display ON/OFF control: Display: Display OFF (0 = 0) Cursor: Cursor OFF (C = 0) Blink: Blink OFF (B = 0) Entry mode set: Address counter: Increment + 1 (I/D = 1) Display shift: No shift (S = 0) DD RAM is selected: The function set command in automatic initialization does not always meet the conguration of each module, in this case your program must reset the Function Set command. (Refer to Function Set on page 7 of this section.)

3.

4.

5.

Note: Power-on timing is necessary to perform automatic initialization. When the above power supply condition is not satised, the internal reset circuit will not operate normally. In this case, perform the initialization by sending commands from the CPU after turning power to ON. Power-On Timing

10

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

12/17/99

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Manual Initialization Procedure

The following diagram applies when the interface data length is 4-bits.

Power ON Since VDD reaches more than 4.5V wait more than 15ms 1 RS 0 R/W 0 DB7 0 DB6 0 DB5 1 DB4 1 Function Set (Interface data length is 8-bit)

Wait more than 4.1 s Function Set (Interface data length is 8-bit)

RS 0

R/W 0

DB7 0

DB6 0

DB5 1

DB4 1

Wait more than 100 s RS 0 RS X 0 0 0 0 0 0 0 0 0 R/W 0 R/W X 0 0 0 0 0 0 0 0 0 DB7 0 DB7 DB3 0 0 N 0 1 0 0 0 0 DB6 0 DB6 DB2 0 0 F 0 0 0 0 0 1 DB5 1 DB5 DB1 1 1 X 0 0 0 0 0 I/D DB4 0 DB4 DB0 0 0 X 0 0 0 1 0 S Function Set (Interface data length is 8-bit)

Function Set (Set interface data length. Set 4-bit) Function Set Display ON Display Clear Entry Mode Set

Initialization End X = Don't care Notes: 1. Before initialize step 1, 2, and 3, cannot check busy ag. 2. After initialize step 4, cannot change function set mode, number of display lines and character font.

12/17/99

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

11

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Manual Initialization Procedure (Continued)

The following diagram applies when the interface data length is 8-bit.

Power ON Since VDD reaches more than 4.5V wait more than 15ms 1 RS 0 R/W 0 DB7 0 DB6 0 DB5 1 DB4 1 DB3 1 DB2 X DB1 X DB0 X Function Set (Interface data length is 8-bit)

Wait more than 4.1 s Function Set (Interface data length is 8-bit)

RS 0

R/W 0

DB7 0

DB6 0

DB5 1

DB4 1

DB3 X

DB2 X

DB1 X

DB0 X

Wait more than 100 s RS 0 RS 0 0 0 0 R/W 0 R/W 0 0 0 0 DB7 0 DB7 0 0 0 0 DB6 0 DB6 0 0 0 0 DB5 1 DB5 1 0 0 0 DB4 1 DB4 1 0 0 0 DB3 X DB3 N 1 0 0 DB2 X DB2 F 1 0 1 DB1 X DB1 X 0 0 I/D DB0 X DB0 X 0 1 S Function Set (Interface data length is 8-bit)

Function Set Display ON Display Clear Entry Mode Set

Initialization End X = Don't care Notes: (1) Before initialize step 1, 2 and 3, cannot check busy ag. (2) After initialize step 4, cannot change function set, number of display lines and character font.

12

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

12/17/99

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

Example of Operation (AND501)

4-Bit Operation Command Power Supply ON (Internal Reset Circuit) Initialization Display ON/OFF Control

RS 0 0 0 0 1 1 R/W DB7 0 0 0 0 0 0 0 0 1 0 0 0 DB6 0 1 0 0 1 0 DB5 0 1 0 0 0 0 DB4 0 0 0 0 0 1

Display

Operation Initialized. No display appears. Initialized. No display appears. Turn on display and cursor. All display is in space mode because of initialization.

Set DD RAM Address A__

Set RAM address so that the cursor is positioned at the head of rst line. Write A. The DD RAM was selected by the initialization performed when power was turned on. The cursor increments by one and shifts to the right.

Write Data to CG/DD RAM

8-Bit Operation Command Power Supply ON (Internal Reset Circuit) Initialization Display ON/OFF Control

RS 0 0 R/W 0 0 DB7 0 1 DB6 0 0 DB5 0 0 DB4 0 0 DB3 1 0 DB2 1 0 DB1 1 0 DB0 0 0

Display

Operation Initialized. No display appears. Initialized. No display appears. Turn on display and cursor. All display is in space mode because of initialization. Set RAM address so that the cursor is positioned at the head of rst line. Write A. The DD RAM was selected by the initialization performed when power was turned on. The cursor increments by one and shifts to the right. Write N Write D Set RAM address so cursor is positioned at the head of second line. Write A Write AND 501 20 x Write 2

Set DD RAM Address Write Data to CG/DD RAM

1 0 0 1 0 0 | | 0 0 0 1

A__

Write Data to CG/DD RAM

1 0 1 0 0 0 0 1 0 1 1 1 0 0 0 0 0 0 | | 1 0 0 0 0 1 0 0 0 0 0 0 0 1

AND__ AND __ AND A__

Set DD RAM Address Write Data to CG/DD RAM

Write Data to CG/DD RAM

1 0 0 0 0 0 0 0 1 0 0 0 0 1 1 1 0 1

Entry Mode Set | | Return Home

0 0 0 0 0 0 0 0 1 X

AND AND501 20 x 2 AND Set mode for display shift at the time of write. AND501 20 x 2 Written data moves to the right, cursor on position 2_ AND501 20x2 Return both the display and cursor to the original position.

X = Don't care

12/17/99

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

13

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

HD44780 Electrical Interfaces

6800 8085

688 with 6821 PIA Z80

8080

14

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

12/17/99

www.purdyelectronics.com

Intelligent Alphanumeric Application Notes

DMM Connected to an 8085A Based System

12/17/99

Purdy Electronics Corporation 720 Palomar Avenue Sunnyvale, CA 94086 Tel: 408.523.8200 Fax: 408.733.1287 email@purdyelectronics.com

15

www.purdyelectronics.com

Anda mungkin juga menyukai

- HD44780U (LCD-II) : (Dot Matrix Liquid Crystal Display Controller/Driver)Dokumen59 halamanHD44780U (LCD-II) : (Dot Matrix Liquid Crystal Display Controller/Driver)Alexander Du PlessisBelum ada peringkat

- Char CommDokumen8 halamanChar CommfhidipBelum ada peringkat

- LCD Data SheetDokumen2 halamanLCD Data SheetGonzalo BojalilBelum ada peringkat

- Drive LCD - Ks0066uDokumen34 halamanDrive LCD - Ks0066uJose SilvaBelum ada peringkat

- Ecdis ManualDokumen223 halamanEcdis ManualVinko Radović67% (3)

- Hitachi LCD Driver HD44780U WithnotesDokumen60 halamanHitachi LCD Driver HD44780U Withnotesepc_kiranBelum ada peringkat

- AESDokumen46 halamanAESDhaval DoshiBelum ada peringkat

- ST7066UDokumen42 halamanST7066UConIntBelum ada peringkat

- Aspect RatioDokumen2 halamanAspect Ratio"Forced" Unlimited DownloadsBelum ada peringkat

- STP Con Packet TracerDokumen6 halamanSTP Con Packet TracerRodrigo VelazquezBelum ada peringkat

- ST7920Dokumen49 halamanST7920jmcs87100% (2)

- Winstar Display DatasheetDokumen20 halamanWinstar Display DatasheetAlejandroBelum ada peringkat

- HJ1602A DatasheetDokumen11 halamanHJ1602A DatasheetsunthomaBelum ada peringkat

- LCD 2x16 Spec-29045Dokumen30 halamanLCD 2x16 Spec-29045kerblaBelum ada peringkat

- Cimon Loader ProdocolDokumen8 halamanCimon Loader ProdocolMurat ErkanBelum ada peringkat

- Lat-Long Coordinate PlottingDokumen16 halamanLat-Long Coordinate Plottinggoon77Belum ada peringkat

- Schematics PDFDokumen7 halamanSchematics PDFCristian GonzalezBelum ada peringkat

- Rc2004a Biw EsxDokumen27 halamanRc2004a Biw EsxUjio37Belum ada peringkat

- Interfacing LCD With MB90F387SDokumen40 halamanInterfacing LCD With MB90F387SMark VillamorBelum ada peringkat

- XbeDokumen7 halamanXbeRosalio Gonzalez palominoBelum ada peringkat

- Weh002004alpp5n PDFDokumen63 halamanWeh002004alpp5n PDFMartin MuszioBelum ada peringkat

- MSI LabDokumen7 halamanMSI LabMirza Riyasat AliBelum ada peringkat

- Book 2Dokumen24 halamanBook 2LiNuBelum ada peringkat

- ManualDokumen532 halamanManualosuwiraBelum ada peringkat

- Debug ReferenceDokumen13 halamanDebug ReferenceAayush Kumar DubeyBelum ada peringkat

- Manual of Compatibility Gps Trackmaker® - Mapdekode: Odilon Ferreira Junior Belo Horizonte - Brazil Apr - 2003Dokumen15 halamanManual of Compatibility Gps Trackmaker® - Mapdekode: Odilon Ferreira Junior Belo Horizonte - Brazil Apr - 2003Julay RamirezBelum ada peringkat

- Mazidi Solution Sol0 - 4Dokumen23 halamanMazidi Solution Sol0 - 4wahajuddinahmedBelum ada peringkat

- MS-DOS Debug CommandsDokumen8 halamanMS-DOS Debug CommandsPatrick PayosBelum ada peringkat

- EpsDokumen6 halamanEpsJoselee Ramos TitoBelum ada peringkat

- 8085 RefDokumen2 halaman8085 RefBiggRangerBelum ada peringkat

- WH1602W Tmi JTDokumen29 halamanWH1602W Tmi JTscribe72Belum ada peringkat

- Datasheet Raystar Rc1602b BperW ESXDokumen28 halamanDatasheet Raystar Rc1602b BperW ESXdtldokiBelum ada peringkat

- Pinout Ide AtaDokumen4 halamanPinout Ide AtafrewellBelum ada peringkat

- Wh1601a Yyh JT#Dokumen29 halamanWh1601a Yyh JT#genaroBelum ada peringkat

- 12864LCD Datasheet PDFDokumen42 halaman12864LCD Datasheet PDFmasterpiano36Belum ada peringkat

- Mazda Panasonic Cn-Vm4360a Service ManualDokumen43 halamanMazda Panasonic Cn-Vm4360a Service ManualElijah ChristensenBelum ada peringkat

- ECE2030 Introduction To Computer Engineering Lecture 17: Memory and Programmable LogicDokumen37 halamanECE2030 Introduction To Computer Engineering Lecture 17: Memory and Programmable Logicah chongBelum ada peringkat

- HD61830 PDFDokumen43 halamanHD61830 PDFAnonymous x78Ua6JXBelum ada peringkat

- 05 NonpipelinedDokumen29 halaman05 NonpipelinedMunesh MeenaBelum ada peringkat

- 6 TableDokumen8 halaman6 Tableafrazk8717Belum ada peringkat

- MC AddressDokumen3 halamanMC AddressUtkarsh KumarBelum ada peringkat

- LMC-SSC2E16-01 Serial: User ManualDokumen12 halamanLMC-SSC2E16-01 Serial: User ManualFred ShihBelum ada peringkat

- Assembler Design Options: Department of Computer Science National Tsing Hua UniversityDokumen27 halamanAssembler Design Options: Department of Computer Science National Tsing Hua UniversityReshma100% (1)

- Specification: ModelDokumen25 halamanSpecification: ModelMohamed KamalBelum ada peringkat

- PacketReading PDFDokumen36 halamanPacketReading PDFHong TH100% (1)

- Powers of 2Dokumen2 halamanPowers of 2gloomygeeksBelum ada peringkat

- System Software Unit-IIDokumen21 halamanSystem Software Unit-IIpalanichelvam90% (10)

- UNIT II System SoftwareDokumen11 halamanUNIT II System SoftwareArulmozhi ManoharanBelum ada peringkat

- LCD 4 Bit InterfacingDokumen6 halamanLCD 4 Bit InterfacingYogesh Hardiya100% (1)

- LMC S4a20Dokumen2 halamanLMC S4a20pareshmehta48Belum ada peringkat

- Chapter 12Dokumen5 halamanChapter 12Saad LatifBelum ada peringkat

- Honda CQ Eh8160akDokumen37 halamanHonda CQ Eh8160aklondon335Belum ada peringkat

- 4GB Registered DDR2 SDRAM DIMM: EBE41AE4ACFA (512M Words 72 Bits, 2 Ranks)Dokumen27 halaman4GB Registered DDR2 SDRAM DIMM: EBE41AE4ACFA (512M Words 72 Bits, 2 Ranks)ramgopalreddykBelum ada peringkat

- MIPS Green SheetDokumen2 halamanMIPS Green SheetjasontgameBelum ada peringkat

- Windows 7 Desktop Support and Administration: Real World Skills for MCITP Certification and Beyond (Exams 70-685 and 70-686)Dari EverandWindows 7 Desktop Support and Administration: Real World Skills for MCITP Certification and Beyond (Exams 70-685 and 70-686)Belum ada peringkat

- Advanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionDari EverandAdvanced Chipless RFID: MIMO-Based Imaging at 60 GHz - ML DetectionBelum ada peringkat

- Software Development for Engineers: C/C++, Pascal, Assembly, Visual Basic, HTML, Java Script, Java DOS, Windows NT, UNIXDari EverandSoftware Development for Engineers: C/C++, Pascal, Assembly, Visual Basic, HTML, Java Script, Java DOS, Windows NT, UNIXPenilaian: 5 dari 5 bintang5/5 (1)

- Teach Yourself the Basics of Aspen PlusDari EverandTeach Yourself the Basics of Aspen PlusPenilaian: 4 dari 5 bintang4/5 (1)

- Syllabus-Industrial Training-2022Dokumen6 halamanSyllabus-Industrial Training-2022Md Tashhirul IslamBelum ada peringkat

- Errores HitachiDokumen4 halamanErrores HitachiToni Pérez Lago50% (2)

- ResumeDokumen3 halamanResumeapi-287627349Belum ada peringkat

- Figurative LanguageDokumen32 halamanFigurative LanguageMichelle Lee100% (1)

- English 9: Finding Other's GreatnessDokumen14 halamanEnglish 9: Finding Other's GreatnessRianne Monica MasangkayBelum ada peringkat

- The Effectiveness of Teaching Writing To The Students With The Technique Rewards and Positive ReinforcementDokumen4 halamanThe Effectiveness of Teaching Writing To The Students With The Technique Rewards and Positive ReinforcementJENNIFER EMBATBelum ada peringkat

- Change Statements Into Questions Ex 2Dokumen2 halamanChange Statements Into Questions Ex 2Nur Adzrini100% (1)

- The Prize Poem - Full Text - CompressedDokumen6 halamanThe Prize Poem - Full Text - CompressedINFINTRIC BEATSBelum ada peringkat

- Sarva Vedanta Siddhanta Sara Sangraha (Commentary by Swami Paramarthananda)Dokumen318 halamanSarva Vedanta Siddhanta Sara Sangraha (Commentary by Swami Paramarthananda)dhvanibaniBelum ada peringkat

- Soal EA 8 Grade PATDokumen2 halamanSoal EA 8 Grade PATPrayogie ShandityaBelum ada peringkat

- Computer MCQ Part-02 EngDokumen72 halamanComputer MCQ Part-02 Engnirmalkumargaurav96305Belum ada peringkat

- The One Where Joey Speaks FrenchDokumen3 halamanThe One Where Joey Speaks FrenchLa Spera OttavaBelum ada peringkat

- Giesecke, Kay - 3-D Apraxic Therapy For KidsDokumen6 halamanGiesecke, Kay - 3-D Apraxic Therapy For KidsampiccaBelum ada peringkat

- Mood Classification of Hindi Songs Based On Lyrics: December 2015Dokumen8 halamanMood Classification of Hindi Songs Based On Lyrics: December 2015lalit kashyapBelum ada peringkat

- Annotation Template For Teacher I-III (Proficient Teachers Objectives Means of Verification (MOV) Description of The MOV Presented AnnotationsDokumen5 halamanAnnotation Template For Teacher I-III (Proficient Teachers Objectives Means of Verification (MOV) Description of The MOV Presented AnnotationsJeffy P. UrbinaBelum ada peringkat

- Love's Labour's LostDokumen248 halamanLove's Labour's LostteearrBelum ada peringkat

- Cyril Mango, Antique Statuary and The Byzantine BeholderDokumen29 halamanCyril Mango, Antique Statuary and The Byzantine BeholderDaniel LBelum ada peringkat

- Proba Scrisa - Model 1Dokumen2 halamanProba Scrisa - Model 1maria savuBelum ada peringkat

- Soal UTS Kelas 6 Bahasa InggrisDokumen3 halamanSoal UTS Kelas 6 Bahasa InggrisAljody PahleviBelum ada peringkat

- 17D38101 Error Control CodingDokumen1 halaman17D38101 Error Control CodingSreekanth PagadapalliBelum ada peringkat

- Lab 5 Motorola 68000Dokumen12 halamanLab 5 Motorola 68000Ayozzet WefBelum ada peringkat

- Contoh ProposalDokumen44 halamanContoh ProposalHendra Umar Al Faruq100% (1)

- Plane Figures Mfe 2 2021 2022Dokumen70 halamanPlane Figures Mfe 2 2021 2022Aaliyah Jean BelenBelum ada peringkat

- Limbo OverviewDokumen7 halamanLimbo OverviewWilfred SpringerBelum ada peringkat

- Ibn Taymiyyah Jesus Divinity ArgumentDokumen4 halamanIbn Taymiyyah Jesus Divinity ArgumentLarbi MegrousBelum ada peringkat

- List of Papyrus Found NewDokumen4 halamanList of Papyrus Found NewiSundae17Belum ada peringkat

- Tests Types - StepsDokumen22 halamanTests Types - Stepsapi-462294949Belum ada peringkat

- How To Describe A PictureDokumen1 halamanHow To Describe A PictureJoy KruseBelum ada peringkat

- Computerwise TransTerm 6/6A/6B User's ManualDokumen45 halamanComputerwise TransTerm 6/6A/6B User's ManualAnonymous W4lIopJh3Belum ada peringkat

- RPH Latest Exam Oriented 8QDokumen2 halamanRPH Latest Exam Oriented 8QFaryz Tontok Tinan 오빠Belum ada peringkat