Capitulo9. Convertidor Analogo Digital Del ATmega32 (Español)

Diunggah oleh

FortinoJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Capitulo9. Convertidor Analogo Digital Del ATmega32 (Español)

Diunggah oleh

FortinoHak Cipta:

Format Tersedia

__________________________________________________________________________ITSP

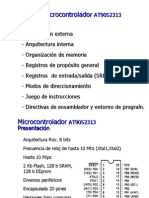

CONVERTIDOR ANALÓGICO DIGITAL del AVR

9.1 INTRODUCCIÓN

Características del Convertidor Analógico Digital:

• 10 bits de resolución.

• 0.5 LSB No lineal.

• ±2 LSB Precisión absoluta.

• 13 a 260µs de Tiempo de Conversión.

• Hasta 15,000 Muestras por segundo en su Máxima Resolución.

• 8 Canales de Entrada Multiplexados a una sola Terminación.

• 7 Canales de entrada diferenciales.

• Rango de Voltaje de Entrada de 0 a Vcc.

• Voltaje de referencia seleccionable a 2.56V.

• Modo de conversión única o libre.

• Inicio de Conversión del ADC por Auto disparo con fuente de interrupción.

• Interrupción de Conversión Completa del ADC.

• Cancelador de Ruido en Modo Sleep.

El Convertidor Analógico Digital del ATmega32 es por Aproximaciones Sucesivas con

una resolución de 10 bits. El ADC se conecta a un multiplexor de 8 canales análogos el

cual permite 8 voltajes de entrada en una sola terminación construido en los pines del

puerto A. El voltaje de entrada de una sola terminación se refiere a 0 V (GND).

El dispositivo también soporta 16 combinaciones de voltajes de entrada diferenciales.

Dos de las entradas diferenciales (ADC1, ADC0 y ADC3, ADC2) están equipadas con

una etapa de ganancia programable, proveyendo pasos de amplificación de 0dB (1x),

20dB (10x), o 46dB (200x) en el voltaje de entrada diferencial antes de la conversión del

A/D. Siete canales de entrada diferenciales análogos comparten una terminal común

negativa (ADC1), mientras que cualquier otra entrada del ADC puede ser seleccionada

como la terminal positiva de entrada. Si se usa una ganancia de 1x o 10x, una

resolución de 8 bits se espera. Si se usa una ganancia de 200x, una resolución de 7

bits se espera.

El ADC contiene un circuito de Muestreo y Retención el cual asegura que el voltaje de

entrada al ADC se mantenga constante durante la conversión. El diagrama a bloques se

muestra en la siguiente figura.

El ADC tiene un pin para la fuente de voltaje separado, AVCC. El AVCC no debe diferir

más de ±0.3 V de Vcc.

Los voltajes de referencia nominales internos 2.56V de AVCC son provistos dentro del

chip. El voltaje de referencia puede ser externamente desacoplado del pin AREF por un

capacitor para un mejor desempeño de ruido.

Documento traducido de la hoja de datos del ATmega32 1

__________________________________________________________________________ITSP

Figura 1. Diagrama a bloques esquemático del Convertidor Analógico Digital.

Operación

El ADC convierte un voltaje de entrada análogo a un valor digital de 10 bits por

aproximaciones sucesivas. El mínimo valor representa a GND y el máximo valor

representa el voltaje en el pin AREF menos 1 LSB. Opcionalmente, AVCC o un voltaje

de referencia interno de 2.56V puede ser conectado al pin AREF escribiendo en los bits

Documento traducido de la hoja de datos del ATmega32 2

__________________________________________________________________________ITSP

REFs del registro ADMUX. El voltaje de referencia interno puede ser desacoplado por

un capacitor externo en el pin AREF para mejorar la inmunidad al ruido.

El canal de entrada análogo y la ganancia diferencial son seleccionados escribiendo en

los bits MUX en ADMUX. Cualquiera de los pines de entrada del ADC, así como GND y

una banda de voltaje de referencia fijo, pueden ser seleccionados como entradas

finales independientes al ADC. Una selección de los pines de entrada del ADC pueden

ser seleccionados como entradas positivas y negativas al amplificador de ganancia

diferencial.

Si los canales diferenciales son seleccionados, la etapa de ganancia diferencial

amplifica la diferencia de voltaje entre el par del canal de entrada seleccionado por el

factor de ganancia seleccionado. Este valor amplificado entonces llega a ser la entrada

análoga del ADC. Si se usan las terminaciones independientes de los canales, el

amplificador de ganancia es “bypassed” juntos.

El ADC se habilita colocando el bit de habilitación del ADC, ADEN en ADCSRA. El

voltaje de referencia y la selección del canal de entrada no tendrán efecto hasta que

ADEN se habilite. El ADC no consume potencia cuando ADEN se limpia, así es

recomendable apagar el ADC antes de que entre al modo de salvado de potencia

(sleep).

El ADC genera un resultado de 10 bits el cual se presenta en los registros de datos del

ADC, ADCH y ADCL. Por default, el resultado se presenta con ajuste a la derecha, pero

puede ser opcionalmente presentado con ajuste a la izquierda colocando el bit ADLAR

en ADMUX.

Si el resultado es ajustado a la izquierda y no más de una precisión de 8 bits se

requiere, es suficiente con leer el ADCH. De lo contrario, ADCL debe ser leído primero,

después ADCH, para asegurar que el contenido del registro de datos pertenezca a la

misma conversión. Una vez que ADCL se lea, el acceso al ADC al registro de datos se

bloquea. Esto significa que si ADCL ha sido leído, y una conversión se completa antes

de que ADCH sea leído, ni el registro es actualizado y el resultado de la conversión se

pierde. Cuando ADCH se lea, el acceso ADC a los registros de ADCH y ADCL se re-

habilita.

El ADC tiene su propia interrupción la cual puede ser disparada cuando una conversión

se completa. Cuando el ADC accede al registro de datos, se prohíbe entre la lectura de

ADCH y ADCL sea disparada la interrupción aún si el resultado se pierde.

Inicializando una Conversión

Una sola conversión es inicializada escribiendo un uno lógico en el bit de inicio de la

conversión del ADC, ADSC. Este bit permanece alto tanto como la conversión esté en

progreso y sea limpiado por hardware cuando se complete la conversión. Si un canal de

datos diferencial se selecciona mientras una conversión está en progreso, el ADC

finalizará la conversión actual antes de ejecutar el cambio de canal.

Documento traducido de la hoja de datos del ATmega32 3

__________________________________________________________________________ITSP

Alternadamente, una conversión puede ser disparada automáticamente por varias

fuentes. El auto disparo es habilitado colocando el bit de habilitación de auto disparo del

ADC, ADATE en ADCSRA. La fuente de disparo se selecciona colocando los bits de

selección de disparo del ADC, ADTS en SFIOR. Cuando un flanco positivo ocurra en la

señal de disparo seleccionada, el preescalador del ADC se reinicia y una conversión

comienza. Esto provee un método de inicio de conversión a intervalos fijos. Si la señal

de disparo aún esta puesta a uno cuando la conversión se completa, una conversión

nueva no será iniciada. Si otro flanco positivo ocurre en la señal de disparo durante la

conversión, el flanco será ignorado. Note que una bandera de interrupción será puesta

a uno, aún si la interrupción especificada esta deshabilitada o el bit de habilitación de

interrupciones globales esta limpio, SREG. Una conversión puede dispararse sin causar

una interrupción. Sin embargo, la bandera de interrupción debe ser limpiada para que

sea disparada en una nueva conversión en el próximo evento de interrupción.

Figura 2. Auto disparo lógico del ADC.

Usando la bandera de interrupción del ADC como una fuente de disparo hace que el

ADC comience una nueva conversión tan pronto como la conversión en curso finalice.

El ADC opera en modo libre, constantemente muestrea y actualiza el registro de datos

del ADC. La primera conversión debe ser iniciada escribiendo un uno lógico en el bit

ADSC en ADCSRA. En este modo el ADC ejecutará conversiones sucesivas

independientemente de la bandera de interrupción del ADC, ADIF se limpia o no.

Si el auto disparo esta habilitado, las conversiones únicas pueden ser iniciadas

escribiendo un uno en ADSC en el registro ADCSRA. ADSC también se usa para

determinar si una conversión está en progreso. El bit ADSC leerá un uno durante una

conversión, independientemente de cómo la conversión fue iniciada.

Preescalamiento y Tiempo de Conversión

Documento traducido de la hoja de datos del ATmega32 4

__________________________________________________________________________ITSP

Figura 3. Preescalador del ADC.

Por default, la circuitería de aproximaciones sucesivas requiere una frecuencia de reloj

de entrada entre 50kHz y 200kHz para obtener la máxima resolución. Si una resolución

más baja de 10 bits se requiere, la frecuencia de reloj de entrada al ADC puede ser

mayor de 200kHz para obtener una razón de muestreo mayor.

El módulo ADC contiene un preescalador, el cual genera una frecuencia de reloj

aceptable para el ADC de cualquier frecuencia del CPU arriba de 100kHz. El

preescalador se activa por los bits ADPS en ADCSRA. El preescalador inicia su cuenta

desde el momento en que el ADC se enciende colocando el bit a uno en ADEN de

ADCSRA. El preescalador se mantiene corriendo mientras el ADEN este en uno, y se

reinicia cuando ADEN este en bajo.

Cuando se inicia una sola conversión colocando el bit ADSC en ADCSRA, la conversión

inicia en la siguiente transición positiva del ciclo de reloj del ADC.

Una conversión normal toma 13 ciclos de reloj del ADC. La primera conversión después

de que el ADC se enciende (ADEN en ADCSRA se ponga a uno) toma 25 ciclos de reloj

del ADC para inicializar la circuitería analógica.

El muestreo y retención actual toma lugar 1.5 ciclos de reloj del ADC después del inicio

de una conversión normal y 13.5 ciclos de reloj del ADC después del comienzo de la

primera conversión. Cuando una conversión se completa, el resultado se escribe en el

registro de datos del ADC, y ADIF se activa. En el modo de conversión única, ADSC se

limpia simultáneamente. El software puede poner a uno ADSC de nuevo, y una nueva

conversión será iniciada en la primera transición positiva del ciclo de reloj del ADC.

Cuando se usa el auto disparo, el preescalador se reinicia cuando ocurre el evento se

disparo. Esto asegura un retardo fijo desde el evento de disparo hasta el inicio de la

Documento traducido de la hoja de datos del ATmega32 5

__________________________________________________________________________ITSP

conversión. En este modo, el muestreo y retención toma 2 ciclos de reloj del ADC

después de la transición positiva en la señal de la fuente de disparo. Tres ciclos de reloj

del CPU adicionales se usan para la sincronización lógica.

Cuando se usa el modo diferencial, a lo largo del auto disparo de una fuente a otra

conversión completa del ADC, cada conversión requerirá 25 ciclos de reloj del ADC.

Esto es porque el ADC debe deshabilitarse y rehabilitarse después de cada conversión.

En modo libre, una nueva conversión será iniciada inmediatamente después de que la

conversión se completa, mientras ADSC permanece en alto.

Figura 4. Diagrama de tiempos del ADC, primera conversión (Modo de Conversión

Única).

Figura 5. Diagrama de tiempos del ADC, Conversión Única

Documento traducido de la hoja de datos del ATmega32 6

__________________________________________________________________________ITSP

Figura 6. Diagrama de tiempos del ADC, Conversión con Auto Disparo

Figura 7. Diagrama de tiempos, Conversión libre

Documento traducido de la hoja de datos del ATmega32 7

__________________________________________________________________________ITSP

Tabla 1. Tiempo de Conversión del ADC.

Canales de Ganancia Diferencial

Cuando se usan los canales de ganancia diferencial, ciertos aspectos se necesitan

tomar en cuenta durante la conversión.

Las conversiones diferenciales son sincronizadas con el reloj interno CKADC2 igual a la

mitad de reloj del ADC. Esta sincronización se realiza automáticamente por la interfase

del ADC de cierta manera que el muestreo y retención ocurra en una fase específica de

CKADC2. Se inicia una conversión por el usuario (por ejemplo, en las conversiones

únicas, y la primera conversión libre) cuando CKADC2 esta en bajo tomará la misma

cantidad de tiempo que una conversión única (13 ciclos de reloj del ADC del próximo

ciclo de reloj preescalado). Una conversión se inicia por el usuario cuando CKADC2 esta

en alto y tomará 14 ciclos de reloj del ADC debido al mecanismo de sincronización. En

el modo libre, una nueva conversión se inicia inmediatamente después que la

conversión previa se completa, y ya que CKADC2 esta en alto en este tiempo, todas

automáticamente se inician, (por ejemplo, todas pero la primera) las conversiones libres

tomaran 14 ciclos de reloj del ADC.

La etapa de ganancia se optimiza por un ancho de banda de 4kHz en los ajustes de

ganancias. Frecuencias más altas pueden estar sujetas a amplificaciones no lineales.

Un filtro pasa bajo externo deberá usarse si la señal de entrada contiene componentes

de frecuencia más altas que la etapa de ganancia del ancho de banda. Note que la

frecuencia de reloj del ADC es independiente de la limitación de la etapa de ganancia

del ancho de banda. Por ejemplo, el periodo de reloj del ADC puede ser de 6µs,

permitiendo un canal ser muestreado a 12kMPS (Muestras Por Segundo), sin

considerar el ancho de banda de este canal.

Si los canales de ganancia diferencial se usan y las conversiones son iniciadas por el

auto disparo, el ADC debe ser apagado entre conversiones. Cuando el auto disparo se

usa, el preescalador del ADC se reinicia antes que la conversión comience. Ya que la

etapa de ganancia es dependiente de la prioridad del reloj estable del ADC de la

conversión, esta conversión no será valida. Deshabilitando y rehabilitando el ADC entre

cada conversión (escribiendo ADEN en ADCSRA a “0” después a “1”), solamente

conversiones extendidas son ejecutadas. El resultado de las conversiones extendidas

será validado.

Documento traducido de la hoja de datos del ATmega32 8

__________________________________________________________________________ITSP

Cambio de canal o Selección de referencia

Los bits MUXn y REFS1:0 en el registro ADMUX son de un solo buffer a través de un

registro temporal al cual el CPU tiene acceso aleatorio. Esto asegura que los canales y

la selección de referencia solamente tomen lugar en un punto seguro durante la

conversión. El canal y la selección de referencia continuamente se actualizan hasta que

una conversión es iniciada. Una vez que la conversión comienza, el canal y la selección

de referencia se cierran para asegurar un tiempo de muestreo suficiente para el ADC.

Continuas actualizaciones se resumen en el último ciclo de reloj del ADC antes que la

conversión se complete. (ADIF en ADCSRA se pone a uno). Note que la conversión

inicia en la siguiente transición positiva del flanco del reloj del ADC después de que

ADCSRA se escriba. El usuario de esta manera es aconsejado no escribir en el nuevo

canal o los valores de selección de referencia de ADMUX hasta en un ciclo de reloj del

ADC después de que ADSC se escriba.

Si el auto disparo se usa, el tiempo exacto del evento de disparo puede ser

indeterminado. Se deberá tener especial cuidado cuando se actualiza el registro

ADMUX, para controlar cual conversión será afectada por los nuevos ajustes.

Si ambos ADATE y ADEN se escriben a uno, un evento de interrupción puede ocurrir en

cualquier tiempo. Si se cambia el registro ADMUX en este periodo, el usuario no puede

decir si la próxima conversión esta basada en los ajustes pasados o los nuevos.

ADMUX puede actualizarse de manera segura como sigue:

1. Cuando ADATE o ADEN se limpia.

2. Durante la conversión, mínimo un ciclo de reloj del ADC después del evento de

disparo.

3. Después de una conversión, antes que se use la bandera de interrupción como

fuente de disparo y sea limpiada.

Cuando se actualiza ADMUX en una de estas condiciones, los nuevos ajustes afectaran

la próxima conversión ADC.

Especial cuidado deberá tenerse cuando se cambia a canales diferenciales. Una vez

que un canal diferencial ha sido seleccionado, la etapa de ganancia puede tomarse

hasta 125µs para estabilizarse para un nuevo valor. De esta manera las conversiones

no deberán iniciarse dentro de los primeros 125µs después de seleccionar un nuevo

canal diferencial. Alternativamente, el resultado de la conversión obtenido dentro de

este periodo deberá ser descartado.

El mismo ajuste de tiempo deberá ser observado para la primer conversión diferencial

después de cambiarse la referencia del ADC (cambiando los bits REF1:0 en ADMUX).

Canales de Entrada del ADC

Cuando se cambia la selección del canal, el usuario deberá observar la siguiente guía

para asegurar que el canal correcto se seleccionó:

En el modo de conversión única, siempre selecciona el canal antes de iniciar la

conversión. La selección del canal puede ser cambiada en un ciclo de reloj del ADC

Documento traducido de la hoja de datos del ATmega32 9

__________________________________________________________________________ITSP

después de escribir a uno al ADSC. Sin embargo, el método más simple es esperar que

la conversión se complete antes de cambiar la selección del canal.

En el modo de corrimiento libre, siempre seleccione el canal antes de iniciar la primera

conversión. La selección del canal puede cambiarse en un ciclo de reloj del ADC

después de escribir a uno el ADSC. Sin embargo, el método más simple es esperar que

la primera conversión se complete, y entonces se cambia la selección del canal. Ya que

la próxima conversión ya ha iniciado automáticamente, el próximo resultado reflejara la

selección del canal previo. Las conversiones subsecuentes reflejaran la selección del

nuevo canal.

Cuando se cambia a un canal diferencial con ganancia, el primer resultado de la

conversión puede tener una pobre precisión debido al ajuste de tiempo requerido para

la cancelación del corrimiento automático de circuitería. El usuario deberá

preferiblemente descartar el resultado de la primera conversión.

Voltaje de Referencia del ADC

El voltaje de referencia para el ADC (VREF) indica el rango de conversión para el ADC.

Los canales independientes que excedan a VREF resultaran en códigos cercanos a

0x3FF. VREF puede ser seleccionado ya sea como AVCC, 2.56V de referencia interna, o

el pin AREF externo.

El AVCC se conecta al ADC a través de un switch pasivo. La referencia interna de

2.56V se genera de la banda de referencia interna (VBG) a través de un amplificador

interno. En cualquier caso, el pin externo AREF esta directamente conectado al ADC, y

el voltaje de referencia puede ser más inmune al ruido por la conexión de un capacitor

entre el pin AREF y tierra. VREF también se puede medir del pin AREF con el voltímetro

a alta impedancia. Note que VREF es una fuente de alta impedancia, y solamente una

carga capacitiva deberá conectarse en un sistema.

Si el usuario tiene una fuente de voltaje fija conectada al pin AREF, el usuario puede no

usar la otra opción de voltaje de referencia en la aplicación, como serán cortados para

el voltaje externo. Si ningún voltaje externo se aplica al pin AREF, el usuario puede

conmutar entre AVCC y 2.56V como selección de referencia. El resultado de la primera

conversión del ADC después de conmutar la fuente de voltaje de referencia puede ser

impreciso, y se le aconseja al usuario descartar este resultado.

Si se usan los canales diferenciales, la referencia seleccionada no deberá ser tan

cercana al valor de AVCC.

Cancelador de Ruido ADC

La característica del ADC de un cancelador de ruido que habilita la conversión durante

el modo sleep para reducir el ruido inducido del CPU y otros periféricos de I/O. El

cancelador de ruido puede usarse con la reducción de ruido del ADC y el modo ocioso.

Para hacer uso de esta característica, el siguiente procedimiento deberá usarse:

Documento traducido de la hoja de datos del ATmega32 10

__________________________________________________________________________ITSP

1. Asegúrese que el ADC este habilitado y no se encuentre ocupado en una

conversión. En el modo de conversión única debe ser seleccionado y la

interrupción de conversión completa del ADC debe ser habilitada.

2. Entre al modo de reducción de ruido del ADC (o modo ocioso). El ADC iniciara

una conversión una vez que el CPU ha sido detenido.

3. Si ninguna interrupción ocurre antes de que la conversión del ADC se complete,

la interrupción del ADC despertara al CPU y ejecutara la rutina de interrupción de

conversión completa del ADC. Si otra interrupción activa al CPU antes de que la

conversión del ADC se complete, esa interrupción será ejecutada, y una solicitud

de interrupción de conversión completa del ADC será generada cuando la

conversión del ADC se completa. El CPU permanecerá en modo activo hasta

que un nuevo comando de sleep se ejecute.

Note que el ADC no será automáticamente apagado cuando se entra a otro modo sleep

o al modo ocioso y el modo de reducción de ruido del ADC. Se le aconseja al usuario

escribir a cero en ADEN antes de entrar en tales modos sleep para evitar el excesivo

consumo de potencia. Si el ADC es habilitado en tal modo de sleep y el usuario quiere

ejecutar conversiones diferenciales, al usuario se le aconseja cambiar de off a on el

ADC después de despertar del modo sleep y provocar una conversión completa para

obtener el valor valido.

Circuitería de Entrada Análoga

La circuitería de entrada análoga para los canales independientes se muestra en la

siguiente figura. Una fuente análoga aplicada al ADCn esta sujeta a la capacitancia del

pin y al escape de la entrada de ese pin, sin considerar que canal es seleccionado

como entrada para el ADC. Cuando el canal se selecciona, la fuente debe dirigir el

capacitor S/H a través de la serie de resistencias (resistencia combinada en el camino

de entrada).

Se optimiza el ADC para señales análogas con una impedancia de salida de

aproximadamente de 10 KΩ o menos. Si una fuente se usa, el tiempo de muestreo será

insignificante. Si una fuente con alta impedancia se usa, el tiempo de muestreo

dependerá de que tanto tiempo la fuente necesite cargar al capacitor S/H, que puede

variar ampliamente. Se le recomienda al usuario usar solamente fuentes con baja

impedancia con una variación en señal baja, ya que esto minimiza la transferencia de

carga requerida al capacitor S/H.

Si se usan canales de ganancia diferenciales, la circuitería de entrada lucirá diferente,

aunque la impedancia de la fuente de unos pocos cientos de kΩ o menos es

recomendada.

Las componentes de la señal más altas que la frecuencia de Nyquist (fADC/2) no

deberán estar presentes por esa clase de canales, para evitar distorsión de señales de

convolución impredecibles. Se le aconseja al usuario remover las componentes de alta

frecuencia con un filtro pasa bajos antes de aplicarse las señales como entradas al

ADC.

Documento traducido de la hoja de datos del ATmega32 11

__________________________________________________________________________ITSP

Figure 8. Circuitería de Entrada Analógica.

Técnicas de Cancelación de Ruido Analógico

La circuitería digital dentro y fuera del dispositivo genera EMI el cual podría afectar la

precisión de la medición analógica. Si la precisión de la conversión es crítica, el nivel de

ruido puede ser reducido aplicando las siguientes técnicas:

1. Mantenga las rutas de las señales analógicas tan cortas como sea posible. Y

mantenga alejadas las rutas de las conmutaciones digitales.

2. El pin AVCC en el dispositivo deberá conectarse a la fuente de voltaje digital Vcc

vía la red LC como se muestra en la figura.

3. Use la función del cancelador de ruido del ADC para reducir el ruido inducido del

CPU.

4. Si cualquiera de los pines del puerto del ADC se usan como salidas digitales, es

esencial que no se conmuten mientras una conversión esta en progreso.

Documento traducido de la hoja de datos del ATmega32 12

__________________________________________________________________________ITSP

Figure 9. Conexiones de Potencia del ADC.

Esquemas de Corrimiento de Compensación

La etapa de ganancia tiene un circuito de cancelación de corrimiento que anula el

corrimiento de medidas diferenciales como sea posible. El corrimiento restante en el

camino análogo puede ser medido directamente seleccionando el mismo canal para

ambas entradas diferenciales. Este residuo de corrimiento puede ser substraído en

software de los resultados medidos. Usando este tipo de software basado en la

corrección del corrimiento, el corrimiento en cualquier canal puede ser reducido debajo

de un LSB.

Definiciones del ADC Preciso

Una línea de ADC de n-bits convierte un voltaje lineal entre GND y VREF en 2n pasos

(LSBs). El código más bajo se lee como un 0, y el código más alto se lee como 2n-1.

Varios parámetros describen la desviación de una conducta ideal.

Documento traducido de la hoja de datos del ATmega32 13

__________________________________________________________________________ITSP

• Desplazamiento: La desviación de la primera transición (0x000 a 0x001)

comparada con la transición ideal (a 0.5 LSB). El valor ideal: 0 LSB.

Figura 10. Error de Desplazamiento.

• Ganancia de Error: Después de ajustar el desplazamiento, la ganancia de error

se encuentra por la desviación de la última transición (0x3FE a 0x3FF)

comparada con la transición ideal (a 1.5 LSB abajo del máximo). Valor ideal: 0

LSB.

Figura 11. Error de Ganancia.

Documento traducido de la hoja de datos del ATmega32 14

__________________________________________________________________________ITSP

• No Linealidad Integral: Después de ajustar los errores de desplazamiento y

ganancia, la NLI es la máxima desviación de una transición actual comparada

con una transición ideal de cualquier código. Valor ideal: 0 LSB.

Figura 12. No Linealidad Integral (NLI).

• No Linealidad Diferencial: La máxima desviación del ancho del código actual (el

intervalo entre dos transiciones adyacentes) del ancho de código ideal (1 LSB).

Valor ideal: 0 LSB.

Figura 13. No Linealidad Diferencial (NLD).

Documento traducido de la hoja de datos del ATmega32 15

__________________________________________________________________________ITSP

• Error de Cuantización: Debido a la cuantización del voltaje de entrada dentro un

número finito de códigos, un rango de voltajes de entrada (1 LSB de ancho)

codificaran el mismo valor. Siempre ± 0.5 LSB.

• Precisión Absoluta: La máxima desviación de una transición actual (sin ajustar)

comparada a una transición ideal para cualquier código. Este es el efecto

compuesto de desplazamiento, Error de ganancia, Error diferencial, Errores No

Lineales y de Cuantización. Valor Ideal: ± 0.5 LSB.

Resultado de la Conversión del ADC

Después que termina la conversión (ADIF es alta), el resultado de la conversión puede

encontrarse en el Registro de Resultado del ADC (ADCL, ADCH).

Para una sola conversión, el resultado es

Con VIN es el voltaje en el pin de entrada seleccionada y VREF el voltaje de referencia

seleccionado. 0x000 representa la tierra analógica, y 0x3FF representa el voltaje de

referencia menos uno LSB.

Si los canales diferenciales se usan, el resultado es:

Donde VPOS es el voltaje en el pin de entrada positivo, VNEG el voltaje en el pin de

entrada negativo, GAIN, el factor de ganancia positiva, y VREF el voltaje de referencia

seleccionado. El resultado se presenta en formato de complemento a dos, de 0x200 (-

512d) a 0x1FF (+511d). Note que si el usuario desea ejecutar un chequeo rápido de

polaridad del resultado, es suficiente leer el MSB del resultado (ADC9 en ADCH). Si el

bit es uno, el resultado es negativo, si el bit es cero, el resultado es positivo.

Documento traducido de la hoja de datos del ATmega32 16

__________________________________________________________________________ITSP

Figure 14. Medida de Rango Diferencial.

Tabla 3. Correlación entre el Voltaje de Entrada y el Código de Salida.

Documento traducido de la hoja de datos del ATmega32 17

__________________________________________________________________________ITSP

Ejemplo:

ADMUX = 0xED (ADC3 - ADC2, 10x ganancia, 2.56V referencia, resultado con ajuste a

la izquierda)

Voltaje en ADC3 es 300 mV, voltaje en ADC2 es 500 mV.

ADCR = 512 * 10 * (300 - 500) / 2560 = -400 = 0x270

ADCL leerá 0x00, y ADCH leerá 0x9C. Escribiendo a cero a ADLAR con ajuste a la

derecha

El resultado es: ADCL = 0x70, ADCH = 0x02.

REGISTROS DEL ADC

Registro de Selección del Multiplexor ADC – ADMUX

• Bit 7:6 – REFS1:0 Bits de Selección de Referencia

Estos bits seleccionan el voltaje de referencia para el ADC, como se muestra en la

siguiente tabla. Si estos bits se cambian durante una conversión, el cambio no tendrá

efecto hasta que la conversión actual se complete (ADIF en ADCSRA se pone a uno).

Las opciones del voltaje de referencia interno no se usan si un voltaje de referencia

externo esta siendo aplicado al pin AREF.

REFS1 REFS0 Selección del Voltaje de Referencia

0 0 AREF, VREF interno apagado

0 1 AVCC con capacitor externo en el pin AREF

1 0 Reservado

1 1 Voltaje de Referencia Interno 2.56V con capacitor externo en el pin AREF

• Bit 5 – ADLAR: Resultado de Ajuste a la Izquierda del ADC.

El bit ADLAR afecta la presentación de la conversión del resultado del ADC en el

registro de datos del ADC. Escriba a uno en ADLAR para el ajuste a la izquierda del

resultado. De lo contrario, el resultado se ajustara a la izquierda. Cambiando el bit

ADLAR afectara al Registro de Datos Inmediatamente del ADC, sin considerar las

conversiones actuales.

• Bits 4:0: Bits de Selección de Ganancia y Canal Analógico

El valor de estos bits seleccionan cual combinación de entradas analógicas se conectan

al ADC. Estos bits también seleccionan la ganancia para los canales diferenciales. Si

estos bits se cambian durante la conversión, el cambio no tendrá efecto hasta que la

conversión actual se complete (ADIF en ADCSRA se pone a uno).

Documento traducido de la hoja de datos del ATmega32 18

__________________________________________________________________________ITSP

Documento traducido de la hoja de datos del ATmega32 19

__________________________________________________________________________ITSP

Registro A de Estado y Control del ADC – ADCSRA

• Bit 7 – ADEN: Habilitación del ADC

Escribiendo un uno a este bit habilita el ADC. Escribiendo un cero aquí, el ADC se

apaga. Apagando el ADC mientras una conversión esta en progreso, este terminara la

conversión primero.

• Bit 6 – ADSC: Inicia la conversión del ADC

En el modo de conversión única, escriba un uno en este bit para iniciar la conversión.

En el modo libre, escriba un uno para iniciar la primera conversión. La primera

conversión después de que el ADC se habilita, tomara 25 ciclos de reloj del ADC en

lugar de los 13. Esta primera conversión ejecuta la inicialización del ADC.

ADSC leerá como uno tanto como una conversión esta en progreso. Cuando la

conversión se completa, retornara a cero. Escribiendo a cero en este bit no tendrá

efecto.

• Bit 5 – ADATE: Habilitación del Auto disparo del ADC.

Cuando a este bit se le escribe un uno, el auto disparo del ADC se habilita. La

conversión del ADC iniciara por una señal con flanco positivo de la señal de disparo

seleccionada. La fuente del disparo se selecciona ajustando los bits de selección de

disparo, ADTS en SFIOR.

• Bit 4 – ADIF: Bandera de Interrupción del ADC

Este bit se pone a uno cuando una conversión del ADC se completa y los registros de

datos se actualizan. La interrupción de conversión completa del ADC se ejecuta si el bit

ADIE y el bit I (Habilitación de Interrupciones Globales) en SREG se ponen a uno. ADIF

se limpia por hardware cuando se ejecuta el vector de interrupción correspondiente.

Alternadamente, ADIF se limpia escribiendo un uno lógico a la bandera. Tenga cuidado

de que si se realiza la lectura-modifica-escritura en ADCSRA, una interrupción

pendiente puede deshabilitarse. Esto aplica si las instrucciones SBI y CBI son usadas.

• Bit 3 – ADIE: Habilitación de Interrupción del ADC

Cuando este bit se le escribe un uno y el bit I en SREG se pone a uno, la interrupción

de conversión completa del ADC se activa.

• Bits 2:0 – ADPS2:0. Bits de Selección del Preescalador del ADC

Estos bits determinan el factor de división entre la frecuencia del XTAL y la entrada del

reloj al ADC.

Documento traducido de la hoja de datos del ATmega32 20

__________________________________________________________________________ITSP

ADPS2 ADPS1 ADPS0 Factor de Division

0 0 0 2

0 0 1 2

0 1 0 4

0 1 1 8

1 0 0 16

1 0 1 32

1 1 0 64

1 1 1 128

Registro de Datos del ADC ADCL y ADCH

Cuando una conversión en el ADC se completa, el resultado se encuentra en estos dos

registros. Si los canales diferenciales se usan, el resultado se presenta en formato

complemento a dos.

Cuando se lee ADCL, el registro de datos del ADC no se actualiza hasta que ADCH se

lea. Consecuentemente, si el resultado se ajusta a la izquierda y no mas de 8 bits de

precisión se requieren, es suficiente con leer el ADCH. De lo contrario, ADCL debe ser

leído primero, después ADCH.

El bit ADLAR en ADMUX y los bits MUXn en ADMUX afectan la manera en que el

resultado se lee de los registros. Si ADLAR se pone a uno, el resultado se ajusta a la

izquierda. Si ADLAR se limpia (por default), el resultado se ajusta a la derecha.

• ADC9:0. Resultado de la Conversión del ADC

Estos bits representan el resultado de la conversión.

Documento traducido de la hoja de datos del ATmega32 21

__________________________________________________________________________ITSP

Registro de Función Especial de E/S – SFIOR

• Bits 7:5 – ADTS2:0. Fuente de Auto Disparo del ADC

Si ADATE en ADCSRA se escribe a uno, el valor de estos bits seleccionan cual fuente

disparara una conversión en el ADC. Si ADATE se limpia, los ajustes de ADTS2:0 no

tendrán efecto. Una conversión se disparara por la transición positiva de la bandera de

interrupción seleccionada. Note que el cambiar de una fuente de disparo que se limpia a

una fuente de disparo que se pone a uno, generara una transición positiva en la señal

de disparo. Si ADEN en ADCSRA se pone a uno, esto iniciara una conversión.

Cambiando al modo libre (ADTS[2:0]=0) no causara un evento de disparo, aún si la

bandera de interrupción del ADC se pone a uno.

• Bit 4 – Res: Bit Reservado

Este bis se reserva para uso futuro en el ATmega32. para asegurar la compatibilidad de

dispositivos futuros, este bit de pone a cero cuando SFIOR se escribe.

Documento traducido de la hoja de datos del ATmega32 22

Anda mungkin juga menyukai

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiDari EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiPenilaian: 5 dari 5 bintang5/5 (1)

- Modulo Adc Atmega8Dokumen20 halamanModulo Adc Atmega8Jean MelendezBelum ada peringkat

- El Módulo Adc de Los Avr PDFDokumen27 halamanEl Módulo Adc de Los Avr PDFmi_papiBelum ada peringkat

- Avr Registros y InstruccionesDokumen68 halamanAvr Registros y InstruccionesCarlosMarcial12Belum ada peringkat

- Uso Timer1 Como Un ContadorDokumen5 halamanUso Timer1 Como Un ContadorRUBENBelum ada peringkat

- Capitulo4. Directivas y Software Del AVR Studio (Español)Dokumen26 halamanCapitulo4. Directivas y Software Del AVR Studio (Español)Fortino91% (11)

- Ejercicos en Atmega 164p Uso de Interrupciones y Teclado MatricialDokumen7 halamanEjercicos en Atmega 164p Uso de Interrupciones y Teclado MatricialWilmer Villegas CodenaBelum ada peringkat

- 01 Introducción Al Compilador MPLAB XC8Dokumen16 halaman01 Introducción Al Compilador MPLAB XC8Enrique RodriguezBelum ada peringkat

- Arquitectura At89c52Dokumen53 halamanArquitectura At89c52ernesto100% (3)

- Informe Comunicacion SerialDokumen21 halamanInforme Comunicacion Serialdavicho47100% (3)

- Capitulo6. Timer0 Del AVR Del ATmega32 (Español)Dokumen13 halamanCapitulo6. Timer0 Del AVR Del ATmega32 (Español)Fortino100% (3)

- Ejercicios programación PIC16F84 control motoresDokumen3 halamanEjercicios programación PIC16F84 control motoresRoberto Andres Ruiz Pereira100% (1)

- Capitulo7. Timer1 Del AVR Del ATmega32 (Español)Dokumen22 halamanCapitulo7. Timer1 Del AVR Del ATmega32 (Español)Fortino80% (5)

- MANUAL DE PRÁCTICAS DE SISTEMAS DIGITALES II-aDokumen79 halamanMANUAL DE PRÁCTICAS DE SISTEMAS DIGITALES II-aElizabeth Manzano ZavalaBelum ada peringkat

- Ejercicios Básicos para MicroconladoresDokumen8 halamanEjercicios Básicos para MicroconladoresestanizniloBelum ada peringkat

- 3 Progra Del Microcontrolador en Ensamblador (3) (2792)Dokumen32 halaman3 Progra Del Microcontrolador en Ensamblador (3) (2792)Alfredo Pacheco ZapataBelum ada peringkat

- Mis Primeros Programas Con PIC16F84A y PIC16F628A PDFDokumen31 halamanMis Primeros Programas Con PIC16F84A y PIC16F628A PDFCarlos Ayala100% (1)

- Instruciones Microcontroladores Avr en Español)Dokumen36 halamanInstruciones Microcontroladores Avr en Español)Javier Sanchez Mojica100% (13)

- Comunicacion Serial AtmegaDokumen24 halamanComunicacion Serial AtmegaJosé Mamani BravoBelum ada peringkat

- P09 Interface I2C PIC18FDokumen7 halamanP09 Interface I2C PIC18FOscar A. PomaBelum ada peringkat

- Examen Final Domiciliario de PIC en CDokumen4 halamanExamen Final Domiciliario de PIC en CMishell Sanchez GuevaraBelum ada peringkat

- Pic 16F877 2Dokumen67 halamanPic 16F877 2Dan Tabarez100% (1)

- ARQUI - 2017C - USART AVR - Comunicación Serial - Ejemplos - InterrupcionesDokumen27 halamanARQUI - 2017C - USART AVR - Comunicación Serial - Ejemplos - InterrupcionesElvis Justo Vilca CárdenasBelum ada peringkat

- Lab7 Comunicacion Serial Con Pic 16F877A y MikroBasicDokumen5 halamanLab7 Comunicacion Serial Con Pic 16F877A y MikroBasicVictor Azaña PomaBelum ada peringkat

- Punteros en CcsDokumen16 halamanPunteros en CcsTitus_RBelum ada peringkat

- Interrupciones: Estructura y procesamiento básicoDokumen38 halamanInterrupciones: Estructura y procesamiento básicoFrancisco Bueno100% (1)

- Lenguaje C para Microcontroladores AVRDokumen324 halamanLenguaje C para Microcontroladores AVRRafael Bruno82% (11)

- Timer 0 Temporizador y Contador Con El PIC 16F877A-16F628ADokumen4 halamanTimer 0 Temporizador y Contador Con El PIC 16F877A-16F628AeeindustrialBelum ada peringkat

- Programaciones BascomDokumen77 halamanProgramaciones BascomFercHo MDsBelum ada peringkat

- Microcontroladores PIC18F4550.Dokumen15 halamanMicrocontroladores PIC18F4550.Gabriel Acevedo lopezBelum ada peringkat

- Programación Rapida en MikroC Pro For AVRDokumen6 halamanProgramación Rapida en MikroC Pro For AVRJosueAlvaradoBelum ada peringkat

- Multimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásDokumen9 halamanMultimetro Digital Con Pic 16F877A - Libros, Simuladores, Tutoriales Y Mucho MásArmando Campos SalazarBelum ada peringkat

- Teclado Matricial 4x4 Con El PIC16F877ADokumen3 halamanTeclado Matricial 4x4 Con El PIC16F877AGustavoCalderon0% (1)

- MICROCODE Programa de Secuencia de Led y SemaforoDokumen13 halamanMICROCODE Programa de Secuencia de Led y SemaforoDanny Sixto Armijos LoyolaBelum ada peringkat

- P06 Uso Del Teclado Matricial 4x4 y El LCDDokumen7 halamanP06 Uso Del Teclado Matricial 4x4 y El LCDRoger Reynaldo Guachalla NarvaezBelum ada peringkat

- Control de Disparo Por PWMDokumen26 halamanControl de Disparo Por PWMJose Luis Quijano Flores100% (2)

- Ejercicos en Atmega 164p Uso de Conversor A/D y Comunicacion SerialDokumen7 halamanEjercicos en Atmega 164p Uso de Conversor A/D y Comunicacion SerialWilmer Villegas Codena0% (1)

- Termómetro Con 16F877ADokumen9 halamanTermómetro Con 16F877ANelson S100% (1)

- Pic 18F4550Dokumen28 halamanPic 18F4550Yazz Correa MnBelum ada peringkat

- PIC16F877A: Universidad de Las Fuerzas Armadas (Espe-L)Dokumen3 halamanPIC16F877A: Universidad de Las Fuerzas Armadas (Espe-L)alexisltgaBelum ada peringkat

- Codigos Ejemplos VerilogDokumen11 halamanCodigos Ejemplos VerilogJorgito Xd100% (2)

- Proyecto FrecuencimetroDokumen15 halamanProyecto FrecuencimetrodanielBelum ada peringkat

- Clase ADC y Timer0Dokumen12 halamanClase ADC y Timer0DAPUMABelum ada peringkat

- Clase 6. ADC y MemoriaDokumen13 halamanClase 6. ADC y MemoriaSergio GuerreroBelum ada peringkat

- 04 Uso Del ADC Del Microcontrolador PICDokumen8 halaman04 Uso Del ADC Del Microcontrolador PICEnrique RodriguezBelum ada peringkat

- Adc PicDokumen37 halamanAdc PicSergio Díaz BarragánBelum ada peringkat

- Modulo Adc Atmega8Dokumen21 halamanModulo Adc Atmega8Rafael RamoscordovaBelum ada peringkat

- P4 Micros ADCDokumen6 halamanP4 Micros ADCGiovanni Brian Galindo BurgosBelum ada peringkat

- Convertidor Análogo Digital Del Pic 16F877ADokumen15 halamanConvertidor Análogo Digital Del Pic 16F877AMisael Laurencio67% (3)

- Adc SimulinkDokumen6 halamanAdc SimulinkNatalia Cancino GBelum ada peringkat

- Conversores Ad de 10 y 12 BitsDokumen8 halamanConversores Ad de 10 y 12 Bitskapri1001Belum ada peringkat

- Módulo ADC Del Pic16f877Dokumen14 halamanMódulo ADC Del Pic16f877Roberto ArredondoBelum ada peringkat

- IE2009 - Programación de Microcontroladores: Pic16F887 - Módulo Convertidor Análogo DigitalDokumen23 halamanIE2009 - Programación de Microcontroladores: Pic16F887 - Módulo Convertidor Análogo DigitalKevin René Alarcón CalderónBelum ada peringkat

- ADC del PIC18F2550Dokumen13 halamanADC del PIC18F2550Josue MarshallBelum ada peringkat

- Módulo Convertidor Analógico - Digital - MicrocontroladoresDokumen19 halamanMódulo Convertidor Analógico - Digital - MicrocontroladoresHUGO RICARDO AVILA DELGADOBelum ada peringkat

- Conversor ADCDokumen10 halamanConversor ADCLucas Matías JuarezBelum ada peringkat

- Capitulo 7 Convertidor Analógico Digital PDFDokumen23 halamanCapitulo 7 Convertidor Analógico Digital PDFAlfredo VazquezBelum ada peringkat

- 3.9 Módulos Analógicos: Microcontroladores PIC - Programación en C Con EjemplosDokumen24 halaman3.9 Módulos Analógicos: Microcontroladores PIC - Programación en C Con EjemplosJuanJValenciaCruzBelum ada peringkat

- Convertidor Analogo Digital ATMEGA16Dokumen3 halamanConvertidor Analogo Digital ATMEGA16JONATHAN RICARDO CHAVEZ BELTRANBelum ada peringkat

- Paper1 - Manejo Del ADCON2Dokumen5 halamanPaper1 - Manejo Del ADCON2Juan Camilo QuicenoBelum ada peringkat

- I. Guía de Actividades de AprendizajeDokumen6 halamanI. Guía de Actividades de AprendizajeFortinoBelum ada peringkat

- I. Estrategias de Enseñanza AprendizajeDokumen10 halamanI. Estrategias de Enseñanza AprendizajeFortinoBelum ada peringkat

- I. Calendario General de ActividadesDokumen5 halamanI. Calendario General de ActividadesFortinoBelum ada peringkat

- Pensamiento Emancipador de Eugenio Espejo en El Proceso de Independencia de La Real Audiencia de Quito 1780-1822. Quito-Ecuador.Dokumen102 halamanPensamiento Emancipador de Eugenio Espejo en El Proceso de Independencia de La Real Audiencia de Quito 1780-1822. Quito-Ecuador.FortinoBelum ada peringkat

- I. Documento de Información General Del CursoDokumen12 halamanI. Documento de Información General Del CursoFortinoBelum ada peringkat

- Trabajo social: posicionamiento de un saber-hacer-emancipadorDokumen28 halamanTrabajo social: posicionamiento de un saber-hacer-emancipadormarthaBelum ada peringkat

- I. Diseño Instruccional y Teorías Del Aprendizaje en La Era DigitalDokumen13 halamanI. Diseño Instruccional y Teorías Del Aprendizaje en La Era DigitalFortinoBelum ada peringkat

- I. Estilos de AprendizajeDokumen11 halamanI. Estilos de AprendizajeFortinoBelum ada peringkat

- I. Elementos Que Conforman Un Curso de Formación en LíneaDokumen11 halamanI. Elementos Que Conforman Un Curso de Formación en LíneaFortinoBelum ada peringkat

- I. CronogramaDokumen8 halamanI. CronogramaFortinoBelum ada peringkat

- Los Modelos Epistemológicos de Referencia Como Instrumentos de Emancipación de LaDokumen26 halamanLos Modelos Epistemológicos de Referencia Como Instrumentos de Emancipación de LaFortinoBelum ada peringkat

- Educación Matemática Crítica. Influencias Teóricas Y AportesDokumen15 halamanEducación Matemática Crítica. Influencias Teóricas Y Aportesalex madrigalBelum ada peringkat

- Expresion EscritaDokumen40 halamanExpresion EscritaFortinoBelum ada peringkat

- La Importancia de La Red de Apoyo Social paraDokumen28 halamanLa Importancia de La Red de Apoyo Social paraFortinoBelum ada peringkat

- FuzzyDokumen25 halamanFuzzyBeckyBethBelum ada peringkat

- Ejemplo Representacion de SeñalesDokumen7 halamanEjemplo Representacion de SeñalesOmar Gerardo Sida LopezBelum ada peringkat

- Lógica DifusaDokumen19 halamanLógica DifusaFortinoBelum ada peringkat

- Mapas MentalesDokumen5 halamanMapas MentalesFortinoBelum ada peringkat

- Tema 2. Marco Conceptual Del ProcesoDokumen27 halamanTema 2. Marco Conceptual Del ProcesoFortinoBelum ada peringkat

- Cómo Encontrar El Valor Más Alto Y Devolver El Valor de Celda Adyacente en ExcelDokumen4 halamanCómo Encontrar El Valor Más Alto Y Devolver El Valor de Celda Adyacente en ExcelFortinoBelum ada peringkat

- Ingenieria de ProcesosDokumen8 halamanIngenieria de Procesosluvia jazminBelum ada peringkat

- Tema I. ProcesosDokumen52 halamanTema I. ProcesosFortinoBelum ada peringkat

- Circuitos Eléctricos I. Tema 2.2Dokumen41 halamanCircuitos Eléctricos I. Tema 2.2FortinoBelum ada peringkat

- Ingenieria de ProcesosDokumen8 halamanIngenieria de Procesosluvia jazminBelum ada peringkat

- Servicios Educativos CouncilDokumen12 halamanServicios Educativos CouncilFortinoBelum ada peringkat

- Circuitos Eléctricos I. Tema 2.3Dokumen8 halamanCircuitos Eléctricos I. Tema 2.3FortinoBelum ada peringkat

- Antologia. Ingenieria de ProcesosDokumen106 halamanAntologia. Ingenieria de ProcesosFortinoBelum ada peringkat

- Circuitos Eléctricos I. Tema 2.3cDokumen6 halamanCircuitos Eléctricos I. Tema 2.3cFortinoBelum ada peringkat

- Circuitos Eléctricos I. Tema 2.1Dokumen20 halamanCircuitos Eléctricos I. Tema 2.1FortinoBelum ada peringkat

- Circuitos Eléctricos I. Tema 2.3dDokumen6 halamanCircuitos Eléctricos I. Tema 2.3dFortinoBelum ada peringkat

- Conectores lógicos textuales guían la producción de textosDokumen6 halamanConectores lógicos textuales guían la producción de textosAndres Suarez0% (1)

- Tipos de InvestigaciónDokumen9 halamanTipos de InvestigaciónAngel Ortiz castroBelum ada peringkat

- Apachetas y MojonesDokumen15 halamanApachetas y MojonesLaly QuintanaBelum ada peringkat

- Guia 3 y 4Dokumen7 halamanGuia 3 y 4Ludmila RamosBelum ada peringkat

- Indicadores de GestionDokumen11 halamanIndicadores de GestionJheimy Stefany Vargas NovaBelum ada peringkat

- PD OuspenskyDokumen372 halamanPD Ouspenskylednik dindel100% (2)

- Dispositivo de Fortalecimiento en Ciencias Sociales 2014Dokumen10 halamanDispositivo de Fortalecimiento en Ciencias Sociales 2014Fabio RolBelum ada peringkat

- Entre Cronos y Kairos Las Formas Del Tiempo HistorDokumen4 halamanEntre Cronos y Kairos Las Formas Del Tiempo HistorEdinson A. MontoyaBelum ada peringkat

- TALLER 5fisicaDokumen4 halamanTALLER 5fisicaLiliana TorresBelum ada peringkat

- 7.CONCEPTOS de Epidemiologia CassDokumen22 halaman7.CONCEPTOS de Epidemiologia CassMADELLAINE GEORGETTE MEDINA FUENTESBelum ada peringkat

- Tiempo Sin CambioDokumen4 halamanTiempo Sin Cambioskatos28Belum ada peringkat

- Tipos de Modelos de SimulaciónDokumen2 halamanTipos de Modelos de SimulaciónSteeven Tutivén MoránBelum ada peringkat

- Series de TiempoDokumen26 halamanSeries de TiempozulemaBelum ada peringkat

- MRUA laboratorio física USMDokumen4 halamanMRUA laboratorio física USMluis zamoranoBelum ada peringkat

- La Maquina TaquionicaDokumen2 halamanLa Maquina TaquionicaJULIANBelum ada peringkat

- Técnicas de Colecta y Censo de FaunaDokumen39 halamanTécnicas de Colecta y Censo de FaunaEduardo Antonio Molinari Novoa100% (7)

- Qué Hay Más Allá de Este AquíDokumen129 halamanQué Hay Más Allá de Este AquíGonzalo PaviaBelum ada peringkat

- Russell Bertrand - El ABC de La RelatividadDokumen128 halamanRussell Bertrand - El ABC de La RelatividadLucreciaGusmerottiBelum ada peringkat

- La Filosofia Practica de KantDokumen41 halamanLa Filosofia Practica de KantDAVID MOINABelum ada peringkat

- El Día Que Hicimos La TransiciónDokumen21 halamanEl Día Que Hicimos La TransiciónLoquumBelum ada peringkat

- DocumentDokumen236 halamanDocumentJuan Daniel Roncancio HernandezBelum ada peringkat

- Norbert Wiener Cibernetica y Sociedad1 PDFDokumen37 halamanNorbert Wiener Cibernetica y Sociedad1 PDFGiselaBelum ada peringkat

- DURKHEIM - La División Del Trabajo Social, Cáp. 5 Del Libro IIDokumen9 halamanDURKHEIM - La División Del Trabajo Social, Cáp. 5 Del Libro IIClaudio RamosBelum ada peringkat

- Assessment Center - Dinámicas EvaluativasDokumen9 halamanAssessment Center - Dinámicas EvaluativasHeber Yosef Picon Ostos100% (1)

- Informe de Aforo de CanalesDokumen21 halamanInforme de Aforo de CanalesPaul Janco TorrejonBelum ada peringkat

- Velocidad Media-1Dokumen8 halamanVelocidad Media-1webjuancarlosBelum ada peringkat

- Intuicion Del Instante BachelardDokumen68 halamanIntuicion Del Instante BachelardMilton MedellínBelum ada peringkat

- Desarrollo Cognoscitivo de PiagetDokumen2 halamanDesarrollo Cognoscitivo de PiagetLala RivarolaBelum ada peringkat

- Sophia ClubDokumen42 halamanSophia ClubSamadhi ScarpaBelum ada peringkat

- Clase MTMDokumen37 halamanClase MTMPaula Andrea MarulandaBelum ada peringkat