Tutorial Microcontroller MC..

Diunggah oleh

Sivaranjan GoswamiDeskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Tutorial Microcontroller MC..

Diunggah oleh

Sivaranjan GoswamiHak Cipta:

Format Tersedia

Tutorial Microcontroller MCS-51 ATMEL ISP

http://www.mytutorialcafe.com/Microcontroller%20Memory%20Organiz...

Pelatihan Mikrokontroller 15 Januari 2011 Microcontroller Kits Programmer and Target 89s51

BACK NEXT

Searching for block diagram of 8051?

1. Microcontroller MCS-51 Architecture

Searching for block diagram of 8051? Block Diagram of 8051

Top answers for Block Diagram of 8051

www.Answered-Questions.com

Block Diagram of 8051

Top answers for Block Diagram of 8051 www.AnsweredQuestions.com

Simple Mikrokontroller 89s51 Trainer

Searching for Block Diagram of 8051?

Discover 100+ answers for Block Diagram of 8051

www.Answered-Questions.com

Searching for Block Diagram of

Discover 100+ answers for Block Diagram of 8051 www.AnsweredQuestions.com

Chitika | Opt out?

Standart Mikrokontroller 89s51 Trainer

1.1. Memory Organization

All 80C51 devices have separate address spaces for program and data memory, as shown in Figures 1.1.1 and 1.1.2. The logical separation of program and data memory allows the data memory to be accessed by 8-bit addresses, which can be quickly stored and manipulated by an 8-bit CPU. Nevertheless, 16-bit data memory addresses can also be generated through the DPTR register. Program memory (ROM, EPROM) can only be read, not written to. There can be up to 64k bytes of program memory. In the 89s51, the lowest 4k bytes of program are on-chip. In the ROMless versions, all program memory is external. The read strobe for external program memory is the PSEN (program store enable).

Super Mikrokontroller Trainer 89s51

Chitika | Opt out?

All Kits + Include Programmer via USB

1 of 5

01-Apr-12 3:07 PM

Tutorial Microcontroller MCS-51 ATMEL ISP

http://www.mytutorialcafe.com/Microcontroller%20Memory%20Organiz...

Figure 1.1.1 89s51 Block Diagram Data Memory (RAM) occupies a separate address space from Program Memory. In the 80C51, the lowest 128 bytes of data memory are on-chip. Up to 64k bytes of external RAM can be addressed in the external Data Memory space. In the ROMless version, the lowest 128 bytes are on-chip. The CPU generates read and write signals, RD and WR, as needed during external Data Memory accesses. External Program Memory and external Data Memory may be combined if desired by applying the RD and PSEN signals to the inputs of an AND gate and using the output of the gate as the read strobe to the external Program/Data memory. Program Memory Figure 1.1.4 shows a map of the lower part of the Program Memory. After reset, the CPU begins execution from location 0000H. As shown in Figure 1.1.4, each interrupt is assigned a fixed location in Program Memory. The interrupt causes the CPU to jump to that location, where it commences execution of the service routine. External Interrupt 0, for example, is assigned to location 0003H. If External Interrupt 0 is going to be used, its service routine must begin at location 0003H. If the interrupt is not going to be used, its service location is available as general purpose Program Memory.

2 of 5

01-Apr-12 3:07 PM

Tutorial Microcontroller MCS-51 ATMEL ISP

http://www.mytutorialcafe.com/Microcontroller%20Memory%20Organiz...

Figure 1.1.2. Memory Program Structure

Figure 1.1.3. Interrupt Location

Data Memory The right half of Figure 1.4 shows the internal and external Data Memory spaces available to the 80C51 user.The CPU generates RD and WR signals as needed during external RAM accesses. Internal Data Memory is mapped in Figure1.5. The memory space is shown divided into three blocks, which are generally referred to as the Lower 128, the Upper 128, and SFR space.

3 of 5

01-Apr-12 3:07 PM

Tutorial Microcontroller MCS-51 ATMEL ISP

http://www.mytutorialcafe.com/Microcontroller%20Memory%20Organiz...

Figure 1.1.4. Memory Data Structure Internal Data Memory addresses are always one byte wide, which implies an address space of only 256 bytes. However, the addressing modes for internal RAM can in fact accommodate 384 bytes, using a simple trick. Direct addresses higher than 7FH access one memory space, and indirect addresses higher than 7FH access a different memory space. Thus Figure 1.1.5. shows the Upper 128 and SFR space occupying the same block of addresses, 80H through FFH, although they are physically separate entities.

Figure 1.5. Internal Data Memory The Lower 128 bytes of RAM are present in all 80C51 devices as mapped in Figure 1.1.6. The lowest 32 bytes are grouped into 4 banks of 8 registers. Program instructions call out these registers as R0 through R7. Two bits in the Program Status Word (PSW) select which register bank is in use. This allows more efficient use of code space, since register instructions are shorter than instructions that use direct addressing.

4 of 5

01-Apr-12 3:07 PM

Tutorial Microcontroller MCS-51 ATMEL ISP

http://www.mytutorialcafe.com/Microcontroller%20Memory%20Organiz...

Figure 1.1.6. Lower 128 bytes of internal RAM All of the bytes in the Lower 128 can be accessed by either direct or indirect addressing. The Upper 128 (Figure 1.1.7) can only be accessed by indirect addressing.

Figure 1.1.7.Upper 128 Bytes of Internal RAM BACK NEXT

5 of 5

01-Apr-12 3:07 PM

Anda mungkin juga menyukai

- Earth Station AntennaDokumen31 halamanEarth Station AntennaSivaranjan Goswami0% (1)

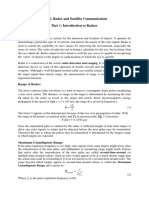

- Introduction To RadarsDokumen4 halamanIntroduction To RadarsSivaranjan GoswamiBelum ada peringkat

- Siv PythonDokumen19 halamanSiv PythonSivaranjan GoswamiBelum ada peringkat

- Binary CodingDokumen3 halamanBinary CodingSivaranjan GoswamiBelum ada peringkat

- Binary CodingDokumen3 halamanBinary CodingSivaranjan GoswamiBelum ada peringkat

- Friend functions and inheritance in CDokumen11 halamanFriend functions and inheritance in CSivaranjan Goswami100% (1)

- Satellite LaunchingDokumen25 halamanSatellite LaunchingSivaranjan GoswamiBelum ada peringkat

- Process in Operating SystemDokumen5 halamanProcess in Operating SystemSivaranjan GoswamiBelum ada peringkat

- Layers of OSI ModelDokumen4 halamanLayers of OSI ModelSivaranjan GoswamiBelum ada peringkat

- Transistor Circuit Design TutorialDokumen16 halamanTransistor Circuit Design TutorialSivaranjan Goswami100% (1)

- Matched Filter - HaykinDokumen3 halamanMatched Filter - HaykinSivaranjan GoswamiBelum ada peringkat

- PPP - Point To Point ProtocolDokumen6 halamanPPP - Point To Point ProtocolSivaranjan Goswami100% (1)

- HFSS ScriptingDokumen420 halamanHFSS ScriptingSivaranjan GoswamiBelum ada peringkat

- Antenna TutorialDokumen20 halamanAntenna TutorialSivaranjan Goswami0% (1)

- OpenCV 2 0 InstallationDokumen11 halamanOpenCV 2 0 InstallationAbdul WaheedBelum ada peringkat

- ZCR Based Identification of Voiced Unvoiced and Silent Parts of Speech Signal in Presence of Background NoiseDokumen30 halamanZCR Based Identification of Voiced Unvoiced and Silent Parts of Speech Signal in Presence of Background NoiseSivaranjan GoswamiBelum ada peringkat

- Inheritance and operator overloading in CDokumen11 halamanInheritance and operator overloading in CSivaranjan Goswami100% (1)

- Embedded C Timer Interrupt 8051Dokumen12 halamanEmbedded C Timer Interrupt 8051Sivaranjan Goswami100% (2)

- DCT Image CompressionDokumen10 halamanDCT Image CompressionSivaranjan Goswami100% (1)

- Guide To Assembly Code-TMS320C5xDokumen314 halamanGuide To Assembly Code-TMS320C5xSivaranjan Goswami0% (1)

- AM Trans-ReceiverDokumen39 halamanAM Trans-ReceiverSivaranjan GoswamiBelum ada peringkat

- A Review On Four Different Methods of FloorplanningDokumen13 halamanA Review On Four Different Methods of FloorplanningSivaranjan GoswamiBelum ada peringkat

- DC Lab ReportDokumen32 halamanDC Lab ReportSivaranjan GoswamiBelum ada peringkat

- Convolution Property of DFTDokumen2 halamanConvolution Property of DFTSivaranjan Goswami100% (1)

- BPSK Signal Through Frequency Selective ChannelDokumen5 halamanBPSK Signal Through Frequency Selective ChannelSivaranjan GoswamiBelum ada peringkat

- GATE TipsDokumen13 halamanGATE TipsSivaranjan GoswamiBelum ada peringkat

- 8051 Programming Ready ReferenceDokumen4 halaman8051 Programming Ready ReferenceSivaranjan Goswami100% (1)

- 5 Ways To Improve ConcentrationDokumen2 halaman5 Ways To Improve ConcentrationHaris IsmailBelum ada peringkat

- ALU 4bitDokumen13 halamanALU 4bitSivaranjan GoswamiBelum ada peringkat

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5782)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (72)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- Automotive Servicing Workshop 3Dokumen32 halamanAutomotive Servicing Workshop 3Alvin RazoBelum ada peringkat

- Mahindra Scorpio MHawk 2.2 TD 2007-2013 Service ManualDokumen762 halamanMahindra Scorpio MHawk 2.2 TD 2007-2013 Service ManualYader Chamorro83% (6)

- Experiment 1 WLF Water Flow MeasurementDokumen4 halamanExperiment 1 WLF Water Flow MeasurementYi Ling GohBelum ada peringkat

- Ajuste Calibracion de Valvulas TH460Dokumen4 halamanAjuste Calibracion de Valvulas TH460UilmerKrdenasBelum ada peringkat

- Beginner Kit For Arduino TutorialDokumen133 halamanBeginner Kit For Arduino TutorialLanz de la CruzBelum ada peringkat

- SCCRDokumen8 halamanSCCRR r r H h hBelum ada peringkat

- Askir C30: Available Models and Accessories Included Basic FSDokumen1 halamanAskir C30: Available Models and Accessories Included Basic FStaibkBelum ada peringkat

- HEAD Ski XRC Catalogue0708 ENDokumen7 halamanHEAD Ski XRC Catalogue0708 ENDaveBelum ada peringkat

- 8040 Datasheet PDFDokumen2 halaman8040 Datasheet PDFrahul.yerrawarBelum ada peringkat

- Edsa PaladinDokumen64 halamanEdsa PaladinDaniel GutierrezBelum ada peringkat

- Technical Data Sheet For The HUS3 Screw Anchor Technical Information ASSET DOC 3357463Dokumen21 halamanTechnical Data Sheet For The HUS3 Screw Anchor Technical Information ASSET DOC 3357463znaky1Belum ada peringkat

- PDF 4077Dokumen72 halamanPDF 4077Ramona Cristina VarbanBelum ada peringkat

- Emotron Fdu2 0 - Manual - 01 5325 01r4.en PDFDokumen252 halamanEmotron Fdu2 0 - Manual - 01 5325 01r4.en PDFТимур КуманцовBelum ada peringkat

- Littelfuse TVS Diode 1 5KE Datasheet PDFDokumen6 halamanLittelfuse TVS Diode 1 5KE Datasheet PDFMuhajir BusraBelum ada peringkat

- AMF 5220 O&M ManualDokumen57 halamanAMF 5220 O&M ManualTaniBelum ada peringkat

- Heuft Basic-Ba R20: Bottle InspectorDokumen2 halamanHeuft Basic-Ba R20: Bottle InspectorImeh NsikakBelum ada peringkat

- BF Am1 enDokumen2 halamanBF Am1 enAhmad Adel El TantawyBelum ada peringkat

- BBK SMP244HDT2 SMP242HDT2 Service ManualDokumen29 halamanBBK SMP244HDT2 SMP242HDT2 Service ManualDaniel Martinez CollazoBelum ada peringkat

- Electrical Design DescriptionDokumen5 halamanElectrical Design DescriptionWQC DriveBelum ada peringkat

- 3 - AURLTE004 KDokumen42 halaman3 - AURLTE004 Kgreat hubBelum ada peringkat

- Lecture 6 Zoning in HvacDokumen32 halamanLecture 6 Zoning in HvacBhaskar BhatiaBelum ada peringkat

- Brochure NGR HilkarDokumen4 halamanBrochure NGR HilkarCandra BaswardaniBelum ada peringkat

- Mathematics SBA (Official Copy)Dokumen27 halamanMathematics SBA (Official Copy)Vanessa sewellBelum ada peringkat

- GR04.F01 FipaDokumen2 halamanGR04.F01 FipaHIDRAFLUIDBelum ada peringkat

- Katalog Techn Unterlagen Grossantriebe en PDFDokumen260 halamanKatalog Techn Unterlagen Grossantriebe en PDFzaidBelum ada peringkat

- Guess The Transport Fun Activities Games Games 58642Dokumen21 halamanGuess The Transport Fun Activities Games Games 58642Thu NguyenBelum ada peringkat

- Eaom-36r Eng v05Dokumen8 halamanEaom-36r Eng v05Khaled KamelBelum ada peringkat

- High Precision Non-Isolated Buck APFC LED Drive ChipsDokumen8 halamanHigh Precision Non-Isolated Buck APFC LED Drive ChipskksandeepBelum ada peringkat

- Comparison of PSFB and FB-LLC topologies for high power DC/DC conversionDokumen49 halamanComparison of PSFB and FB-LLC topologies for high power DC/DC conversionNhật Đào QuốcBelum ada peringkat

- Power and Distribution Transformers Sizing Calculations - Part Nine Electrical KnowhowDokumen11 halamanPower and Distribution Transformers Sizing Calculations - Part Nine Electrical KnowhowRodel PelimianoBelum ada peringkat