1 - F Noise in Cmos Transistors For Analog

Diunggah oleh

Bahar BaratiDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

1 - F Noise in Cmos Transistors For Analog

Diunggah oleh

Bahar BaratiHak Cipta:

Format Tersedia

1/F NOISE IN CMOS TRANSISTORS FOR ANALOG

APPLICATIONS FROM SUBTHRESHOLD TO SATURATION

C. JAKOBSON, I. BLOOM and Y. NEMIROVSKY

Kidron Microelectronics Research Center, Faculty of Electrical Engineering Technion, Israel Institute

of Technology, Haifa 32000, Israel

(Received 12 October 1997; in revised form 6 January 1998)

AbstractDetailed noise measurements of the 1/f noise in p- and n-mos transistors for analog appli-

cations are reported under various bias conditions ranging from subthreshold to saturation. The

CMOS transistors under study have a relatively large area, exhibit long channel behavior and are fabri-

cated in a commercial ``low noise process'', as prescribed for analog applications. A clear methodology

and useful models for the power spectral densities of the gate voltage and drain current are presented

and are based on recent studies in sub-micron transistors that have established the physical origin of 1/

f noise in MOS transistors. In saturation, it is found that it is advisable to limit the bias voltages to

values that are experimentally determined from the transconductance characteristics and correspond to

a nearly constant channel mobility. The experimentally observed reduction in channel mobility indicates

the existence of strong elds that induce additional oxide charging and hence an increase in the eective

density of oxide traps and the noise. In the bias voltages where channel mobility is nearly constant, the

measured input-referred noise power is practically constant. Below threshold voltage, a reduction is

observed in the input-referred noise as gate voltage is decreased, corresponding to the prediction of the

model and due to the exponential reduction of the inversion capacitance with gate voltage. This beha-

vior is observed for both n-mos and p-mos transistors. # 1998 Elsevier Science Ltd. All rights reserved

1. INTRODUCTION

CMOS transistors are often required as ``building

blocks'' in circuits for analog applications. CMOS

transistors are preferred for dense, low voltage and

low power applications. While the advantages of

CMOS technology are well established, there is a

major drawback for analog applications: the MOS

transistors are ``noisy'', even in the so called ``ana-

log low noise'' fabrication processes. The analog

designer faces a formidable challenge: how to design

low noise analog channels with CMOS technology,

taking advantages of the unique features of the

technology and reducing the noise by using appro-

priately the available design parameters.

The noise in CMOS transistors is usually domi-

nated by 1/f noise up to relatively high frequencies

of the order of several tens of kHz. The origin of 1/

f noise in CMOS transistors has been the subject of

numerous studies and controversy ([110], and

references therein). This controversy has been to a

large extent resolved by recent studies that focused

on the microscopic origins of the noise, namely ran-

dom telegraph noise in sub-micron MOSFETS[11

16]. In sub-micron MOSFETs the trappingdetrap-

ping of single inversion carriers at the SiSiO

2

inter-

face causes discrete modulations of the channel

conductance in the form of random telegraph sig-

nals (RTSs). It has been shown that the superposi-

tion of even several RTSs is sucient to give rise to

1/f noise in MOSFETs[1]. Recently, a new

approach to carrier trappingdetrapping 1/f noise

which avoids the oversimplied assumptions that

are usually used to explain 1/f noise, has been pre-

sented[17,18]. By considering the current non-uni-

formities observed in the sub-micron MOSFETS,

the physical picture for the origin of 1/f noise in

ordinary MOSFETs transistors, which accounts for

both carrier number and mobility uctuations, has

been recently established[1118].

However, there is still a considerable gap between

the recent enormous advance in the physical under-

standing of the origin of 1/f noise in CMOS transis-

tors and the requirements of the practitioner

engineer who needs to model and optimize the 1/f

noise of the transistors. Analog designers and users

rely on empirical relation which can be of the

form[19]

S

I

=

Mg

2

m

C

2

ox

ZL

1

f

b

, (1)

where S

I

is the drain current 1/f noise spectral den-

sity, M is an empirical parameter, Z and L are, re-

spectively, the width and channel length, C

ox

is the

oxide capacitance per unit area, g

m

is the transcon-

ductance, and b is a parameter which is close to 1

in a wide frequency range and in any case varies in

a narrow range from 0.8 to 1.2.

It is usually found that ``cleaner'' fabrication pro-

cesses result in lower values for M, other things

being equal. A ``low noise analog process'' is tai-

Solid-State Electronics Vol. 42, No. 10, pp. 18071817, 1998

# 1998 Elsevier Science Ltd. All rights reserved

Printed in Great Britain

0038-1101/98/$ - see front matter

PII: S0038-1101(98)00162-2

1807

lored to yield lower values of M. However, even

state-of-the art ASIC VLSI CMOS processes do

not predict the value of M and the tolerance in M

while other electrical parameters such as at band

voltage, threshold voltage, etc., are well specied

and characterized.

Furthermore, Equation (1) expresses the drain

current 1/f noise spectral density while for certain

applications the noise referred to input is more sig-

nicant for the analysis of the overall system signal

to noise ratio. In many cases, for example in analog

channels for X-ray and gamma-ray spectroscopy,

the spectral resolution is dominated by the 1/f gate

voltage noise of the MOS transistor that resides in

the input of a CMOS charge sensitive preampli-

er[20]. Since S

I

=g

m

2

S

Vgs

, the power spectral density

of 1/f gate voltage noise is:

S

Vg

=

M

C

2

ox

ZL

1

f

b

X (2)

In this case, the noise contribution does not appear

to fundamentally depend on the operation region

(subthreshold or saturation) while actual measure-

ments indicate that the power spectral density of 1/f

gate voltage noise varies between subthreshold to

saturation and depends on the gate voltage. Such

dependence can be introduced only by a possible

dependence of M on the operation point. Hence, it

is highly desirable, even for the practical engineer,

to have a model that will relate M to the electrical

and geometrical parameters of the transistors as

well as to the fabrication technology.

In this paper we model 1/f noise in MOS transis-

tors from subthreshold to saturation. The paper

focuses on relatively large area transistors which

obey the ``long channel'' approximations, since ana-

log applications currently rely on such transistors

and not on sub-micron transistors (note: one of the

reasons to use large-scale transistors in analog ap-

plications is that noise is inversely proportional to

scale, as discussed in Section 6). We start with a

physical model that describes well both n-mos and

p-mos transistors provided they exhibit ``long chan-

nel'' behavior and the gate and drain bias voltages

are relatively low so that the decrease in channel

mobility is negligible. Subsequently we dene the

methodology for calculating 1/f noise in MOS tran-

sistors in a wide range of operating regimes, empha-

sizing the assumptions and the approximations

required to obtain a useful result for the analog de-

sign engineer. We then report 1/f noise measure-

ments of p- and n-MOS transistors fabricated in a

``low noise analog'' CMOS process[21]. The noise

measurements cover the operation regimes from

subthreshold to saturation. The measurements are

investigated in light of the modeling presented in

this paper. The common empirical approach that

appears for example in SPICE[19], is critically dis-

cussed. Finally, the results of this study are inter-

preted in terms of the needs of CMOS low

frequency, low noise analog circuits. In particular,

the eect of gate voltage upon noise, usually

ignored by analog designers, is illuminated.

2. THE PHYSICAL MODEL

2.1. The origin of 1/f noise in MOSFETs

It has been established that capture and emission

at single, individual traps in the SiO

2

gate oxide of

sub-micron MOSFETs cause discrete modulations

of the source-drain conductance in the form of ran-

dom telegraph signals (RTSs)[1116]. While the

superposition of even few (several) RTSs already

gives rise to 1/f noise, in ordinary MOSFETs, the

superposition includes a large number of traps,

resulting in 1/f noise. Furthermore, in sub-micron

MOSFETs, the amplitude of an RTS is shown to

depend on the channel non-uniformity and, in par-

ticular, on the local current density in the immedi-

ate vicinity of the trap center. In large-scale

MOSFETs with the large number of charge carriers

and traps involved, neighboring traps may interact

and the channel current non-uniformity is smeared

out[16].

Thus, it is now recognized that the physical ori-

gin of low frequency noise in MOSFETs is basically

the carrier number uctuation theory known also as

the trappingdetrapping model, originally proposed

by McWhorter. The low frequency noise is caused

primarily by uctuation of the number of inversion

layer carriers as they are trapped and detrapped to

and from traps located in the oxide. These uctu-

ations can also induce uctuations in the channel

mobility of the remaining carriers in the channel

since the traps act as scattering sites when they cap-

ture a carrier. However, in large-scale MOSFETs,

in particular in strong inversion, the Coulomb

eects are eectively screened by the gate and the

channel and these induced mobility uctuations are

normally negligible[16].

2.2. Application of the trappingdetrapping model

According to the trappingdetrapping model,

known also as the number uctuating model[16],

the channel exchanges carriers with the oxide traps

by several types of transitions, including thermally

activated processes and tunneling, depending on the

nature of the trap and the operation conditions.

The model assumes that there is an exponential

dependence of capture and release rates upon trap

depth in the oxide. It is also assumed that oxide

traps are uniformly distributed in space and energy.

The new approach presented in Refs[17,18] avoids

these oversimplied assumptions and therefore sig-

nicantly increases the condence in the physical

picture of the trappingdetrapping model.

Based on the assumptions discussed above and

often cited in the literature, S

Not

/ (f) the power

C. Jakobson et al. 1808

spectral density of the uctuations in the number of

occupied traps, denoted by N

ot

', can be expressed

by

S

Not

/ ( f) = N

ot

LZ

1

f

, (3)

where LZ is the gate area (channel length L times

the gate width Z) and N

ot

[cm

2

] is the equivalent

density of oxide traps per unit area.

3. METHODOLOGY OF MODELING 1/F NOISE IN LONG

CHANNELS MOS TRANSISTORS

The methodology is based on the following: the

power spectral densities of two uctuating physical

parameters are readily obtained from the given re-

lationship between the two parameters provided the

two parameters are related by a constant under-

neath the constraints of the measurement. For

example since dI

d

=g

m

dV

g

, then S

I

d

(f) = g

m

2

S

Vg

(f).

The physical model determines the power spectral

density of the uctuations in the number of occu-

pied traps. The rest is determined by MOS theory

which denes the relationship between the number

of oxide traps, the number of carriers in the chan-

nel, the geometrical dimensions of the transistor

and the electrical parameters I

d

, V

d

, V

g

, i.e. the

drain current, drain voltage and gate voltage, re-

spectively, at the operation point[2,19,22].

Since S

Not

/ (f) is given by the physical model, we

start by dening the relationship between the oxide

traps and the inversion charge. We then directly

relate the inversion charge to the gate voltage and

in this manner obtain S

Vg

(f). The transformation to

S

I

d

(f) and S

V

d

(f) readily follows.

The inversion charge density and the oxide trap

charge density are expressed by

Q

inv

Cb

cm

2

!

=

qN

inv

ZL

and

Q

ot

Cb

cm

2

!

=

qN

ot

/

ZL

,

where N

inv

is the total number of carriers in the

channel and N

ot

' is the total number of occupied

traps.

According to MOS theory (see Appendix A)

dQ

inv

=

C

inv

C

ox

C

d

C

inv

!

dQ

ot

, (4)

where C

d

is the depletion capacitance, C

ox

is the

oxide capacitance, and C

inv

is the inversion capaci-

tance; all expressed per unit area. Hence, for small

signal analysis (corresponding to small uctuations)

S

Q

inv

( f) =

C

inv

C

ox

C

d

C

inv

!

2

S

Qot

( f)X (5)

Since S

Qot

(f) = (q/ZL)

2

S

Not

/ (f) and S

Not

/ (f) is given

by Equation (3), then

S

Qinv

( f) =

C

inv

C

ox

C

d

C

inv

!

2

q

2

N

ot

ZL

1

f

(6)

Under strong inversion, C

inv

bbC

ox

+C

d

and

Equation (6) is simplied to

S

Q

inv

( f) =

q

2

N

ot

ZL

1

f

X (7)

The relation between S

Q

inv

(f) and S

Vg

(f) is derived

for each operation region in Section 4.

4. MODELING OF NOISE

The subsequent modeling relates to large area,

``long channel'' transistors operating from subthres-

hold to saturation but in a limited range of gate

and drain bias voltages where the channel mobility

is practically constant. The bias region correspond-

ing to this assumption is indicated experimentally

from the dependence of the measured transconduc-

tance upon bias voltages (see Fig. 3).

4.1. At strong inversion in the linear region

According to MOS theory, for strong inversion,

in the linear region at low drain voltages (V

d

40)

Q

inv

( y) = C

ox

(V

g

V

t

)X (8)

Assuming that the uctuations in occupied oxide

traps have a negligible eect on threshold voltage,

i.e. dQ

ot

``Q

f

where Q

f

is the xed surface state

charge density,

S

Q

inv

( f ) = C

2

ox

S

Vg

( f)X (9)

Thus, combining Equations (7) and (9), an ex-

pression for S

Vg

(f) is readily obtained

S

Vg

( f) =

q

2

C

2

ox

N

ot

ZL

1

f

X (10)

Equation (10) is determined only by N

ot

and the

geometrical parameters C

ox

, Z and L and is inde-

pendent of carrier mobility and biasing condition

(V

g

, V

d

) provided N

ot

is independent of gate vol-

tage. Once S

Vg

(f) is determined, S

I

d

(f) and S

V

d

(f)

can be readily obtained.

In the linear region g

m

=(C

ox

mZ/L)V

d

=[I

d

/

(V

g

V

t

)] and g

m

is constant at a constant V

d

.

Accordingly,

S

I

d

( f) = g

2

m

S

Vg

( f) =

q

2

C

2

ox

I

d

V

g

V

t

2

N

ot

ZL

1

f

X (11)

For V

ds

in the linear region (V

ds

<V

gs

V

r

) a depen-

dence [V

ds

/(V

gs

V

t

)]

1 + d

with 0 < d < 1 has been

observed[23].

4.2. At strong inversion in the saturation region

In saturation, for V

d

bbV

ds,sat

QV

g

V

t

, the channel

is pinched o. The channel is non-uniform and the

1/f noise in CMOS transistors 1809

inversion layer charge is a function of y, the dis-

tance along the channel.

Thus, Equation (8) is replaced by

Q

inv

( y) = C

ox

[V

g

V

t

V( y)[, (12)

where V(y) varies between 0 at y = 0 and

V

ds,sat

QV

g

V

t

at y = L

e

(the point of pinch-o).

The average inversion charge is dened by

Q

inv

=

1

L

eff

L

eff

0

Q

inv

( y) dy

=

C

ox

L

eff

VgVt

0

[V

g

V

t

V( y)]

dV

dVady

X (13)

Multiplying the integrant by Q

inv

and dividing by

Q

inv

and since Q

inv

(dV/dy) = I

d

/Zm and I

d

is con-

stant along the channel and at saturation is given

by I

d

=(C

ox

mZ/2L

e

)(V

g

V

t

)

2

, we thus obtain

Q

inv

=

2

3

C

ox

(V

g

V

t

)X (14)

Accordingly,

S

Qinv

( f) =

4

9

C

2

ox

S

Vg

( f)X (15)

To relate S

Q

inv

(f) to N

ot

, the capacitive ratio in the

square brackets of Equation (6) must also be aver-

aged along the channel. At y = 0, i.e. near the

source, strong inversion prevails, C

inv

is larger than

C

ox

and C

d

and the value is 1. At the pinch-o

point, C

inv

=0 and the value is 0. Hence, S

Q

inv

(f) is

related to N

ot

by an approximate factor of 1/2 (see

Equation (6)), yielding

S

Vg

( f)

q

2

C

2

ox

N

ot

ZL

1

f

X (16)

Thus, the power spectral density of the gate voltage

at saturation practically equals to that in the linear

region and should be independent of gate voltage

provided N

ot

does not increase with V

g

.

At saturation

g

m

=

C

ox

mZ

L

eff

(V

g

V

t

) =

2

C

ox

mZ

L

eff

I

d

r

X (17)

Assuming small signal analysis, S

Id

=g

m

2

S

Vg

, and

S

I

d

( f)

q

2

mN

ot

I

d

C

ox

L

2

eff

1

f

X (18)

Equation (18) predicts that for a given I

d

, the

power spectral density of the drain current of p-mos

is lower than that of an n-mos by the ratio of the

corresponding mN

ot

product, i.e. the eective mobi-

lity and eective density of oxide trap product.

While S

Vg

(f) scales down with C

ox

2

and ZL, S

I

d

(f)

scales down with C

ox

and L

e

2

.

4.3. At subthreshold

At weak inversion below threshold using

Equation (6) and assuming C

inv

``C

ox

, C

d

, then

S

Vg

( f)

1

C

2

ox

S

Q

inv

( f) =

1

C

2

ox

C

inv

C

ox

C

d

!

2

q

2

N

ot

ZL

1

f

X

(19)

In weak inversion and for long channel devices, the

only current that ows is assumed to be diusion

current I

d

=qD

n

A(dn/dy). Current continuity

requires that dn/dy is constant and hence that the

electron density is linear with distance. Therefore,

n(y)In(0)[1 y/L]. The electron densities at the

source and drain are, respectively, n(0) = n

p,0

e

qf

s

akT

and n(L) = n

p,0

e

qf

s

akT

e

qV

d

akT

. Accordingly, the

density of inversion charges is

n

inv

1

L

n(0)

L

0

1

y

L

dy =

1

2

n(0) =

1

2

n

p,0

e

qf

s

akT

1

2

n

p,0

e

qVgankT

(20)

where n

p,0

are the minority carrier concentration on

p-type substrate of the n-mos and n = (C

ox

+C

d

)/

C

ox

is the capacitive ratio between the oxide capaci-

tance and the depletion capacitance. Q

inv

is directly

related to n

inv

.

C

inv

is dened by dQ

inv

/df

s

and at subthreshold

is approximated by Q

inv

/(kT/q). Hence, C

inv

exhibits

an exponential dependence upon gate voltage and

the value of the capacitive ratio in Equation (19) is

exponentially reduced as gate voltage is reduced.

Hence, the model predicts that at subthreshold,

S

Vg

(f) will exhibit an exponential voltage depen-

dence, and will be signicantly reduced as gate vol-

tage is reduced.

At subthreshold, the drain current is related to

gate voltage by I

d

QI

0

e

qVgankT

where n is the capaci-

tive ratio dened above. Hence, g

m

Q(qI

d

/kT)[C

ox

/

(C

ox

+C

d

] and using Equation (19),

S

I

d

( f) =

C

2

inv

(C

ox

C

d

)

4

q

4

(kT )

2

I

2

d

N

ot

ZLf

X (21)

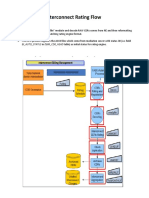

5. EXPERIMENTAL SETUP

The experimental setup for measuring the low

frequency drain current noise spectrum of the

MOSFET is shown in Fig. 1. The transistor is con-

nected in a common source conguration and is

d.c. coupled to the Stanford Research SR570 Low

Noise Current Amplier. The output of this ampli-

er is connected to an HP3562 Dynamic Signal

Analyzer which samples this signal and calculates

its Fourier transform. This transform provides the

power spectral density of the incoming voltage in

the frequencies of interest.

To verify the expressions of the 1/f noise devel-

oped in the previous sections, it is necessary to

achieve a good precision in the variations of the

d.c. parameters of the transistor. To this end, an ex-

C. Jakobson et al. 1810

perimental setup fully controlled by a PC has been

built, which can work stand alone for hours as

required for these measurements. The adjustable

d.c. parameters are: the gate voltage, determined by

a 12 bit D/A converter, and the drain voltage,

determined by the bias voltage input of the current

amplier. The desired drain current is adjusted by

introducing an oset current to the current ampli-

er and adjusting to zero its output. In this way,

the measurement can be performed at xed current

steps, instead of voltage steps. To execute the zero

adjust, an A/D is added to the setup, and connected

to the output of the current amplier. The sensi-

tivity of the amplier is also controlled by the PC,

and xed for each drain-voltage condition by an in-

ternal algorithm. The measurement results are also

acquired by the PC from the Dynamic Signal

Analyzer. R

G

and C

G

are added to lter input noise

from the D/A converter.

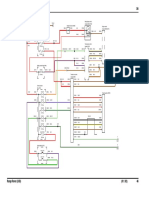

The noise contribution of the dierent elements

in the setup is calculated using the small signal cir-

cuit shown in Fig. 2. The main noise sources are:

the current noise of the current amplier, and the

drain current noise of the MOSFET, which is the

noise source we want to measure. The additional

contributions from the D/A converter and the bias

voltage are adequately ltered, and hence elimi-

nated from the measurement.

The power spectral density of the output voltage

measured by the DSA is given by

S

Vout

=

S

ID

S

2

S

Ia

4kTS

4kT

R

off

1

S

2

S

Va

1

r

ds

R

off

r

ds

R

off

S

2

X (22)

Where S

ID

is the drain current noise of the

MOSFET, r

ds

is the drain source resistance of the

MOSFET, S is the sensitivity of the low noise cur-

rent amplier, R

o

is the resistor, connected to a

variable voltage, used internally by the low noise

current amplier to generate the oset current, S

Ia

and S

Va

are the input current and input voltage

noise, respectively, of the operational amplier

AD743.

The desired noise spectrum is the rst term in

Equation (22). To make the other terms negligible

the following conditions are immediately derived

S

Ia

_S

ID

,

1

S

4kTS

ID

,

S

Va

_S

ID

1

S

r

ds

R

off

2

X (23)

The noise sources of the resistors are directly calcu-

lated, while the noise sources from the AD743 oper-

ational amplier are taken from its data sheet. At

1 kHz the input noise current is and the input vol-

tage noise is 7fA/

Hz

_

. The input capacitance C

inp

of the operational amplier is 20 pF.

Fig. 1. Schematics of the low frequency noise measurement set-up.

1/f noise in CMOS transistors 1811

With this set-up, the gate and drain voltages can

be independently controlled and varied. The d.c.

characteristics of the MOSFETs studied are separ-

ately measured using a Semiconductor Parameter

Analyzer (HP). The gate transconductance is found

by deriving numerically these characteristics. The

input referred noise is obtained by dividing S

ID

by

the square of the measured gate transconductance

evaluated at each data point. The fact that the gate

transconductance is measured rather than calculated

is crucial to minimize errors in noise data.

6. RESULTS AND DISCUSSION

The small-signal transconductance is measured

for each bias point. Figure 3 shows a family of gate

transconductance characteristics plotted as a func-

tion of the gate-source voltage with the drain-source

voltage as a parameter, for the relatively large area

n-mos and p-mos under study. The measured trans-

conductance is an important parameter in measur-

ing the low frequency noise of the MOS transistors.

Furthermore, the measured transconductance also

exhibits the range of drain and gate bias voltages

corresponding to a practically constant channel

mobility. From Fig. 3(a), for the n-mos, V

t

=0.79 V

and the observed value of the eective channel

mobility is m

n

=543 cm

2

V

1

s

1

and it is practically

constant for V

gs

<2.5 V. Similarly, from Fig. 3(b),

for the p-mos, V

t

=0.91 V and the observed value

of the eective channel mobility is

m

p

=207 cm

2

V

1

s

1

and it is practically constant

for V

gs

<1.6 V. Moreover, when the transconduc-

tance at saturation becomes lower because of

reduced mobility, it indicates that there is a large

electric eld[22,24]. At high electrical elds, there is

an additional oxide charging, as indicated by

increased gate current leakage[25]. Accordingly,

there is a signicant increase in the eective oxide

trap density N

ot

and a corresponding increase of

the drain current and gate voltage noise power

spectral density. Thus, in analog application, it is

very important to limit in saturation the applied

gate and drain voltages to values where the decrease

in channel mobility is very small, as proposed in

this study.

Figure 4 exhibits the dependence of the measured

power spectral density of the drain current upon

mean drain current. S

ID

increases with increasing

drain current. The general behavior corresponds to

the predictions of the modeling of Section 3

(Equation (11) for the linear region, Equation (18)

at saturation, Equation (21) at subthreshold). The

n-mos and p-mos exhibit similar behavior but the

power spectral density of the drain current of the p-

mos transistor is lower by approximately one and a

half orders of magnitude compared to that of the n-

mos. This result corresponds to the predictions of

the modeling and corresponds to the lower mobility

(approximately by a factor of H2.5 as derived from

Fig. 3) and a lower eective N

ot

(by a factor of 15,

see below).

Figure 5 shows the power spectral density of the

gate voltage S

Vg

(input-referred noise). Above V

t

,

S

Vg

is practically constant with V

g

for n-mos and

slightly increases with gate voltage in p-mos transis-

tors, provided V

g

does not exceed the value that

corresponds to a practically constant mobility

(obtained from the dependence of the gate trans-

conductance upon gate voltage). When a larger gate

voltage is applied, both n-mos and p-mos transistors

exhibit an increase in S

Vg

. The value of S

Vg

is lower

by over an order of magnitude for the p-mos tran-

sistor, indicating a lower density of eective oxide

traps for the p-mos transistor. For the transistors of

Fig. 5, a reduction by a factor of H15 is observed.

Below threshold voltage, the measured noise

behavior in subthreshold corresponds to the predic-

tions of the modeling (Section 4.3). A signicant re-

duction at subthreshold is observed due to the

exponential reduction of C

inv

with gate voltage.

This behavior is observed for both n-mos and p-

mos transistors.

The eective density of oxide traps is obtained

from Fig. 6. Figure 6 shows the measured M of the

empirical expression of Equation (2) which is

obtained by normalizing the measurements of the

input-referred noise at f = 1 Hz with geometrical

dimensions and C

ox

(i.e. according to Equation (2)).

Fig. 2. Small-signal model of the noise sources in the measurement set-up.

C. Jakobson et al. 1812

The measured values of M for several n-mos and p-

mos transistors with dierent areas and process

runs (but exposed to the same ``low noise pro-

cess''[21]) vary, respectively, between M = (42

2)10

30

Cb cm

2

and M = (221)10

32

Cb cm

2

.*

Above threshold voltage, by comparing Equation (2)

and Equations (10) and (16), it is seen that

M = q

2

N

ot

. Thus, the eective density of oxide

traps for n-mos and p-mos, denoted, respectively,

by N

ot,n

and N

ot,p

, are derived. The measured values

obtained from Fig. 6 are N

ot,n

=1.2 10

7

cm

2

and

N

ot,p

=0.810

6

cm

2

. To relate N

ot

to the CMOS

Fig. 3. The measured gate transconductance g

m

as a function of gate voltage V

GS

with drain voltage

V

DS

as a parameter (a) n-channel 110 mm/10 mm, (b) p-channel 100 mm/10 mm. Both transistors have

been fabricated by a ``low noise'' process[21]. The dashed line is the transconductance at saturation

g

m,sat

.

*For clarity, we have indicated in Fig. 6 these average M

values which are assumed to be independent of the

gate voltage in the range marked in the gure.

1/f noise in CMOS transistors 1813

process technology and the type of the transistor

(n-mos, p-mos), it is useful to dene the eective

density of oxide traps by N

ot

[cm

2

] = kTN

t

(E)/g, in

which N

t

(E) [cm

3

eV

1

] is the density of oxide

traps per unit volume and unit energy (and is deter-

mined by the technology), g is the McWhorter tun-

neling parameter which depends on the eective

mass of the tunneling carrier as well as on the bar-

rier height (and hence on the transistor type). For

N

t

(E) = 4 10

16

cm

3

eV

1

, kT = 0.026 eV at

300 K, 1/g of the order of 1 A, N

ot

is of the order

of 10

7

cm

2

.

Fig. 4. Measured drain current noise power spectral density S

ID

as a function of the mean drain current

from subthreshold to saturation (a) for the n-channel mos transistor of Fig. 3(b) for the p-channel mos

transistor of Fig. 3. The dashed line indicates the behavior predicted by the noise models of Section 3.

Fig. 5. Input-referred noise spectra (gate voltage power spectral density) as a function of gate voltage

from subthreshold to saturation (a) for the n-channel mos transistor of Fig. 3(b) for the p-channel mos

transistor of Fig. 3.

C. Jakobson et al. 1814

In general, p-mos transistors have noise levels

one to two orders of magnitude lower than those of

n-channel devices with similar gate geometry and

fabricated by the same technology at the same pro-

cess run. This can be attributed to the larger tunnel-

ing barrier (4.8 eV) for holes relative to that of

electrons (3.1 eV) and the dierent electron and

hole eective mass, resulting in dierent typical tun-

neling parameters g as well as to possibly dierent

oxide trap densities N

t

(E) near the valence and con-

duction band edges[5].

The gate area dependence of the input-referred

noise power of both n-mos and p-mos transistors is

shown in Fig. 7. The noise power varies as the

Fig. 6. Empirical noise constant M for various n-channel and p-channel mos transistors. The marked

lines indicate the range of M-values independent of gate voltage.

Fig. 7. The normalized input-referred noise power of MOS transistors operating in saturation, plotted

vs channel area. Solid dots: n-mos, Open circles: p-mos. The dashed lines show the 1/area dependence.

1/f noise in CMOS transistors 1815

inverse of the channel area, as predicted by the

modeling, down to small-scale transistors with gate

area of the order of 3 mm

2

. Using the measured

values of N

ot

, the volume density of oxide traps in

the ``low noise analog process''[21] under study is

estimated to be N

t

(E)kTQ10

15

cm

3

. The total

number of oxide traps within an oxide thickness of

100 A and a gate area of 100 10 mm

2

yields a total

number of the order of 10

4

traps. For the technol-

ogy reported here, the random telegraph signal[11

16] is observed only in sub-micron transistors.

7. SUMMARY

Noise is a signicant factor in designing analog

circuits. Although circuit techniques have been

developed to reduce the eects of 1/f noise[26], it is

clear that the ultimate low noise performance will

be limited by the noise factor M of the devices in

the circuit. In particular, the input transistor of the

rst stage plays a critical role in the overall circuit

noise (since the noise contribution of the following

transistors is reduced by the gain of the rst stage).

Since low frequency noise cannot be avoided while

using CMOS technology, taking advantage of avail-

able design parameters and the understanding of

the physical origin of the noise to reduce noise, is

highly desirable.

The present study focuses on large area, long-

channel transistors, operating between subthreshold

and saturation but in a limited range of gate and

bias voltages where channel mobility is practically

constant. A clear methodology and simple models,

based on well dened assumptions and approxi-

mations, have been derived for the power spectral

densities of the gate voltage and drain current. The

general behavior of the measurements corresponds

to the predictions of the modeling. The modeling

presented here relates M to the eective density of

oxide traps N

ot

and to the operation point. At sat-

uration, for gate and drain voltage region exhibiting

a nearly constant channel mobility, M = q

2

N

ot

, and

is nearly independent of gate voltage.

A key parameter which is usually determined by

available chip area is the channel area. Maximizing

the channel area will yield the minimum noise since

the noise is inversely proportional to gate area in

all regions of operation. It should be noted though

that this increases the input capacitance and for

example in capacitive readout often violates capaci-

tance matching[20].

Another key issue is the type (p-channel vs n-

channel) and the operation point of the transistor,

which for a given process determine the value of

the noise factor M. M is a process dependent

empirical constant, which in strong inversion and

suciently low gate voltage (corresponding to a

practically constant channel mobility) is nearly

independent of bias voltages. The measured values

of M for n-mos and p-mos transistors, fabricated in

a ``low noise analog process''[21] vary, respectively,

between

M=(422)10

30

Cb

2

acm

2

and

M=(221)10

32

Cb

2

acm

2

X

Below threshold voltage, a signicant reduction is

observed in the input-referred noise as gate voltage

is decreased, corresponding to the prediction of the

model and due to the exponential reduction of the

inversion capacitance with gate voltage. This beha-

vior is observed for both n-mos and p-mos transis-

tors. Hence, lowering the operation gate voltage is

an additional viable method for 1/f noise reduction.

For the best 1/f noise performance, a low value of

gate bias corresponding to subthreshold is war-

ranted. The usefulness of this reduction is deter-

mined by the frequency range of operation of the

circuit since in subthreshold the thermal noise is

increased. Bias in subthreshold is also known for

providing the largest ratio of gate transconductance

to drain current (this ratio determines the gain of

the stage).

If system constraints are required to operate the

mos transistor in saturation, it is again advisable to

apply a lower gate voltage where the transistor

exhibits a nearly constant channel mobility and cor-

respondingly, a nearly constant input-referred noise.

It is shown here that the useful bias voltages can be

experimentally determined from the measured

characteristics of the transconductance. At higher

gate voltages where the channel mobility starts to

decrease, the power spectral density increases and

this is attributed to additional oxide charging and

hence to an eective increase in N

ot

. This eect is

even more pronounced in p-mos transistors where

the reduction in channel mobility and the increase

of the noise-referred-to-input are observed in lower

gate voltages (compared to n-mos).

AcknowledgementsThis research was supported by the

Kidron Foundation and was performed in the laboratories

donated by Etia and Miguel Meilichson. The research was

also supported by Technion V. P. R. Fund-Promotion of

Sponsored Research. We gratefully thank Mrs. Gitta

Abraham for typing the manuscript.

REFERENCES

1. Kirton, M. J. and Uren, M. J., Noise in solid-state

microstructures: A new perspective on individual

defects, interface states, and low-frequency (1/f) noise,

Adv. Phys., 1989, 38, 367468.

2. Simonne, J. J., Blasquez, G. and Barbottin, G., 1/f

noise in MOSFETs, in Instabilities in Silicon Devices:

Silicon Passivation and Related Instabilities, Vol. 2.

Elsevier, Amsterdam, 1989, pp. 639657.

3. McWhorter, A. L., 1/f noise and germanium surface

properties, in Semiconductor Surface Physics. Univ.

Pennsylvania Press, Philadelphia, 1957, pp. 207228.

4. Reimbold, G., Modied 1/f trapping noise theory and

experiments in MOS transistors biased from weak to

C. Jakobson et al. 1816

strong inversion-inuence of surface states, IEEE

Trans. Electron Dev., 1984, 31(9), 11901198.

5. Scoeld, J. H., Borland, N. and Fleetwood, D. M.,

Reconciliation of dierent gate-voltage dependencies

of 1/f noise in n-mos and p-mos transistors, IEEE

Trans. Electron Dev., 1994, 41(11), 19461952.

6. Fleetwood, D. M., Meisenheimer, T. L. and Scoeld,

J. H., 1/f noise and radiation eects in MOS devices,

IEEE Trans. Electron Dev., 1994, 41(11), 19531964.

7. Vandamme, L. K. J., Li, X. and Rigaud, D., 1/f noise

in MOS devices, mobility or number uctuations?.

IEEE Trans. Electron Dev., 1994, 41(11), 19361944.

8. Chang, J., Abidi, A. A. and Viswanathan, C. R.,

Flicker noise in CMOS transistors from subthreshold

to strong inversion at various temperatures, IEEE

Trans. Electron Dev., 1994, 41(11), 19651971.

9. Vandamme, L. K. J., 1/f noise in CMOS transistors,

10th Int. Conf. on Noise in Physical Systems, 1990, pp.

491494.

10. Hooge, F. N., 1/f noise sources, IEEE Trans. Electron

Dev., 1994, 41(11), 19261935.

11. Kirton, M. J., Uren, M. J., Collins, S., Schulz, M.,

Karmann, A. and Scheer, K., Semicond. Sci.

Technol., 1989, 4, 1116.

12. Ralls, K. S., Skocpol, W. J., Jackel, L. D., Howard,

R. E., Fetter, L. A., Epworth, R. W. and Tennant, D.

M., Discrete resistance switching in submicrometer

silicon inversion layers: individual interface traps and

low-frequency (1/f?) noise. Phys. Rev. Lett., 1984, 52,

228231.

13. Schulz, M., Coulomb energy of traps in semiconduc-

tor space charge regions, J. Appl. Phys., 1993, 74(4),

26492657.

14. Mueller, H. H. and Schulz, M., J. Mat. Sci., 1995, 6,

65.

15. Mueller, H. H. and Schulz, M., Conductance modu-

lation of submission MOSFETs by single-electron

trapping, J. Appl. Phys., 1996, 79, 41784186.

16. Mueller, H. H. and Schulz, M., Statistics of random

telegraph noise in sub-micron MOSFETs, in Noise in

Physical Systems and 1/f Fluctuations, ed. C. Claeys

and E. Simoen. World Scientic, 1997, p. 195.

17. Nemirovsky, A. and Ron, A., A new approach to car-

rier trapping-detrapping 1/f noise, in Noise in Physical

Systems and 1/f Fluctuations, ed. C. Claeys and E.

Simoen. World Scientic, 1997, p. 85.

18. Nemirovsky, A. and Ron, A., A revised model for

carrier trapping-detrapping 1/f noise, Solid-St.

Electron., 1997. To be published.

19. Tsividis, Y. P., Operation and Modeling of the MOS

Transistor. McGraw Hill, 1988.

20. Jakobson, C., CMOS low noise switched charge sensi-

tive preamplier for CdTe and CdZnTe X-ray detec-

tors, IEEE Trans. Nucl. Sci., 1997, 44(1), 2025.

21. MOSIS (Metal Oxide Semiconductor Implementation

Service) a multiproject fabrication service run by

ARPA (Advanced Research Projects Agency).

22. Pierret, R. F., Field eect devices, in Addison-Wesley

Modular Series on Solid State Devices, Vol. 4. N.Y.,

1990.

23. Li, X. and Vandanne, L. K. J., An explanation of 1/f

noise in LDD MOSFETs from the Ohmic region to

saturation, Solid-St. Electron., 1993, 36, 15151521.

24. Sun, S. C. and Plummer, J. D., IEEE Trans. Electron

Dev., 1980, ED-27, 1497.

25. Nemirovsky, Y. et al., The eect of gate leakage cur-

rents on 1/f noise in MOSFETs, unpublished results.

26. Gregorian, R. and Temes, G. C., Analog MOS

Integrated Circuits for Signal Processing. N.Y., Wiley,

1986, pp. 502513.

APPENDIX A

The equation that governs the performance of the MOS

structure is

V

G

F

MS

Q

ot

C

ox

=

Q

D

C

ox

Q

inv

C

ox

f

s

(AX1)

The inversion and depletion capacitances are dened, re-

spectively, by

C

inv

=

dQ

inv

df

s

, C

D

=

dQ

D

df

s

X (AX2)

For a xed voltage V,

dQ

ot

C

ox

=

dQ

D

C

ox

dQ

inv

C

ox

df

s

X (AX3)

Accordingly,

dQ

ot

df

s

= C

D

C

inv

C

ox

and

dQ

inv

dQ

ot

=

C

inv

C

ox

C

D

C

inv

X (AX4)

Note: The interface traps capacitance, C

it

, is neglected

here, since C

it

``C

ox

in the transistors under study.

1/f noise in CMOS transistors 1817

Anda mungkin juga menyukai

- Ecc R12.2.XDokumen118 halamanEcc R12.2.XDM100% (1)

- MOS Integrated Circuit DesignDari EverandMOS Integrated Circuit DesignE. WolfendaleBelum ada peringkat

- Automotive CAN Bus System Explained - Kiril Mucevski - Pulse - LinkedInDokumen7 halamanAutomotive CAN Bus System Explained - Kiril Mucevski - Pulse - LinkedInnarendra100% (2)

- Low Phase Noise VCO Design Thesis PDFDokumen133 halamanLow Phase Noise VCO Design Thesis PDFAhmed KamalBelum ada peringkat

- EI2403 - VLSI Design 2 Marks With AnswersDokumen23 halamanEI2403 - VLSI Design 2 Marks With AnswersAnand GvphBelum ada peringkat

- Wideband Microwave Amplifier DesignDokumen11 halamanWideband Microwave Amplifier DesignbaymanBelum ada peringkat

- Reducing MOSFET Consumption by Switched Biasing: 1 F Noise and PowerDokumen8 halamanReducing MOSFET Consumption by Switched Biasing: 1 F Noise and PowerkurabyqldBelum ada peringkat

- Pspice Model For Flicker Noise PDFDokumen11 halamanPspice Model For Flicker Noise PDFmikedelta28Belum ada peringkat

- Mixer Noise ASPDAC04Dokumen5 halamanMixer Noise ASPDAC04Ashish KapoorBelum ada peringkat

- Vlsi QBDokumen34 halamanVlsi QBKaviya dharshini S -ECE-028Belum ada peringkat

- Kamran J16Dokumen12 halamanKamran J16Nithya VelamBelum ada peringkat

- A Low Noise Amplifier Optimized For A GPS Receiver RF Front EndDokumen6 halamanA Low Noise Amplifier Optimized For A GPS Receiver RF Front EndterrozerBelum ada peringkat

- Design Techniques For Low Noise Cmos Operational AmplifiersDokumen4 halamanDesign Techniques For Low Noise Cmos Operational AmplifiersChandra Praveen MahalingamBelum ada peringkat

- Numerical Modeling of RF Noise in Scaled MOS DevicesDokumen8 halamanNumerical Modeling of RF Noise in Scaled MOS DevicesAnonymous jxm0WNS7QaBelum ada peringkat

- Chapter 4 - Analog Integrated Circuit Design by John ChomaDokumen92 halamanChapter 4 - Analog Integrated Circuit Design by John ChomaAriana Ribeiro LameirinhasBelum ada peringkat

- Technical Details: Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedDokumen7 halamanTechnical Details: Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedAbderrezzaq ZianeBelum ada peringkat

- 1987 Samsung SFET Data BookDokumen446 halaman1987 Samsung SFET Data BookAsad AhmedBelum ada peringkat

- Technical Details: Complementary Metal-Oxide-Semiconductor (CMOS) (Dokumen9 halamanTechnical Details: Complementary Metal-Oxide-Semiconductor (CMOS) (RailyBelum ada peringkat

- Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedDokumen7 halamanComplementary Metal-Oxide-Semiconductor (CMOS) (PronouncedArchana SadanandanBelum ada peringkat

- Complete High-Frequency Thermal Noise Modeling of Short-Channel MOSFETs and Design of 5.2-GHz Low Noise AmplifierDokumen10 halamanComplete High-Frequency Thermal Noise Modeling of Short-Channel MOSFETs and Design of 5.2-GHz Low Noise AmplifierWuBelum ada peringkat

- CMOSDokumen6 halamanCMOSالمؤسس عثمان بن ارطغرلBelum ada peringkat

- Research ArticleDokumen10 halamanResearch Articlerizal iskandarBelum ada peringkat

- Session 3: Solid State Devices I MOS and Fet (A) : Wednesday, Oct. 18 P.M. To SheratonDokumen2 halamanSession 3: Solid State Devices I MOS and Fet (A) : Wednesday, Oct. 18 P.M. To SheratonManda Praveen KumarBelum ada peringkat

- Harmonic Oscillators in CMOSA Tutorial OverviewDokumen16 halamanHarmonic Oscillators in CMOSA Tutorial OverviewJatinKumarBelum ada peringkat

- Rfic Unit 3: BY Blessina Preethi R, Asso, Professor, SvpcetDokumen31 halamanRfic Unit 3: BY Blessina Preethi R, Asso, Professor, SvpcetBlessina PreethiBelum ada peringkat

- Performance Very Low Frequency Filters: Design Considerations For HighDokumen4 halamanPerformance Very Low Frequency Filters: Design Considerations For Highmvmuthukumar88Belum ada peringkat

- Technical Details: Complementary Metal-Oxide-Semiconductor (CMOS)Dokumen4 halamanTechnical Details: Complementary Metal-Oxide-Semiconductor (CMOS)Testing toolsBelum ada peringkat

- From Wikipedia, The Free Encyclopedia: CMOS Inverter (NOT Logic Gate)Dokumen9 halamanFrom Wikipedia, The Free Encyclopedia: CMOS Inverter (NOT Logic Gate)bas_cbkBelum ada peringkat

- Subedi PaperDokumen7 halamanSubedi PaperLiviu BadeaBelum ada peringkat

- Wiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosDokumen10 halamanWiki Loves Love: Documenting Festivals and Celebrations of Love On Commons. Help Wikimedia and Win Prizes by Sending PhotosraoBelum ada peringkat

- Shyam Ac Performance of Nano ElectronicsDokumen30 halamanShyam Ac Performance of Nano Electronicsapi-3827000100% (1)

- A Narrow-Band CMOS FM Receiver Based On Single-Sideband Modulation IF FilteringDokumen8 halamanA Narrow-Band CMOS FM Receiver Based On Single-Sideband Modulation IF FilteringVivek RoyBelum ada peringkat

- LSK489 Application Note Preliminary DraftDokumen16 halamanLSK489 Application Note Preliminary DrafttarpinoBelum ada peringkat

- Design of CMOS Analog Integrated Circuits: Franco MalobertiDokumen52 halamanDesign of CMOS Analog Integrated Circuits: Franco MalobertiPrakashKumarRoutBelum ada peringkat

- Ac Performance of Nano Electronics Seminar Report On 2018-19Dokumen32 halamanAc Performance of Nano Electronics Seminar Report On 2018-19MusthafaBelum ada peringkat

- For Other Uses, See .: CMOS (Disambiguation)Dokumen11 halamanFor Other Uses, See .: CMOS (Disambiguation)Smitha KollerahithluBelum ada peringkat

- A 1.5V 1.5GHz CMOS LNADokumen16 halamanA 1.5V 1.5GHz CMOS LNAptt3iBelum ada peringkat

- Designing 1-V Op Amps Using Standard Digital CMOS TechnologyDokumen12 halamanDesigning 1-V Op Amps Using Standard Digital CMOS TechnologynikilquickBelum ada peringkat

- For Other Uses, See .: CMOS (Disambiguation)Dokumen10 halamanFor Other Uses, See .: CMOS (Disambiguation)Ashutosh DabasBelum ada peringkat

- Recent Trends in CMOS Low Noise Amplifiers: Abstract - This Paper Presents An Overview and Comparison of CMOS Low NoiseDokumen12 halamanRecent Trends in CMOS Low Noise Amplifiers: Abstract - This Paper Presents An Overview and Comparison of CMOS Low NoisemztanimBelum ada peringkat

- UNP NoiseDokumen12 halamanUNP Noisejofinjv3194Belum ada peringkat

- Graphene Transistors by Frank SchwierzDokumen10 halamanGraphene Transistors by Frank SchwierzshreypathakBelum ada peringkat

- Technical Details: Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedDokumen11 halamanTechnical Details: Complementary Metal-Oxide-Semiconductor (CMOS) (PronouncedsohilnkBelum ada peringkat

- FinFET Inverter Anlaysis PDFDokumen14 halamanFinFET Inverter Anlaysis PDFRakeshBelum ada peringkat

- 10.1007/978 3 642 34216 5 - 21Dokumen12 halaman10.1007/978 3 642 34216 5 - 21Sarmista SenguptaBelum ada peringkat

- A Low Phase Noise GM Boosted DTMOS VCO Desi 2018 Karbala International JournDokumen9 halamanA Low Phase Noise GM Boosted DTMOS VCO Desi 2018 Karbala International JournSAFA'A AL-HAREERIBelum ada peringkat

- Synopsis VCO BDCoEDokumen9 halamanSynopsis VCO BDCoEraymar2kBelum ada peringkat

- Layout Variations On LNADokumen4 halamanLayout Variations On LNArichbuggerBelum ada peringkat

- A 10 MW Inductorless, Broadband CMOS Low Noise Amplifier For 900 MHZ Wireless CommunicationsDokumen4 halamanA 10 MW Inductorless, Broadband CMOS Low Noise Amplifier For 900 MHZ Wireless CommunicationsWuBelum ada peringkat

- A Gm-Id Based Methodology For CMOS Analog DesignDokumen6 halamanA Gm-Id Based Methodology For CMOS Analog DesignDeep SaxenaBelum ada peringkat

- Bias Dependent Attenuation of Coplanar Transmission Lines On SiliconDokumen4 halamanBias Dependent Attenuation of Coplanar Transmission Lines On SiliconEssam KhaterBelum ada peringkat

- A 2.4-Ghz Low-Flicker-Noise Cmos Sub-Harmonic ReceiverDokumen11 halamanA 2.4-Ghz Low-Flicker-Noise Cmos Sub-Harmonic ReceiverdabalejoBelum ada peringkat

- Paper LC Vco SohiniDokumen5 halamanPaper LC Vco SohiniDr-Umakanta NandaBelum ada peringkat

- MOS Transistor Modeling For RF IC Design (Enz)Dokumen16 halamanMOS Transistor Modeling For RF IC Design (Enz)Sharabi.salahBelum ada peringkat

- RF Transistors StructuresDokumen26 halamanRF Transistors StructuresAlican UysalBelum ada peringkat

- 1996 - JSSC - A gmID Based Methodology For The Design of CMOS Analog Circuits and Application To The Synthesis of A SOI Micropower OTADokumen6 halaman1996 - JSSC - A gmID Based Methodology For The Design of CMOS Analog Circuits and Application To The Synthesis of A SOI Micropower OTALuật TrầnBelum ada peringkat

- Evaluating The Low-Frequency Power-Line Communications Channel in Rural North AmericaDokumen9 halamanEvaluating The Low-Frequency Power-Line Communications Channel in Rural North AmericamahijakmohitBelum ada peringkat

- Acoustic Characteristics of Noise Absorbing Barriers: Gleb Nazarov, Dmitry Nepryakhin, and Alexandr KomkinDokumen9 halamanAcoustic Characteristics of Noise Absorbing Barriers: Gleb Nazarov, Dmitry Nepryakhin, and Alexandr KomkinAtharv MarneBelum ada peringkat

- Application: Design For ProcessDokumen4 halamanApplication: Design For ProcessjaberyemeniBelum ada peringkat

- Microelectronic CircuitDokumen696 halamanMicroelectronic CircuitImtiaz AhmedBelum ada peringkat

- A Broadband Folded Gilbert Cell CMOS MixerDokumen6 halamanA Broadband Folded Gilbert Cell CMOS MixerMohammedIrshadAhBelum ada peringkat

- Noise in Nanoscale Semiconductor DevicesDari EverandNoise in Nanoscale Semiconductor DevicesTibor GrasserBelum ada peringkat

- Brocade ZoningDokumen34 halamanBrocade Zoningdenver_osbornBelum ada peringkat

- TCE SS CFP Emerging Signal Processing Techniques and Protocols For Interconnected Consumer ElectronicsDokumen2 halamanTCE SS CFP Emerging Signal Processing Techniques and Protocols For Interconnected Consumer ElectronicsMuhammad Senoyodha BrennafBelum ada peringkat

- Easy Data Exchange Via Festo Easyip: Festo Ag & Co - KGDokumen11 halamanEasy Data Exchange Via Festo Easyip: Festo Ag & Co - KGFFlipooxBelum ada peringkat

- HA-646 BrochureDokumen1 halamanHA-646 BrochureFelhazi AndreiBelum ada peringkat

- Install Guide For Raymarine E120 E80Dokumen58 halamanInstall Guide For Raymarine E120 E80costinosBelum ada peringkat

- EletronicsDokumen1 halamanEletronicsAlexandre Sette100% (1)

- JPR Java Programming 22412 Msbte Microproject - Msbte Micro Projects - I SchemeDokumen12 halamanJPR Java Programming 22412 Msbte Microproject - Msbte Micro Projects - I SchemeAtul GaikwadBelum ada peringkat

- Ber Analysis of 2X2 Mimo Spatial Multiplexing Under Awgn and Rician Channels For Different Modulations TechniquesDokumen15 halamanBer Analysis of 2X2 Mimo Spatial Multiplexing Under Awgn and Rician Channels For Different Modulations TechniquesKhairul NurzamBelum ada peringkat

- Interconnect Rating FlowDokumen5 halamanInterconnect Rating FlowShahzad AlviBelum ada peringkat

- Automatic TransmissionDokumen5 halamanAutomatic Transmissionolyga mgolBelum ada peringkat

- Tableau VM Tuning and Best PracticesDokumen6 halamanTableau VM Tuning and Best Practicessrikanth_4allBelum ada peringkat

- CAPE 2014 Unit 1 Computer Science P2Dokumen8 halamanCAPE 2014 Unit 1 Computer Science P2dnitehawk qBelum ada peringkat

- s3 in Ontap Best PracticesDokumen25 halamans3 in Ontap Best PracticesbuyoloBelum ada peringkat

- An Aquaculture Remote PH Monitoring SystemDokumen29 halamanAn Aquaculture Remote PH Monitoring SystemChimdi ChukwuBelum ada peringkat

- Fortigate Cookbook 504Dokumen220 halamanFortigate Cookbook 504regabriBelum ada peringkat

- PDF Edne Nov 2013Dokumen48 halamanPDF Edne Nov 2013torinomg100% (1)

- Protocol Dp25 Dp05 Dp500 Dp500lDokumen32 halamanProtocol Dp25 Dp05 Dp500 Dp500lRoStarBelum ada peringkat

- Epo 510 RG Log Files 0-00 En-UsDokumen10 halamanEpo 510 RG Log Files 0-00 En-UsabbuasherBelum ada peringkat

- Bus Impedance Matrix Building Algorithm Illustrated With An ExampleDokumen3 halamanBus Impedance Matrix Building Algorithm Illustrated With An ExampleLangelihle Xaba KingBelum ada peringkat

- 2015 - 2016 Questions (New Syllabus) Describe The Characteristics and Uses of Different Types of DVDDokumen2 halaman2015 - 2016 Questions (New Syllabus) Describe The Characteristics and Uses of Different Types of DVDYashodhaBelum ada peringkat

- Process ListDokumen3 halamanProcess ListAnonymous BJdOLuABBelum ada peringkat

- Black Box TechinquesDokumen5 halamanBlack Box TechinquesMEHJABEEN SAYYEDBelum ada peringkat

- Rock Smith ConfigurationDokumen20 halamanRock Smith ConfigurationRaúlÁlvarezMBelum ada peringkat

- Natural System VariablesDokumen68 halamanNatural System VariablesEVANGELION20150% (1)

- Labsheet 1Dokumen4 halamanLabsheet 1KarthikBelum ada peringkat

- AV Receiver: Owner'S Manual Manual de InstruccionesDokumen430 halamanAV Receiver: Owner'S Manual Manual de InstruccionesSebas SinBelum ada peringkat

- Kodak DirectView CR 500 - Diagnostics PDFDokumen211 halamanKodak DirectView CR 500 - Diagnostics PDFFélix Enríquez100% (1)

- UMTS RNC Product Description v1 04Dokumen82 halamanUMTS RNC Product Description v1 04tquanglongBelum ada peringkat