ADC Design

Diunggah oleh

muffassirHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

ADC Design

Diunggah oleh

muffassirHak Cipta:

Format Tersedia

International Conference on Emerging Technological Trends in Advanced Engineering Research [ICETT 2012], 2012 February 20-21.

Simple Neuron Circuit with Adjustable Weights and its Application to Neural Based ADC

Syed Muffassir M. S. Ali, Dr.Suhas S. Gajre

Abstract A neuron circuit design whose weights can be changed even after the fabrication is presented here. It is based on modified CMOS inverter synapses. Weights can be modified by changing the threshold voltage of the inverters. The application of this neuron model circuit design for the analog to digital converter has been implemented. The implementation has been done using CADENCE software VIRTUOSO tool using the 180 nm process technology for 1.8 V. Index Termsneuromorphic circuit design,analog VLSI,ADC.

I. INTRODUCTION ECENTLY there have been many implementations of the various neuron models starting from the simple formal neuron models[1] to the latest spiking neuron model based on mathematical equations[2],[3]. These implementation have been done keeping in mind to build some day a neurocomputer capable to perform the functions as that of the Human Brain. This trend got momentum after the pioneering work of C.Mead [4]. However for the implementation of the weights these neuron circuits use the Floating gate MOS transistors where the capacitance of the floating gate is used for weights. The poly silicon is used as capacitance in these Floating Gate MOS, so it requires larger area on the chip [5]. Also there has been implementation using the resistors for the weights [6]. But here also the weights once fabricated cannot be changed. Also the values are fixed after the fabrication process. C.K.Pham implemented the synapse circuits using the resistors. This circuit requires huge area because of the presence of resistors and the weights were fixed after the fabrication of the chip. So there is a need for less area and adjustable weight neuron circuit which is proposed in this paper. Since this neuron circuit is based on the simple formal model of the neuron it cannot be used to implement the neurocomputer rather can be used to realize the neural analog circuits because of its simplicity & less area required. We

suggest for the realization of neuro-computer spiking neuron model circuits should be used since they perfectly mimic the behavior of the human brain. The neural networks have been even used to implement the neural based analog circuits like the filter design ,analog multiplier , integrator and the ADC[7],[8],[9],[10]. For the implementation of the filter Rodriguez et al [11] used the floating gate MOS transistors. These circuits require large area because of the implementation of the capacitance using poly silicon floating gate capacitors. Also there have been few implementation of the neural based Analog to Digital Converter (ADC) [12],[13],[14]. These most implementations have been done using the symmetrical connections of the Hopfield Network. These circuits are highly complex and require huge hardware. Avitabile et al. [15] presented a class of neural networks with the nonsymmetrical connections in contrast to the Hopfield network. The implementation of feed-forward and nonsymmetrical network is reported by Mamoru. T et al. in [16]. Here the weights of the synapse were fixed by the value of the channel conductances of the MOS transistors. Also C. K. Pham implemented the ADC using the inverters but the presence of resistors made the circuit bulky. In this paper we have implemented the circuit for the ADC using our proposed neuron circuit. It requires less area and also the accuracy is better. The remainder of this paper is organized as follows. In Section II we have introduced the variable threshold CMOS inverter which is used for the neuron circuit model implementation. In Section III presents the modified novel neuron model circuits, where we can change the weights of the synapses using the control voltage Vc. In Section IV 3-bit neural based ADC is analyzed and implemented using the novel neural model presented. In Section V simulation results have been presented using the CADENCE software for 180 nm process technology. Finally in Section VI conclusions are drawn.

II. ADJUSTABLE THRESHOLD CMOS INVERTER

Manuscript received February 10, 2012. Syed Muffassir M. S. Ali is a student of Department of Electronics and Telecommunication Engineering, S. G. G. S Institute of Engineering and Technology, Nanded 431601 (Maharashtra) India. (email: muffassir@gmail.com) Dr.Suhas S. Gajre is with the Department of Electronics and Telecommunication Engineering, S. G. G. S Institute of Engineering and Technology, Nanded 431601 (Maharashtra) India.

The transconductance K is fixed by the process parameters and the W/L ratio of the MOS transistors. The threshold voltage is determined by this K ratio in the CMOS inverters. The K is given by

= Cox

(1)

ISBN : 978-93-80624-62-4

http://www.icett.com/

Baselios Mathews II College of Engineering, Kollam, Kerala, India.

International Conference on Emerging Technological Trends in Advanced Engineering Research [ICETT 2012], 2012 February 20-21.

Where W and L are the width and the length of the MOS transistors. The detailed analysis of the conventional CMOS inverter can be found in many CMOS design books.[17,[18],[19].The threshold voltage of this conventional CMOS inverter is given by [19]

(4) |+

(5)

(2)

=

Where

(3)

are the threshold voltages of PMOS

Where m is defined by eq (3). Thus from this analysis it is now clear that the same DC transfer characteristics as obtained by varying the m (as defined by eq(3)) can also be obtained by the control voltage Vc applied to this inverter without varying the W/L ratios. As the control voltage Vc is increased or decreased produces the same effect as the variation of the W/L ratios and further this can be done even when the chip is fabricated also.

and NMOS transistors respectively. are the transconductance parameters of the NMOS and PMOS respectively. If the threshold voltage of the CMOS inverter has to be changed we need to change the m given by (3) which requires W/L to be changed according to eq (1). So after fabrication it is not possible to change the threshold voltage of these conventional MOS transistors. A MOSFET whose threshold can be changed has been proposed by Suan-Wei et al in [20]. To change the threshold of the MOSFET we need here 7 MOS transistors. So to make CMOS inverter with this MOSFET we need 14 MOS transistors. For the parallel array the number of MOS transistors required will be 7 times greater than that would have been with the conventional MOS transistors. A better CMOS inverter with the adjustable threshold has been proposed by Z.Wang in [21]. Here we need only 3 MOS transistors to implement the adjustable threshold CMOS inverter. The detailed analysis is given in this paper so we refer the interested reader to this [21]. For a look the adjusted threshold of the CMOS inverter as shown in the below figure has Vth given by

III. MODIFIED SYNAPSE AND NEURON CIRCUIT There have been many implementation of the synapse circuit. But all of them require either a capacitor or resistor for the implementation of weights. Congo. K. Pham presented Synapse circuit using inverters [16]. In these implementations the weights were either fixed by the value of resistors or the conductances of the channel which could not be modified after the fabrication of the chip. In this paper we propose a modified synapse circuit having adjustable weights. This can be achieved just by changing the threshold of the CMOS inverters as introduced in previous section. Here also the weights are defined by the conductances of the channel i.e. W/L ratios. In addition the weights can be changed by the control voltage applied. Thus now it becomes possible to modify the weight by the control voltage. The below shown circuit in fig.(2) is a modified circuit of the neuron employing modified CMOS inverter synapses.

Fig. 1. Schematic representation of the modified inverter. Fig. 2 Schematic of the modified Neuron Circuit of 3 synapse CMOS

ISBN : 978-93-80624-62-4

http://www.icett.com/

Baselios Mathews II College of Engineering, Kollam, Kerala, India.

International Conference on Emerging Technological Trends in Advanced Engineering Research [ICETT 2012], 2012 February 20-21.

inverter.

based 3-but ADC.

From left the first 3 modified inverters are the synapses and the later 2 inverters are the Decision Making Amplifier which acts as the implementation of Hard Limiting Threshold Function. The threshold of this inverter can be varied by changing the Vc voltage. The common voltage Vout is determined when the current ( ) flowing through the NMOS is equal to the current ( ) flowing in NMOS transistors The parallel conductance of all the NMOS is gn+gn and all PMOS is gp then the vout is given by

Then = =

(6)

are given by

(7) (8)

The hard limiting threshold function is realized by the two cascaded CMOS inverters as

= 1 0

1/2 > 1/2

(9)

Here in the above fig. (2) we have connected the control voltage Vc .By changing this control voltage we can change the weights of the synapses. Also the cascaded decision making inverters need to change their threshold to make correct decisions so we connected same control voltage Vc. Also for more flexibility we can give different voltage but unnecessarily will increase the number of pins.

Fig. 3. Shematic of the modified ADC.

V. SIMULATION RESULTS IV. NEURAL BASED 3-BIT ADC The 3 bit modified circuit of the Analog to Digital Converter is shown in the fig. (3). It consists of the 3 neuron circuits as presented in previous section. The decision making amplifier output is given to the extra connected CMOS inverter for converting the output logic to the positive logic. Each neuron has the weights 4,2 & 1 respectively. The analog input is given to the CMOS inverter which has the weight 8. So every input to the neuron is either high or low level. The m can thus be given as We have designed and simulated the neural based ADC in 180nm process technology in CADENCE. The input voltage to the circuit was 1.8 V. The analog input to the inverter is a triangular wave of 20nsec period with delay time of 0nsec and rise and fall time equal to the 1nsec each. The modified CMOS inverter ratios were designed according to the weights needed and particularly the PMOS size was made 2.7 times greater than the NMOS to make the equal.The simulation results of the transient analysis for the period of 80nsec is shown in the fig (4).

(10)

The data is converted from MSB to LSB and the previous converted data are used for the next conversion. By using the control voltage Vc, The threshold of the inverter can be tuned to get the optimized output of the neural

ISBN : 978-93-80624-62-4

http://www.icett.com/

Baselios Mathews II College of Engineering, Kollam, Kerala, India.

International Conference on Emerging Technological Trends in Advanced Engineering Research [ICETT 2012], 2012 February 20-21.

REFERENCES

W. McCulloch and W. Pitts, A logical calculus of ideas immanent in nervous activity, Bulletin of Mathematical Biophysics, vol. 5, pp. 115113, 1943. [2] S.Mihalas and E.Niebur, A generalized linear integrate-and-fire neural model produces diverse spiking behaviors, Neural Computation 2009;21(3):704-18 [3] Izhikevich E.M., Simple model of spiking neurons, IEEE Transactions On Neural Networks, 14:1569-1572, 2003 [4] C. A. Mead, Analog VLSI and Neural Systems, Addison-Wesley, Reading, MA, 1989 [5] F. Kele, Low Voltage Low Power Neuron Circuit Design Based On Subthreshold FGMOS Transistors And XOR Implementation, 2010 XIth International Workshop on Symbolic and Numerical Methods, Modeling and Applications to Circuit Design, pp. 4-8, 2010. [6] C.-kha Pham and T. Universit, A novel synapses circuit and its application to a neural-based a/d converter, The 2001 IEEE International Symposium on Circuits and systems, vol. 3, pp. 6-9,2001. [7] E. Rodrguez-villegas, A. Yfera, and A. Rueda, A 1-V Micropower Log-Domain Integrator Based on FGMOS Transistors Operating in Weak Inversion, IEEE Journal of Solid State Circuits, vol. 39, NO. 1, pp. 256-259, 2004. [8] E. Rodriguez-villegas, A. Rueda, and A. Yufera, A 1.5V 23MHz Low Power FGMOS Filter, ICCDCS, vol. 3, no. 1, pp. 337-340,2008. [9] S. Vlassis, Analogue squarer and multiplier based on floating-gate MOS transistors, Electronics Letters, vol. 34, no. 9, pp. 825-826, 1998. [10] E. Rodriguez, A. Yhfera, and A. Rueda, A g m -C FLOATING-GATE MOS INTEGRATOR, ISCAS-2000, pp. 153-156, 2000. [11] E. Rodriguez-villegas, A. Yfera, and A. Rueda, A 1 . 25-V Micropower G m - C Filter Based on FGMOS Transistors Operating in Weak Inversion, IEEE Journal of Solid State Circuits,vol. 39, no. 1, pp. 100-111, 2004. [12] B. J. Sheu, Design of a Neural-Based A / D Converter Using Modified Hopfield Network, IEEE Journal of Solid State Circuits , vol. 24, no. 4, 1989. [13] David W. Tank and John J. Hopfield, Simple neural optimization networks: an A/D converter, signal decision circuit, and a linear programming circuit, IEEE Circuit and Systems , vol. CAS-33, pp. 553541 ,May 1986 [14] Jen-Dong Yuh and Robert W. Newcomb, A multilevel neural network for A/D conversion, IEEE Neural Networks,vol-4,pp.470-483,May 1986 [15] G. Avitabile, M. Forti, S. Manetti and M. Marini, On a class of nonsymmetrical neural networks with application to ADC, IEEE Circuit and Systems, vol.CAS 38 pp. 202-209, Feb. 1991 [16] C.k.Pham,M.Tanaka and K.Shono, A simple 6-bit neural-based a / d converter employing only cmos inveters, ISCAS 96, pp. 357-360,1996 [17] Allen,P. E. and Holberg,D. R., CMOS Analog Circuit Design, Holt,Rinehard and Winston, New York, 1987. [18] Franco Maloberiti,Analog Design for CMOS VLSI Systems, Kluwer Adademic Publishers,2001. [19] Weste N.H and Eshragian. K, Principles of CMOS VLSI Design, Addison-Wesley,Reading,1998. [20] S.-wei Tsay and R. W. Newcomb, An adjustable threshold mosfet *, Design, pp. 1270-1272, 1992. [21] Z.Wang, Novel CMOS inverter with linearly adjustable threshold voltage using only 3 MOS transistors. Microelectronics Journal, vol:22, Elsevier Science Publishers Ltd,England.pp:75-79, 1991. [1]

Fig. 4 . Transient analysis output waveforms of the modified ADC.

VI. CONCLUSION Neuron Circuit has been designed and presented here whose weights can be altered by the control voltage. Also the neural based 3-bit ADC has been successfully implemented using the proposed neuron model. This neuron circuit can be used to implement other neural based analog circuits.

ACKNOWLEDGMENT Syed Muffassir M. S. Ali would like to thank Shoeb M.Khan of Hyundai Ltd for his support during this implementation.

ISBN : 978-93-80624-62-4

http://www.icett.com/

Baselios Mathews II College of Engineering, Kollam, Kerala, India.

International Conference on Emerging Technological Trends in Advanced Engineering Research [ICETT 2012], 2012 February 20-21.

Syed Muffassir M. S. Ali received B.E degree electronics and telecommunication engineering from R.T.M Nagpur University,Nagpur in 2006.Presently he is working towards M.Tech degree in electronics engineering from S.G. G. S Institute of Engineering and technology,Nanded(India). From 2007-2009 he worked at Rolta India Ltd,Mumbai as Production Executive. From 2009-10 as a Project Manager at Hospifix, Mumbai. His research interest includes low power neuromorphic circuits design, analog VLSI and floating gate transistors. Dr.Suhas S.Gajre received the B.E & M.E degrees in Electronics from SGGS College of Engineering and Technology,Nanded. He received Ph.D degree from Indian Institute of Technology, Delhi. He won the First Prize in All India Student Academic Meet in Computer Science in AI section for a technical paper and also a second prize in the National Level Symposium on Computer Science for students in Coimbatore in 1991.Currently he is an Assistant Professor in SGGS IE & T, Nanded. His research interest includes Biomedical Signal Processing, Electronic Devices and Circuits, Analog VLSI Design.

ISBN : 978-93-80624-62-4

http://www.icett.com/

Baselios Mathews II College of Engineering, Kollam, Kerala, India.

Anda mungkin juga menyukai

- A Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryDari EverandA Heartbreaking Work Of Staggering Genius: A Memoir Based on a True StoryPenilaian: 3.5 dari 5 bintang3.5/5 (231)

- The Sympathizer: A Novel (Pulitzer Prize for Fiction)Dari EverandThe Sympathizer: A Novel (Pulitzer Prize for Fiction)Penilaian: 4.5 dari 5 bintang4.5/5 (119)

- Never Split the Difference: Negotiating As If Your Life Depended On ItDari EverandNever Split the Difference: Negotiating As If Your Life Depended On ItPenilaian: 4.5 dari 5 bintang4.5/5 (838)

- Devil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaDari EverandDevil in the Grove: Thurgood Marshall, the Groveland Boys, and the Dawn of a New AmericaPenilaian: 4.5 dari 5 bintang4.5/5 (265)

- The Little Book of Hygge: Danish Secrets to Happy LivingDari EverandThe Little Book of Hygge: Danish Secrets to Happy LivingPenilaian: 3.5 dari 5 bintang3.5/5 (399)

- Grit: The Power of Passion and PerseveranceDari EverandGrit: The Power of Passion and PerseverancePenilaian: 4 dari 5 bintang4/5 (587)

- The World Is Flat 3.0: A Brief History of the Twenty-first CenturyDari EverandThe World Is Flat 3.0: A Brief History of the Twenty-first CenturyPenilaian: 3.5 dari 5 bintang3.5/5 (2219)

- The Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifeDari EverandThe Subtle Art of Not Giving a F*ck: A Counterintuitive Approach to Living a Good LifePenilaian: 4 dari 5 bintang4/5 (5794)

- Team of Rivals: The Political Genius of Abraham LincolnDari EverandTeam of Rivals: The Political Genius of Abraham LincolnPenilaian: 4.5 dari 5 bintang4.5/5 (234)

- Rise of ISIS: A Threat We Can't IgnoreDari EverandRise of ISIS: A Threat We Can't IgnorePenilaian: 3.5 dari 5 bintang3.5/5 (137)

- Shoe Dog: A Memoir by the Creator of NikeDari EverandShoe Dog: A Memoir by the Creator of NikePenilaian: 4.5 dari 5 bintang4.5/5 (537)

- The Emperor of All Maladies: A Biography of CancerDari EverandThe Emperor of All Maladies: A Biography of CancerPenilaian: 4.5 dari 5 bintang4.5/5 (271)

- The Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You AreDari EverandThe Gifts of Imperfection: Let Go of Who You Think You're Supposed to Be and Embrace Who You ArePenilaian: 4 dari 5 bintang4/5 (1090)

- Her Body and Other Parties: StoriesDari EverandHer Body and Other Parties: StoriesPenilaian: 4 dari 5 bintang4/5 (821)

- The Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersDari EverandThe Hard Thing About Hard Things: Building a Business When There Are No Easy AnswersPenilaian: 4.5 dari 5 bintang4.5/5 (344)

- Hidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RaceDari EverandHidden Figures: The American Dream and the Untold Story of the Black Women Mathematicians Who Helped Win the Space RacePenilaian: 4 dari 5 bintang4/5 (890)

- Elon Musk: Tesla, SpaceX, and the Quest for a Fantastic FutureDari EverandElon Musk: Tesla, SpaceX, and the Quest for a Fantastic FuturePenilaian: 4.5 dari 5 bintang4.5/5 (474)

- The Unwinding: An Inner History of the New AmericaDari EverandThe Unwinding: An Inner History of the New AmericaPenilaian: 4 dari 5 bintang4/5 (45)

- The Yellow House: A Memoir (2019 National Book Award Winner)Dari EverandThe Yellow House: A Memoir (2019 National Book Award Winner)Penilaian: 4 dari 5 bintang4/5 (98)

- On Fire: The (Burning) Case for a Green New DealDari EverandOn Fire: The (Burning) Case for a Green New DealPenilaian: 4 dari 5 bintang4/5 (73)

- Facet Electronica 1Dokumen191 halamanFacet Electronica 1Joaquin Platero Ryū100% (4)

- Reading Teacher ExamDokumen43 halamanReading Teacher Examcboosalis100% (1)

- Evidence-Based Clinical Voice AssessmentDokumen17 halamanEvidence-Based Clinical Voice AssessmentkaaanyuBelum ada peringkat

- Ge3 Module (Aps Approved Module)Dokumen143 halamanGe3 Module (Aps Approved Module)Jan Matthew Albesa100% (1)

- LipidsDokumen36 halamanLipidsQueng Eledia100% (1)

- Observational Learning PDFDokumen4 halamanObservational Learning PDFMark neil a. GalutBelum ada peringkat

- Design of Low Voltage Low Power Neuromorphic Circuits Using CADENCEDokumen83 halamanDesign of Low Voltage Low Power Neuromorphic Circuits Using CADENCEmuffassir100% (1)

- Neuromorphic Circuits Technical ReportDokumen13 halamanNeuromorphic Circuits Technical Reportmuffassir100% (2)

- Design of Low Voltage Low Power Neuromorphic SystemsDokumen54 halamanDesign of Low Voltage Low Power Neuromorphic SystemsmuffassirBelum ada peringkat

- Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™Dokumen20 halamanDa Vinci™ Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™ Da Vinci™muffassirBelum ada peringkat

- Ultra Low Voltage Low PowerDokumen30 halamanUltra Low Voltage Low PowermuffassirBelum ada peringkat

- MATLAB DSP Lab ManualDokumen35 halamanMATLAB DSP Lab ManualTapasRoutBelum ada peringkat

- OMNETDokumen20 halamanOMNETmuffassir100% (1)

- Patterns of Motion and Friction Lesson Plan GGDokumen3 halamanPatterns of Motion and Friction Lesson Plan GGMatt Jerrard Rañola RoqueBelum ada peringkat

- Capitulo 3 y 4 de The Death of ExpertiseDokumen64 halamanCapitulo 3 y 4 de The Death of ExpertiseLAURA SOFIA PERDOMO PARDOBelum ada peringkat

- Virtual Reality Exposure Therapy for AerophobiaDokumen6 halamanVirtual Reality Exposure Therapy for AerophobiaOMAIMA QAZIBelum ada peringkat

- 2020055.MSM Eee312l Lab 08Dokumen5 halaman2020055.MSM Eee312l Lab 08Mahmud SazzadBelum ada peringkat

- Community, Engagement, Solidarity and CitizenshipDokumen10 halamanCommunity, Engagement, Solidarity and CitizenshipCyrrha Fe QuesabaBelum ada peringkat

- INGLESDokumen20 halamanINGLESNikollay PeñaBelum ada peringkat

- College of Fine Arts: Karnataka Chitrakala ParishathDokumen2 halamanCollege of Fine Arts: Karnataka Chitrakala Parishathnandan R TBelum ada peringkat

- TR Band Post Procedure Physician Order Set 042512Dokumen1 halamanTR Band Post Procedure Physician Order Set 042512effitaBelum ada peringkat

- Analyzing Data Case StudiesDokumen3 halamanAnalyzing Data Case StudiesankitaBelum ada peringkat

- Katamba 1993 # Morphology # LIBDokumen178 halamanKatamba 1993 # Morphology # LIBLuciano ReBelum ada peringkat

- BC Roy Engineering College ProfileDokumen2 halamanBC Roy Engineering College ProfileDeepBelum ada peringkat

- High School Resume ValedictorianDokumen2 halamanHigh School Resume ValedictorianMaite Rocio VBelum ada peringkat

- fs4 Episode 2Dokumen3 halamanfs4 Episode 2api-309998163100% (1)

- 2b or Not 2bDokumen11 halaman2b or Not 2bDammar Singh SaudBelum ada peringkat

- Ficha Técnica Disk On ChipDokumen21 halamanFicha Técnica Disk On ChipCAGERIGOBelum ada peringkat

- Nusing Skills Output (Nso)Dokumen3 halamanNusing Skills Output (Nso)leroux2890Belum ada peringkat

- Ensuring Safe Learning Spaces Under COVID 19Dokumen2 halamanEnsuring Safe Learning Spaces Under COVID 19Prenrose Deferia PiaBelum ada peringkat

- CSM JDDokumen2 halamanCSM JDAushta LakshmiPriyaBelum ada peringkat

- Andrea Zakaib Resume June 16 Pathways To EducationDokumen1 halamanAndrea Zakaib Resume June 16 Pathways To Educationapi-307442547Belum ada peringkat

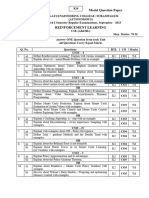

- RL Model Question PaperDokumen1 halamanRL Model Question Paperspiderman423423Belum ada peringkat

- 2021 Urology Residency Match StatisticsDokumen6 halaman2021 Urology Residency Match Statisticsnarutota181Belum ada peringkat

- 10.4324 9780203424605 PreviewpdfDokumen51 halaman10.4324 9780203424605 PreviewpdfailynBelum ada peringkat

- Free Area & Perimeter Task Cards: Promoting Success For You and Your Students!Dokumen11 halamanFree Area & Perimeter Task Cards: Promoting Success For You and Your Students!api-507043127Belum ada peringkat

- Banning Gay Adoption Harms ChildrenDokumen8 halamanBanning Gay Adoption Harms ChildrenTKILLETTE100% (2)