Optimization Technique Sram 45nm Cse

Diunggah oleh

prateeka100Deskripsi Asli:

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Optimization Technique Sram 45nm Cse

Diunggah oleh

prateeka100Hak Cipta:

Format Tersedia

P3 (Power-Performance-Process) Optimization of Nano-CMOS SRAM using Statistical DOE-ILP

Garima Thakral1, Saraju P. Mohanty2, Dhruva Ghai3, Dhiraj K. Pradhan4 Computer Science and Engineering, University of North Texas, USA.1,2,3 Department of Computer Science, University of Bristol, UK.4 Email-ID: saraju.mohanty@unt.edu2, pradhan@compsci.bristol.ac.uk4.

Acknowledgment: This research is supported in part by NSF awards CCF-0702361 and CNS-0854182. VLSI Design and CAD Lab

1

Summary and Conclusions

A

novel design flow is presented for simultaneous P3 (power minimization, performance maximization and process variation tolerance) optimization of nano-CMOS circuits. For demonstration of the effectiveness of the flow, a 45 nm single-ended 7-transistor SRAM is used as example circuit. The SRAM cell is subjected to a dual-VTh assignment based on a novel statistical Design of Experiments-Integer Linear Programming (DOE-ILP) approach. Experimental results show 44.2% power reduction (including leakage) and 43.9% increase in the read static noise margin compared to the baseline design. The process variation analysis of the optimized cell is carried out considering the variability in 12 parameters.

VLSI Design and CAD Lab

2

P3 (Power-Performance-Process) Optimization of Nano-CMOS SRAM using Statistical DOE-ILP

Garima Thakral1, Saraju P. Mohanty2, Dhruva Ghai3, and Dhiraj K. Pradhan4 Department of Computer Science and Engineering, University of North Texas, USA.1,2,3 Department of Computer Science, University of Bristol, UK.4 Email-ID: saraju.mohanty@unt.edu2, pradhan@compsci.bristol.ac.uk4.

. An 8 8 SRAM array is constructed using P3 optimized SRAM cell to study the feasibility of P3-optimal SRAM array construction. Algorithm 1 discusses a well-established process-level technique, called dual-VTh (threshold voltage) which is used for reduction of power consumption. It is a very important to choose appropriate transistors for high-VTh assignment, thus, the statistical DOE-ILP methodology is proposed. Further, ILP is useful for optimizing the linear objective function subjected to constraints and obtain a bound on the optimal value to solve the predictive equations formed using DOE. Minimum sized transistors are taken for the baseline design.

Abstract

In this research paper, a novel design flow is presented for simultaneous P3 (power minimization, performance maximization and process variation tolerance) optimization of nano-CMOS circuits. The SRAM cell is subjected to a dual-VTh assignment based on a novel statistical Design of Experiments-Integer Linear Programming (DOE-ILP) approach. A 45nm single-ended 7-transistor SRAM is used as example circuit. Experimental results show 44.2% power reduction (including leakage) and 43.9% increase in the read static noise margin compared to the baseline design. The process variation analysis of the optimized cell is carried out considering the variability effect in 12 device parameters.

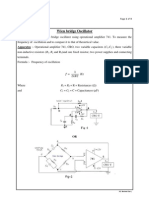

Design of Seven Transistor SRAM

The Proposed Methodology for P3 Optimality

The optimized butterfly curve is shown in Fig. 9(b)

Introduction, Motivation, and Contributions

In case of nanoscale circuit maintaining power, performance and process variation simultaneously becomes a major design challenge. Different design methods have been proposed like decrease in supply voltage, which reduces the dynamic power quadratic ally and reduces the leakage power linearly. However, substantial problems have been noted when the traditional six-transistor. SRAM cell is subjected to ultra-low voltage supply as it gives poor stability. In this paper a well-established process-level technique, called dual-VTh (threshold voltage) is used for reduction of power consumption. Read static noise margin (SNM) is defined as the minimum DC noise voltage which is required to flip the state of the SRAM cell during the read operation. The read SNM here is treated as a measure of performance.

The baseline 7-transistor SRAM cell is shown in Figure 3. The SRAM cell operates on a single bit line instead of the traditional two bit lines as in case of 6-transistor SRAM cell performing both read and write operations.

Power and SNM Measurement

Figure 10 shows the comparison of baseline and P3 optimized SRAM cell power and SNM for various values of Vdd.

Statistical DOE-ILP Optimization Algorithm

Fig. (a) shows the effect of process variations on the butterfly curve of the P3 optimized SRAM. Fig. (b) shows the distributions for SNM High and SNM Low extracted from the Monte Carlo simulations. SNM Low is treated as the actual SNM. Fig. (c) shows the distribution of average power of the P3 optimized SRAM cell under process variations.

Summary, Conclusions, and Future Works

A statistical DOE-ILP approach has been presented in this paper for simultaneous P3 optimization of SRAM cell. As part of extension of this research, a P4 optimal methodology is under consideration, where the 4th P would be parasitics. Thermal effects will also be incorporated in the future which will lead to what is envisioned as P4VT optimal; V stands for voltage and T stand for temperature. Also, array-level optimization of SRAM with mismatch and process variation will be considered as part of the design flow.

This table below presents that the dual- VTh assignment in SRAM shows 44.2% power reduction and 43.9% increase in read SNM over the baseline design. Figure 1 presents novel design flow for P3optimal SRAM with reduced power dissipation, increased performance (i.e. SNM), and processvariation awareness.

This research is supported in part by NSF awards CCF-0702361 and CNS-0854182

VLSI Design and CAD Laboratory (VDCL)

Anda mungkin juga menyukai

- Statistical DOE-ILP Based P3 Optimization of Nano-CMOS SRAMDokumen30 halamanStatistical DOE-ILP Based P3 Optimization of Nano-CMOS SRAMPremkumar ChandhranBelum ada peringkat

- A Combined DOE-ILP Based Power and Read Stability Optimization in Nano-CMOS SRAMDokumen6 halamanA Combined DOE-ILP Based Power and Read Stability Optimization in Nano-CMOS SRAMPrateek SinghalBelum ada peringkat

- Low Power SRAM PresentationDokumen15 halamanLow Power SRAM PresentationRekha KumariBelum ada peringkat

- Static-Noise-Margin Analysis of Modified 6T SRAM Cell During Read OperationDokumen5 halamanStatic-Noise-Margin Analysis of Modified 6T SRAM Cell During Read OperationidescitationBelum ada peringkat

- Bicta2012 Submission 94Dokumen23 halamanBicta2012 Submission 94Gurinder Pal SinghBelum ada peringkat

- Comparative Static Leakage Power Analysis of 4T and 6T SRAM CellsDokumen14 halamanComparative Static Leakage Power Analysis of 4T and 6T SRAM CellsKumarak Kannan TBelum ada peringkat

- 6Tvs7T Sram ComparisonDokumen5 halaman6Tvs7T Sram ComparisonPrateek AgrawalBelum ada peringkat

- A Highly Stable 8T SRAM Cell: P.Rama Koteswara Rao and D.Vijaya KumarDokumen6 halamanA Highly Stable 8T SRAM Cell: P.Rama Koteswara Rao and D.Vijaya KumarRakeshconclaveBelum ada peringkat

- Design Simulation and Analysis of 5T-Sram Cell Using Different FoundriesDokumen6 halamanDesign Simulation and Analysis of 5T-Sram Cell Using Different FoundriesPreeti SinghBelum ada peringkat

- Hybrid-Type CAM Design For Both Power and Performance EfficiencyDokumen10 halamanHybrid-Type CAM Design For Both Power and Performance EfficiencyRavi Tej GunisettyBelum ada peringkat

- Manage Enhancing Energy G.sakanaDokumen10 halamanManage Enhancing Energy G.sakanaBESTJournalsBelum ada peringkat

- Performance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDokumen7 halamanPerformance Evaluation of 6T, 7T & 8T SRAM at 180 NM TechnologyDr-Sanjeev KashyapBelum ada peringkat

- 15 - Conclusion and Future ScopeDokumen5 halaman15 - Conclusion and Future ScopeMel Vin PinBelum ada peringkat

- Design and VLSI Implementation of 8 MB Low Power SRAM in 90nmDokumen10 halamanDesign and VLSI Implementation of 8 MB Low Power SRAM in 90nmcnnprem_eeeBelum ada peringkat

- Low Power Sram ThesisDokumen5 halamanLow Power Sram ThesisBestWriteMyPaperWebsiteSingapore100% (2)

- Transistor Sizing of Energy-Delay - Efficient CircuitsDokumen7 halamanTransistor Sizing of Energy-Delay - Efficient CircuitsDaveMartoneBelum ada peringkat

- Hybrid Cache 2Dokumen6 halamanHybrid Cache 2ddomjaniBelum ada peringkat

- Improved Stability SRAM Design For Low Power ApplicationsDokumen5 halamanImproved Stability SRAM Design For Low Power ApplicationsInternational Journal of Application or Innovation in Engineering & ManagementBelum ada peringkat

- Sram Utilization and Power Consumption Analysis For Low Power ApplicationsDokumen9 halamanSram Utilization and Power Consumption Analysis For Low Power ApplicationsHarshit RBelum ada peringkat

- Tcam 3Dokumen5 halamanTcam 3Rugada ChaitanyaBelum ada peringkat

- Optimized CAM DesignDokumen6 halamanOptimized CAM DesignIJMERBelum ada peringkat

- Tappered Buffers Literature ReviewDokumen5 halamanTappered Buffers Literature ReviewZulfiqar AliBelum ada peringkat

- Low Power SRAM Project - Kushal 18ecu011 - Parth 18ecu016Dokumen17 halamanLow Power SRAM Project - Kushal 18ecu011 - Parth 18ecu016Parth BathlaBelum ada peringkat

- Sram - Power DissipationDokumen5 halamanSram - Power DissipationPromit MandalBelum ada peringkat

- Low Power SramDokumen5 halamanLow Power SramPromit MandalBelum ada peringkat

- Final ProjectDokumen5 halamanFinal Projectnksharma.naveen1855Belum ada peringkat

- 8T Paper WTCM FinalDokumen11 halaman8T Paper WTCM Finaldeberjeet ushamBelum ada peringkat

- Modeling andDokumen9 halamanModeling andSibi ManojBelum ada peringkat

- 7T Security Oriented SRAM Cell Reduces Power Analysis VulnerabilitiesDokumen5 halaman7T Security Oriented SRAM Cell Reduces Power Analysis VulnerabilitiesUma MahiBelum ada peringkat

- Analysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghDokumen5 halamanAnalysis of Low Power 6T SRAM Using 45 NM Technology: Shatrughan SinghShruti DasBelum ada peringkat

- A Novel Approach To Design SRAM Cells For Low LeakDokumen13 halamanA Novel Approach To Design SRAM Cells For Low LeakАндрей ГрозинBelum ada peringkat

- Design and Implementation of S R Flip Flop For Efficient Power Using CMOS 90nm TechnologyDokumen4 halamanDesign and Implementation of S R Flip Flop For Efficient Power Using CMOS 90nm TechnologyijsretBelum ada peringkat

- Design of 6T-SRAM Cell Using Dual Threshold Voltage TransistorDokumen4 halamanDesign of 6T-SRAM Cell Using Dual Threshold Voltage TransistorAbhijeet KumarBelum ada peringkat

- Saun 2019 IOP Conf. Ser. Mater. Sci. Eng. 561 012093 PDFDokumen10 halamanSaun 2019 IOP Conf. Ser. Mater. Sci. Eng. 561 012093 PDFShruti DasBelum ada peringkat

- Modeling combined-cycle power plants for simulation of frequency excursionsDokumen1 halamanModeling combined-cycle power plants for simulation of frequency excursionsAbdulrahmanBelum ada peringkat

- Maximum Power Estimation 1Dokumen4 halamanMaximum Power Estimation 1erhemantkumar1987Belum ada peringkat

- Chen DATE 2017Dokumen6 halamanChen DATE 2017Sumit DiwareBelum ada peringkat

- Design Techniques and Test Methodology For Low-Power TcamsDokumen14 halamanDesign Techniques and Test Methodology For Low-Power TcamsNaga KarthikBelum ada peringkat

- Accurate Calculation of Fault Currents in Complex Power SystemsDokumen2 halamanAccurate Calculation of Fault Currents in Complex Power SystemsRamprasadPandaBelum ada peringkat

- 6t Sram ThesisDokumen8 halaman6t Sram Thesisfjdqvrcy100% (2)

- Graph Theory and GA Optimize Distribution LossDokumen8 halamanGraph Theory and GA Optimize Distribution LossIam SriBelum ada peringkat

- Design of Low Power Sram: Presentation OnDokumen31 halamanDesign of Low Power Sram: Presentation Ondhanaji pawarBelum ada peringkat

- MTJ-Based Nonvolatile 9T SRAM CellDokumen5 halamanMTJ-Based Nonvolatile 9T SRAM CellidescitationBelum ada peringkat

- Numerical Arc Model Parameter Extraction For SF6 Circuit PDFDokumen5 halamanNumerical Arc Model Parameter Extraction For SF6 Circuit PDFAndré LuizBelum ada peringkat

- Analysis of Write Power Consumption For Single Gate and Dual Gate MOS Based SRAMDokumen6 halamanAnalysis of Write Power Consumption For Single Gate and Dual Gate MOS Based SRAMresearchinventyBelum ada peringkat

- Low Power Sram Design Using Block PartitioningDokumen4 halamanLow Power Sram Design Using Block PartitioningesatjournalsBelum ada peringkat

- High Speed Applications of Lower Power SRAM Cells: Akansha Lal (2k21/VLS/03) Shweta (2K21/VLS/18)Dokumen2 halamanHigh Speed Applications of Lower Power SRAM Cells: Akansha Lal (2k21/VLS/03) Shweta (2K21/VLS/18)shwetabhagatBelum ada peringkat

- Switching Characteristics of Generalized Array Multiplier Architectures and Their Applications To Low Power DesignDokumen23 halamanSwitching Characteristics of Generalized Array Multiplier Architectures and Their Applications To Low Power Designanon_100122661Belum ada peringkat

- Transformer Modeling in Atp EmtpDokumen6 halamanTransformer Modeling in Atp Emtpmspd2003Belum ada peringkat

- Analysis of Power Efficient Sram Cell For Portable Devices: Swaroop Kumar K, Shabirahmed B J, Narendra K, Asha G HDokumen9 halamanAnalysis of Power Efficient Sram Cell For Portable Devices: Swaroop Kumar K, Shabirahmed B J, Narendra K, Asha G HerpublicationBelum ada peringkat

- International Journal of Engineering Research and DevelopmentDokumen6 halamanInternational Journal of Engineering Research and DevelopmentIJERDBelum ada peringkat

- Three Phase PWM Rectifier ThesisDokumen7 halamanThree Phase PWM Rectifier Thesisalanacartwrightnorman100% (2)

- Analysis of SRAM Bitcells Using Ultralow-Voltage Schmitt-Trigger Based DesignDokumen5 halamanAnalysis of SRAM Bitcells Using Ultralow-Voltage Schmitt-Trigger Based DesignerpublicationBelum ada peringkat

- Eec118s11 Lab6Dokumen6 halamanEec118s11 Lab6vamsi krishnaBelum ada peringkat

- Accurate Power-Analysis Techniques Support Smart SOC-design ChoicesDokumen4 halamanAccurate Power-Analysis Techniques Support Smart SOC-design ChoicesSaurabh KumarBelum ada peringkat

- A Low-Voltage Micropower Asynchronous Multiplier With Shift-Add Multiplication ApproachDokumen11 halamanA Low-Voltage Micropower Asynchronous Multiplier With Shift-Add Multiplication ApproachPradeep ChandraBelum ada peringkat

- Analog Circuit Sizing Using Adaptive Worst-Case Parameters SetsDokumen5 halamanAnalog Circuit Sizing Using Adaptive Worst-Case Parameters SetswoshisimoxBelum ada peringkat

- Calculation of Short Circuit Currents in Overhead Ground Wires Using EMTP/ATPDokumen6 halamanCalculation of Short Circuit Currents in Overhead Ground Wires Using EMTP/ATPAnonymous mcCJYBoBelum ada peringkat

- 2006 Electrical-Engineering1 RahimpourDokumen6 halaman2006 Electrical-Engineering1 Rahimpourval111Belum ada peringkat

- High-Performance D/A-Converters: Application to Digital TransceiversDari EverandHigh-Performance D/A-Converters: Application to Digital TransceiversBelum ada peringkat

- Clock DividersDokumen19 halamanClock Dividersapi-376268992% (12)

- DTU Times InterviewvDokumen4 halamanDTU Times Interviewvprateeka100Belum ada peringkat

- 6Tvs7T Sram ComparisonDokumen5 halaman6Tvs7T Sram ComparisonPrateek AgrawalBelum ada peringkat

- Xilinx VHDL Test Bench Tutorial - 2.0Dokumen17 halamanXilinx VHDL Test Bench Tutorial - 2.0indrajeetkumarBelum ada peringkat

- Operational Amplifier 741 As Wein Bridge Oscillator 1Dokumen4 halamanOperational Amplifier 741 As Wein Bridge Oscillator 1Deepak SharmaBelum ada peringkat

- Chemical Leasing Within Industrial and Service Sector Cleaning OperationsDokumen61 halamanChemical Leasing Within Industrial and Service Sector Cleaning OperationsАлександр ПодорожникBelum ada peringkat

- 2 Tables Charts Review PDFDokumen71 halaman2 Tables Charts Review PDFCloie ChavezBelum ada peringkat

- G11 - Characteristics, Processes, and Ethics of ResearchDokumen16 halamanG11 - Characteristics, Processes, and Ethics of Researchsoru riiruBelum ada peringkat

- Thesis (From Curriculum Reform To Classroom Practice) 2Dokumen448 halamanThesis (From Curriculum Reform To Classroom Practice) 2poiu100% (1)

- Silent Sound TechnologyDokumen20 halamanSilent Sound TechnologySuman Savanur100% (3)

- 9-7-23... f126 A-F127... cf-3625... Stats... QueDokumen6 halaman9-7-23... f126 A-F127... cf-3625... Stats... Queindian kingBelum ada peringkat

- AN5377 R 6Dokumen8 halamanAN5377 R 6JhonattanIsaacBelum ada peringkat

- Inquiry MethodDokumen16 halamanInquiry Methodarthur the great50% (2)

- CRISC Day Wise TOC: Day 1: Domain 1: IT Risk IdentificationDokumen2 halamanCRISC Day Wise TOC: Day 1: Domain 1: IT Risk IdentificationDeepak JhaBelum ada peringkat

- Modifiable Areal Unit ProblemDokumen5 halamanModifiable Areal Unit Problemisabella343Belum ada peringkat

- UntitledDokumen37 halamanUntitledJanna AlisacaBelum ada peringkat

- Factor Influencing Investment DecisionDokumen19 halamanFactor Influencing Investment Decisiondashora8Belum ada peringkat

- EY Digital M&A StrategyDokumen20 halamanEY Digital M&A StrategyYaasBelum ada peringkat

- Historical TooningDokumen294 halamanHistorical TooningDiana RădulescuBelum ada peringkat

- Basic Terms in StatisticsDokumen7 halamanBasic Terms in StatisticsKat ArenaBelum ada peringkat

- Understanding Ball's policy cycle approachDokumen31 halamanUnderstanding Ball's policy cycle approachnascimentoalagoas100% (4)

- Complementary and Alternative Medicine Clinic DesignDokumen176 halamanComplementary and Alternative Medicine Clinic Designnatasa2575% (4)

- Research Requirement MSN-AHDokumen7 halamanResearch Requirement MSN-AHangelica javierBelum ada peringkat

- GE PC Course SyllabusDokumen9 halamanGE PC Course SyllabusAine CebedoBelum ada peringkat

- Midterm SolutionDokumen6 halamanMidterm SolutionbrsbyrmBelum ada peringkat

- "One Day I Want To Own A Football Club in Italy", Rinita Singh, CEO, Quantum Market ResearchDokumen2 halaman"One Day I Want To Own A Football Club in Italy", Rinita Singh, CEO, Quantum Market ResearchSangitaa AdvaniBelum ada peringkat

- Lesson 10 Estimating Population MeansDokumen5 halamanLesson 10 Estimating Population MeansSamleedigiprintsBelum ada peringkat

- Law PHD Thesis ProposalDokumen6 halamanLaw PHD Thesis Proposalangelicaortizpaterson100% (2)

- Hypothesis Testing BasicsDokumen36 halamanHypothesis Testing BasicsRoyal MechanicalBelum ada peringkat

- Readings in Philippines History 1Dokumen24 halamanReadings in Philippines History 1RYAN JEREZBelum ada peringkat

- Objectification of WomenDokumen68 halamanObjectification of WomenShanzay AliBelum ada peringkat

- Adapted StudyDokumen14 halamanAdapted StudySunga ErikaBelum ada peringkat

- Chapt ER8: Strategy Formulation: Functional Strategy and Strategic ChoiceDokumen32 halamanChapt ER8: Strategy Formulation: Functional Strategy and Strategic ChoiceMuhammad Bisma AbdillahBelum ada peringkat

- Assessment CentresDokumen12 halamanAssessment CentresvjvishuBelum ada peringkat