5.IA 64 and Itanium Processors

Diunggah oleh

vignesh_march19940 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

40 tayangan9 halamanIA-64 instructions are encoded in bundles - 128 bits wide: 5-bit template field and three 41-bit instructions. Instructions can be executed in parallel - arbitrarily long, but the compiler explicitly indicates the boundary by placing a stop. Itanium processors are designed to benefit from VLIW approach.

Deskripsi Asli:

Hak Cipta

© © All Rights Reserved

Format Tersedia

PPTX, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniIA-64 instructions are encoded in bundles - 128 bits wide: 5-bit template field and three 41-bit instructions. Instructions can be executed in parallel - arbitrarily long, but the compiler explicitly indicates the boundary by placing a stop. Itanium processors are designed to benefit from VLIW approach.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PPTX, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

40 tayangan9 halaman5.IA 64 and Itanium Processors

Diunggah oleh

vignesh_march1994IA-64 instructions are encoded in bundles - 128 bits wide: 5-bit template field and three 41-bit instructions. Instructions can be executed in parallel - arbitrarily long, but the compiler explicitly indicates the boundary by placing a stop. Itanium processors are designed to benefit from VLIW approach.

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PPTX, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 9

Unit II

Intel IA-64 and Itanium Processor

By

N.R.Rejin Paul

Lecturer/VIT/CSE

CS2354 Advanced Computer Architecture

2

4.7 Intel IA-64 and Itanium Processor

Designed to benefit VLIW approach

IA-64 Register Model

128 64-bit GPR (65 bits actually)

128 82-bit floating-point registers

two extra exponent bits over the standard 80-bit IEEE format

64 1-bit predicate register

8 64-bit branch registers, used for indirect branches

a variety of registers used for system control, etc.

other supports:

register stack frame: like register window in SPARC

current frame pointer (CFM)

register stack engine

3

Five Execution Unit Slots in IA-64

4

Instruction Groups and Bundle

Two concepts to achieve the benefits of implicit parallelism and

ease of instruction decode

instruction group: a sequence of consecutive instructions without

register data dependences

instructions in the group can be executed in parallel

arbitrarily long, but the compiler explicitly indicates the boundary by placing a stop

bundle: fixed formatting of multiple instructions (3)

IA-64 instructions are encoded in bundles

128 bits wide: 5-bit template field and three 41-bit instructions

the template field describes the presence of stops and

specifies types of execution units for each instruction

5

24 Possible Template Values and

Formats

8 possible values are reserved

Stops are indicated by heavy lines

6

Example: Unroll x[i]=x[i]+s Seven Times

9 bundles

21 cycles

85% of slots filled

(23/27)

11 bundles

12 cycles

70% of slots filled

(23/33)

7

Some

Instruction

Formats of IA-

64

See Textbook or

Intels manuals for

more information

8

Predication and Speculation Support

instr 1

instr 2

:

br

ld r1=

use =r1

ld.s r1=

instr 1

instr 2

:

br

chk.s r1

use =r1

ld.s r1=

instr 1

use =r1 instr 2

:

br

chk.s use

Recovery code

ld r1=

use =r1

br

Traditional arch. with

branch barrier

Itanium Support for Explicit Parallelism

LOAD moved

above branch by

compiler

Uses moved

above branch by

compiler

9

Summary

Chapter 4 Exploiting Instruction-Level Parallelism with

Software Approaches

4.1 Basic Compiler Techniques for Exposing ILP

4.2 Static Branch Prediction

4.3 Static Multiple Issue: The VLIW Approach

4.4 Advanced Compiler Support for ILP

4.7 Intel IA-64 Architecture and Itanium Processor

Anda mungkin juga menyukai

- AVRDokumen104 halamanAVRPriya GuptaBelum ada peringkat

- Test Bank and Soluiton 2018-2019Dokumen40 halamanTest Bank and Soluiton 2018-2019A plus Test bank and Solution manualBelum ada peringkat

- MPS Lecture 3 - The Microprocessor and Its ArchitectureDokumen26 halamanMPS Lecture 3 - The Microprocessor and Its ArchitectureShehroze TalatBelum ada peringkat

- Lecture#2 Fut Microprocessor PDFDokumen81 halamanLecture#2 Fut Microprocessor PDFAhmedGamalBelum ada peringkat

- 15 Ia64Dokumen34 halaman15 Ia64Fbi RiyoBelum ada peringkat

- 4 Intel 286 To Pentium ArchitectureDokumen25 halaman4 Intel 286 To Pentium ArchitectureAli AhmadBelum ada peringkat

- Limits of Instruction-Level ParallelismDokumen51 halamanLimits of Instruction-Level ParallelismShanmugapriyaVinodkumarBelum ada peringkat

- AVRDokumen32 halamanAVRSanjeev KamalBelum ada peringkat

- Advanced Processor SuperscalarclassDokumen73 halamanAdvanced Processor SuperscalarclassKanaga Varatharajan50% (2)

- Core8051 DsDokumen41 halamanCore8051 DsMinh Trí KnightBelum ada peringkat

- Intel IA32 (80x86) Microprocessors: Dr. Doug L. Hoffman Computer Science 330 Spring 2002Dokumen28 halamanIntel IA32 (80x86) Microprocessors: Dr. Doug L. Hoffman Computer Science 330 Spring 2002amdevaBelum ada peringkat

- 8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT90S4414 PreliminaryDokumen10 halaman8-Bit Microcontroller With 4K Bytes In-System Programmable Flash AT90S4414 PreliminaryYerson CrespoBelum ada peringkat

- Pentium 4 StructureDokumen38 halamanPentium 4 Structureapi-3801329100% (6)

- Intel Pentium 4 Processor: Presented by Michele CoDokumen60 halamanIntel Pentium 4 Processor: Presented by Michele CoAnonymous jHQWZLaknBelum ada peringkat

- Atmel 2586 AVR 8 Bit Microcontroller ATtiny25 ATtiny45 ATtiny85 DatasheetDokumen234 halamanAtmel 2586 AVR 8 Bit Microcontroller ATtiny25 ATtiny45 ATtiny85 DatasheetcrocomodxBelum ada peringkat

- STM32 Training 12W06 1V0Dokumen73 halamanSTM32 Training 12W06 1V0Oussama Riahi ChBelum ada peringkat

- Microprocessor UpdatedDokumen202 halamanMicroprocessor UpdatedMuhammadShazaibBelum ada peringkat

- EE 346 Microprocessor Principles and Applications An Introduction To Microcontrollers, Assembly Language, and Embedded SystemsDokumen40 halamanEE 346 Microprocessor Principles and Applications An Introduction To Microcontrollers, Assembly Language, and Embedded SystemsAbG Compilation of VideosBelum ada peringkat

- Atmel 2586 AVR 8 Bit Microcontroller ATtiny25 ATtiny45 ATtiny85 DatasheetDokumen234 halamanAtmel 2586 AVR 8 Bit Microcontroller ATtiny25 ATtiny45 ATtiny85 DatasheetTudor ArthurBelum ada peringkat

- A Study On Hyper-Threading: Vimal Reddy Ambarish Sule Aravindh AnantaramanDokumen29 halamanA Study On Hyper-Threading: Vimal Reddy Ambarish Sule Aravindh AnantaramanVetrivel SubramaniBelum ada peringkat

- 8515 CompleteDokumen101 halaman8515 Completefiddu4bvBelum ada peringkat

- Power PC ArchitectureDokumen28 halamanPower PC ArchitecturedesamratBelum ada peringkat

- Pentium ArchitectureDokumen18 halamanPentium ArchitectureMary HarrisonBelum ada peringkat

- Software Pipelining: An Alternative Method of Reorganizing Loops To Increase Instruction Level ParallelismDokumen14 halamanSoftware Pipelining: An Alternative Method of Reorganizing Loops To Increase Instruction Level ParallelismSi Mohamed RahiliBelum ada peringkat

- Chapter 4 Processors and Memory Hierarchy: Module-2Dokumen31 halamanChapter 4 Processors and Memory Hierarchy: Module-2Rahul RajBelum ada peringkat

- Cpe 631 Pentium 4Dokumen111 halamanCpe 631 Pentium 4rohitkotaBelum ada peringkat

- Pentium ArchitectureDokumen3 halamanPentium ArchitectureweblnsBelum ada peringkat

- ATtiny 85Dokumen201 halamanATtiny 85Λιθοξόος Έλλην100% (2)

- VLIW Processors: Spring 2003 CSE P548 1Dokumen17 halamanVLIW Processors: Spring 2003 CSE P548 1Riyuk Diki StayonthelineBelum ada peringkat

- Csa Mod 2Dokumen28 halamanCsa Mod 2anusarat100% (1)

- 80286Dokumen28 halaman80286Kavitha SubramaniamBelum ada peringkat

- CS136, Advanced Architecture: Limits To ILP Simultaneous MultithreadingDokumen49 halamanCS136, Advanced Architecture: Limits To ILP Simultaneous MultithreadingsumikmeaBelum ada peringkat

- MicroprocessorDokumen19 halamanMicroprocessorParasBelum ada peringkat

- Pic16f FeaturesDokumen40 halamanPic16f Featuresveeramaniks408Belum ada peringkat

- ESZG512 ESD Assignment2 WILPDokumen7 halamanESZG512 ESD Assignment2 WILPneelakandan venkatramanBelum ada peringkat

- 2.1: Advanced Processor Technology: Qn:Explain Design Space of Processor?Dokumen29 halaman2.1: Advanced Processor Technology: Qn:Explain Design Space of Processor?ripcord jakeBelum ada peringkat

- AMP Lab ManualDokumen22 halamanAMP Lab ManualSatish PawarBelum ada peringkat

- Chapter Six: The 80x86 Instruction SetDokumen44 halamanChapter Six: The 80x86 Instruction SetAbdifitahBelum ada peringkat

- Module 2 ACA NotesDokumen31 halamanModule 2 ACA NotesShylaja100% (1)

- Chapter 2: The Microprocessor and Its ArchitectureDokumen108 halamanChapter 2: The Microprocessor and Its ArchitectureTaqsim RajonBelum ada peringkat

- Unitv: Embedded System Design-Case Studies Powerpc Processor Architectural IssuesDokumen8 halamanUnitv: Embedded System Design-Case Studies Powerpc Processor Architectural IssuesSoundarya SvsBelum ada peringkat

- Unitv: Embedded System Design-Case Studies Powerpc Processor Architectural IssuesDokumen8 halamanUnitv: Embedded System Design-Case Studies Powerpc Processor Architectural IssuesSoundarya SvsBelum ada peringkat

- CH 2Dokumen24 halamanCH 2sp6445022Belum ada peringkat

- Coa Imp Questions - 32543434 - 2024 - 03 - 19 - 23 - 14Dokumen6 halamanCoa Imp Questions - 32543434 - 2024 - 03 - 19 - 23 - 14cofasi3281Belum ada peringkat

- Module-2 ACADokumen31 halamanModule-2 ACAVivek SinghBelum ada peringkat

- Microprocessor & Its ArchitectureDokumen79 halamanMicroprocessor & Its ArchitectureKen Andrie Dungaran GuariñaBelum ada peringkat

- Lecture 05 ARM ProcessorsDokumen65 halamanLecture 05 ARM ProcessorsNguyễn Tấn ĐịnhBelum ada peringkat

- Lecture 02 - Microcontroller Core Features and ArchitectureDokumen12 halamanLecture 02 - Microcontroller Core Features and ArchitectureAwaisBelum ada peringkat

- General Information: CPU / Microprocessor Intel Pentium 4 631 HH80552PG0802M BX80552631 BX80552631T2Dokumen3 halamanGeneral Information: CPU / Microprocessor Intel Pentium 4 631 HH80552PG0802M BX80552631 BX80552631T2george_rivera_26Belum ada peringkat

- Very Large Scale Instruction WordDokumen22 halamanVery Large Scale Instruction Wordrboy1993Belum ada peringkat

- ProcessorsDokumen44 halamanProcessorsRAHA TUDU100% (4)

- Lecture 1 SarmadDokumen34 halamanLecture 1 SarmadsarmadBelum ada peringkat

- Amp Units 3&4 NotesDokumen18 halamanAmp Units 3&4 NotesSumithBelum ada peringkat

- Distributed and Parallel Computing - Unit2Dokumen92 halamanDistributed and Parallel Computing - Unit2Apoorva RajouraBelum ada peringkat

- 2.1 Advanced Processor TechnologyDokumen40 halaman2.1 Advanced Processor Technologydhivya aBelum ada peringkat

- Advanced Microprocessors: Presented by Ashish Kumar Singh Pranav Gautam Guide Mrs. Nayanica SrivastavaDokumen20 halamanAdvanced Microprocessors: Presented by Ashish Kumar Singh Pranav Gautam Guide Mrs. Nayanica SrivastavaPranav GautamBelum ada peringkat

- Super Scalar ArchitecturesDokumen36 halamanSuper Scalar Architectureskhuram4uBelum ada peringkat

- Week 02Dokumen55 halamanWeek 02aroosa naheedBelum ada peringkat

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDari EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationBelum ada peringkat

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Dari EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Belum ada peringkat

- How The JVM Locates, Loads, and Runs Libraries: Class Loaders Are The Key To Understanding How The JVM Executes ProgramsDokumen4 halamanHow The JVM Locates, Loads, and Runs Libraries: Class Loaders Are The Key To Understanding How The JVM Executes Programsvignesh_march1994Belum ada peringkat

- Alipay Payment Method Guide 2Dokumen8 halamanAlipay Payment Method Guide 2vignesh_march1994100% (1)

- Api ReferenceDokumen14 halamanApi Referencevignesh_march1994Belum ada peringkat

- Integrating Queueing Theory and Scheduling For Dynamic Scheduling ProblemsDokumen38 halamanIntegrating Queueing Theory and Scheduling For Dynamic Scheduling Problemsvignesh_march1994Belum ada peringkat

- Source Anonymitybased Enhanced Framework in Disruption Tolerant Military NetworksDokumen7 halamanSource Anonymitybased Enhanced Framework in Disruption Tolerant Military Networksvignesh_march1994Belum ada peringkat

- Program ListDokumen5 halamanProgram Listvignesh_march1994Belum ada peringkat

- Athena Health Sample Interview QuestionsDokumen4 halamanAthena Health Sample Interview Questionsvignesh_march1994Belum ada peringkat

- UltrasoundDokumen26 halamanUltrasoundvignesh_march19940% (1)

- AndroidDokumen1 halamanAndroidvignesh_march1994Belum ada peringkat

- QuizDokumen3 halamanQuizvignesh_march1994Belum ada peringkat

- Cinimamachine TuteDokumen7 halamanCinimamachine TutegregoryBelum ada peringkat

- Community Detection in Social Networks An OverviewDokumen6 halamanCommunity Detection in Social Networks An OverviewInternational Journal of Research in Engineering and TechnologyBelum ada peringkat

- Iso 8402-1994Dokumen23 halamanIso 8402-1994Davood OkhovatBelum ada peringkat

- Information Theory - SAMPLE EXAM ONLY: MATH3010Dokumen5 halamanInformation Theory - SAMPLE EXAM ONLY: MATH3010Pradeep RajaBelum ada peringkat

- Graylog Extractors RsyslogDokumen3 halamanGraylog Extractors RsyslogAndrey TBelum ada peringkat

- Upload - NMBDokumen15 halamanUpload - NMBTHANIGAINATHAN.G.D 10A3Belum ada peringkat

- Internship JD MaproDokumen2 halamanInternship JD MaproJimmy JonesBelum ada peringkat

- Va - Zvuk Osamdesetih - 1997 - Zabavna I Pop - 1982 - 1983Dokumen6 halamanVa - Zvuk Osamdesetih - 1997 - Zabavna I Pop - 1982 - 1983bozicna_jelkaBelum ada peringkat

- Auto Hematology AnalyzerDokumen1 halamanAuto Hematology AnalyzerKhashayar ModaberiBelum ada peringkat

- WebQual An Exploration of Website QualityDokumen9 halamanWebQual An Exploration of Website QualityArmiasthoMiazBelum ada peringkat

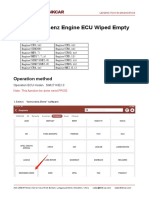

- Mercedes Benz Engine ECU Wiped EmptyDokumen9 halamanMercedes Benz Engine ECU Wiped EmptyP BBelum ada peringkat

- S1200CPU LAxesGrpCtrl DOC v11 enDokumen62 halamanS1200CPU LAxesGrpCtrl DOC v11 enDavid JimenezBelum ada peringkat

- Test Point Insertion For Test Coverage Improvement in DFT - Design For Testability (DFT) .HTMLDokumen75 halamanTest Point Insertion For Test Coverage Improvement in DFT - Design For Testability (DFT) .HTMLIlaiyaveni IyanduraiBelum ada peringkat

- Modicon M258 - XBTZ9008Dokumen2 halamanModicon M258 - XBTZ9008Andrian Fathurohman PermanaBelum ada peringkat

- Enterprise Account Sales Manager in San Diego CA Resume Thomas WoodDokumen3 halamanEnterprise Account Sales Manager in San Diego CA Resume Thomas WoodThomasWoodBelum ada peringkat

- Chief Patrons: in Association With Global Research Conference Forum Organizes Virtual International Conference OnDokumen2 halamanChief Patrons: in Association With Global Research Conference Forum Organizes Virtual International Conference OnRavishankar BhaganagareBelum ada peringkat

- CSS Institutional Asessment PackageDokumen2 halamanCSS Institutional Asessment PackageJohnny Pancito RodriguezBelum ada peringkat

- Comm 12ND QuaterDokumen5 halamanComm 12ND QuaterApril BuenoBelum ada peringkat

- ELL782: Computer ArchitectureDokumen2 halamanELL782: Computer ArchitectureSIYAB KhanBelum ada peringkat

- 4hana 1909Dokumen60 halaman4hana 1909ddharBelum ada peringkat

- Concepts of Multimedia Processing and TransmissionDokumen63 halamanConcepts of Multimedia Processing and TransmissionvelmanirBelum ada peringkat

- Combined Calendar Application and Scientific CalculatorDokumen36 halamanCombined Calendar Application and Scientific CalculatorPulak Kumar MandalBelum ada peringkat

- Form 2 March 2020 Break Computer Studies AssignmentDokumen16 halamanForm 2 March 2020 Break Computer Studies AssignmentKarari WahogoBelum ada peringkat

- B452 Service Manual 04 - B450 - MMDokumen124 halamanB452 Service Manual 04 - B450 - MMgenmassaBelum ada peringkat

- Net-Net 4000 S-CX6.4.0 MIB Reference GuideDokumen126 halamanNet-Net 4000 S-CX6.4.0 MIB Reference GuideFrancoj DABelum ada peringkat

- Surat Pernyataan Calon Mahasiswa BaruDokumen3 halamanSurat Pernyataan Calon Mahasiswa Barua2020-11469 Ian Hadisurya BudimanBelum ada peringkat

- It - Mega - Courses 1Dokumen13 halamanIt - Mega - Courses 1Telt100% (4)

- UGDokumen23 halamanUGram101987Belum ada peringkat

- cs2201 Unit1 Notes PDFDokumen16 halamancs2201 Unit1 Notes PDFBal BolakaBelum ada peringkat