Contadores Asincrono-Sincrono

Diunggah oleh

Angel Ortiz0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

658 tayangan20 halamanJudul Asli

10. CONTADORES ASINCRONO-SINCRONO.ppt

Hak Cipta

© © All Rights Reserved

Format Tersedia

PPT, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PPT, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

658 tayangan20 halamanContadores Asincrono-Sincrono

Diunggah oleh

Angel OrtizHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PPT, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 20

CONTADORES ASINCRONOS.

Tipo de contador en el que la salida de cada flip - flops

sirve como la entrada de reloj del siguiente que se

encuentra en la cadena.

EJEMPLOS:

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

Este contador es asncrono debido a que los FF

no cambian en sincrona exacta con los pulsos de

reloj; solo el flip flop A responde a stos. El flip - flop B

tiene que esperar a que el flip - flop A cambie estados

antes de que se complemente, el flip - flop C tiene que

esperar al flip - flop B; y as sucesivamente.

El contador anterior tiene 16 estados diferentes (del

0000 al 1111). Por tanto, se conoce como contador de

rizo MOD-16 (donde MOD se refiere al nmero de

estados por los cuales pasa el contador en cada ciclo

completo antes de que se recicle hacia su estado

inicial). El nmero MOD = 2

N

, donde N es el nmero de

flip flops conectados en la configuracin anterior.

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

CONTADORES CON NMEROS

MOD < 2

N

El contador bsico puede ser modificado

para producir nmeros MOD menores que

2

N

, permitiendo que el contador omita

estados que normalmente son parte de la

secuencia de conteo.

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

EJEMPLO: Contador MOD-6 producido por el borrado de

un contador MOD-8 cuando ocurre el conteo de seis (110).

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

Diagrama de Transicin de estados para el contador

MOD-6 de la figura anterior

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

EJERCICIOS

Determinar el nmero MOD del

contador de las siguientes

figuras, as como la frecuencia

en la salida D.

SISTEMAS DIGITALES I ING. ELECTRNICA

SCdeE.- 2009

Circuitos Secuenciales

FIGURA 1:

SISTEMAS DIGITALES I ING. ELECTRNICA

SCdeE.- 2009

Circuitos Secuenciales

FIGURA 2:

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

PROCEDIMIENTO GENERAL PARA CONSTRUIR UN

CONTADOR QUE EMPIECE A CONTAR DESDE TODOS

LOS CEROS Y TENGA UN NMERO MOD DE X:

Determinar el menor nmero de FF tales como 2

N

X y

conectarlo como un contador. Si 2

N

= X, no realice los

pasos 2 y 3.

Conecte una compuerta NAND a las entradas

asncronas RESTABLECER (Clear) de todos los FF.

Determine cules FF estn en el estado ALTO (H) en un

conteo = X; luego conecte las salidas normales de estos

FF a las entradas de la compuerta NAND.

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

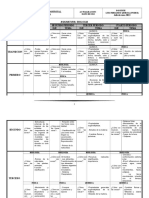

CONTADOR ASNCRONO 74293

MR1 MR2 Q3 Q2 Q1 Q0

H H L L L L

L H

H L

L L

Q3 Q2 Q1 Q0

0 L L L L

1 L L L H

2 L L H L

3 L L H H

4 L H L L

5 L H L H

6 L H H L

7 L H H H

8 H L L L

9 H L L H

10 H L H L

11 H L H H

12 H H L L

13 H H L H

14 H H H L

15 H H H H

ENTRADAS

DE RESET

SALIDAS

SALIDAS CUEN

TA

CUENTA

CUENTA

CUENTA

SISTEMAS DIGITALES I ING. ELECTRNICA

SCdeE.- 2009

DIAGRAMA LGICO

Todas las entradas J, K se encuentran internamente conectadas a ALTO.

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

Conexiones del Contador 74293

Contador MOD-16.

Contador MOD-10.

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

Contador MOD-60.

El problema que presentan los contadores asncronos es el que se

refiere a los retardos de propagacin, debido a que no todos los FF

cambian de estado en sincrona con los pulsos de entrada. A

consecuencia del problema anterior, estos contadores no son tiles en

frecuencias muy altas, sobre todo para nmeros grandes de bits.

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

Retardos de propagacin en un contador binario

asncrono de tres bits.

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

TAREA:

Determine a travs de diagramas de tiempo la secuencia de conteo

del siguiente contador. Grafique las seales en el siguiente orden:

CLK, A, A, B, B, C y X. Todas las entradas J, K son altas.

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

CONTADORES SINCRNOS

Contador en el que todos los flip flops estn

sincronizados simultneamente por un reloj.

Q

1

Q

1

J

1

K

1

Q

0

J

0

Q

0

K

0

CLOCK

J

0

= K

0

= 1

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

1

0

1

0 0

1

Q

J K

J K

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

Estado

Presente

/q

0

/q0 1 1

Estado

siguiente

q

1

q

0

J

1

K

1

J

o

K

o

Q

1

Q

0

CONTADORES SINCRNOS

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

CONTADORES SINCRNOS

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

Diagramas de tiempos para un contador sncrono de 2 bits

(los retardos de ambos FF se consideran iguales)

COMPARACIN ENTRE CONTADORES

SNCRONOS CON LOS ASNCRONOS.

Las entradas CLK de todos los FF estn conectados

entre s de modo que la seal entrada de reloj se

aplica simultneamente a todos los FF.

Slo el FF A, que es el LSB, tiene entradas J y K que

estn permanentemente en el nivel ALTO (H). Las

entradas de los dems FF son excitadas por alguna

combinacin en las salidas de los propios FF.

El contador sncrono requiere de ms circuitera que

un contador asncrono

SISTEMAS DIGITALES I ING. ELECTRNICA

Circuitos Secuenciales

SCdeE.- 2009

Anda mungkin juga menyukai

- Ejercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiDari EverandEjercicios prácticos con Electrónica: Proyectos de electrónica con Arduino y Raspberry PiPenilaian: 5 dari 5 bintang5/5 (1)

- Costos de MantenimientoDokumen9 halamanCostos de Mantenimientorjesusr50% (2)

- Circuitos SecuencialesDokumen19 halamanCircuitos SecuencialesIrma Bravo BorjasBelum ada peringkat

- Practica 1 Latch SRDokumen10 halamanPractica 1 Latch SRBrandon Vargas ChicoBelum ada peringkat

- Informe Majes Sihuas Ultimo Mayo Del 2019Dokumen18 halamanInforme Majes Sihuas Ultimo Mayo Del 2019Carlos VegaBelum ada peringkat

- Contador Descendente Mod 10 130Dokumen2 halamanContador Descendente Mod 10 130cuzcuz2050% (2)

- Ensayo Contador Sincrono y AsincronoDokumen2 halamanEnsayo Contador Sincrono y Asincronomatias29Belum ada peringkat

- Instrumentación Industrial Tema 3Dokumen34 halamanInstrumentación Industrial Tema 3Angel OrtizBelum ada peringkat

- Contadores y registros digitalesDokumen18 halamanContadores y registros digitalesLucia Barrera GastañaduiBelum ada peringkat

- Contadores Asincronos y SincronosDokumen30 halamanContadores Asincronos y SincronosYamil Solis Diaz100% (3)

- Informe Reloj DigitalDokumen9 halamanInforme Reloj DigitalJavier CarvajalBelum ada peringkat

- Contador Con Flip-FlopDokumen2 halamanContador Con Flip-Floptubi vok3100% (3)

- 08 ContadoresDokumen60 halaman08 ContadoresViviana Elizabeth VeraBelum ada peringkat

- Cables AwgDokumen2 halamanCables AwgAngel OrtizBelum ada peringkat

- 4a - Clases Sistemas DigitalesDokumen31 halaman4a - Clases Sistemas DigitalesMauricioGuanoluisaBelum ada peringkat

- Sumadores, comparadores y decodificadores digitalesDokumen4 halamanSumadores, comparadores y decodificadores digitalesVictor Castrejon100% (3)

- Introducción Al Psoc5Lp: Teoría y aplicaciones prácticaDari EverandIntroducción Al Psoc5Lp: Teoría y aplicaciones prácticaBelum ada peringkat

- Circuitos Secuenciales Usando FPGADokumen60 halamanCircuitos Secuenciales Usando FPGAPedro Landaeta100% (2)

- Contador Asincrónico Descendente Módulo 32Dokumen3 halamanContador Asincrónico Descendente Módulo 32Cristian AguilarBelum ada peringkat

- Circuito Integrado 74LS181 (ALU)Dokumen3 halamanCircuito Integrado 74LS181 (ALU)Luis B HernandezBelum ada peringkat

- Manual para El Manejo Del Software EmpowerDokumen24 halamanManual para El Manejo Del Software EmpowerAndrea Stephanie Bello Diaz80% (5)

- SolucionarioDokumen5 halamanSolucionariojuanBelum ada peringkat

- Preguntas Equipo 2 Amplificador OperacionalDokumen3 halamanPreguntas Equipo 2 Amplificador OperacionalEdgar BC0% (2)

- Logica Digital Proyecto 1 PDFDokumen12 halamanLogica Digital Proyecto 1 PDFelenaBelum ada peringkat

- Informe de Circuitos Logicos (Contadores) 4Dokumen18 halamanInforme de Circuitos Logicos (Contadores) 4Louis Charles86% (7)

- Sumador de 4 BitsDokumen11 halamanSumador de 4 Bitsbaad13Belum ada peringkat

- Creación de Un Reloj Digital Usando Circuitos Integrados TTL en Proteus.Dokumen17 halamanCreación de Un Reloj Digital Usando Circuitos Integrados TTL en Proteus.Karlos EstangaBelum ada peringkat

- Celda BásicaDokumen2 halamanCelda BásicaWendyBelum ada peringkat

- Registro de DesplazamientoDokumen42 halamanRegistro de Desplazamientodante azaña vega100% (1)

- Sistemas de numeración en electrónica digitalDokumen12 halamanSistemas de numeración en electrónica digitalCarlos Enrique Infantes PeraltaBelum ada peringkat

- Registros desplazamientoDokumen4 halamanRegistros desplazamientoDennis Montero JimenezBelum ada peringkat

- Flip flops y ejerciciosDokumen47 halamanFlip flops y ejerciciossbuesoBelum ada peringkat

- Contador Binario de 4 y 8 BitsDokumen7 halamanContador Binario de 4 y 8 BitsAlan VazquezBelum ada peringkat

- Como Hacer Reloj DigitalDokumen9 halamanComo Hacer Reloj DigitalSusy VillafanBelum ada peringkat

- Practica 5 Aplificador de Audio en ProteusDokumen7 halamanPractica 5 Aplificador de Audio en ProteusGiovas CamachoBelum ada peringkat

- Practica 3 (Semisumador)Dokumen6 halamanPractica 3 (Semisumador)pedroanayaBelum ada peringkat

- Guia Instalacion Quartus IIDokumen19 halamanGuia Instalacion Quartus IIJesus ManuelBelum ada peringkat

- Contador Del 0 Al 9 en PIC 16F877ADokumen2 halamanContador Del 0 Al 9 en PIC 16F877AKarinna VillarreealBelum ada peringkat

- Señal Reloj Flanco y Nivel Grupo 4.pooDokumen10 halamanSeñal Reloj Flanco y Nivel Grupo 4.pooALANYS DAYANA GUERRERO PERRAZOBelum ada peringkat

- Trabajo Encargado de Elect IV 2018 IIDokumen8 halamanTrabajo Encargado de Elect IV 2018 IIZexars -Belum ada peringkat

- Informe Modulación Delta - AdaptativaDokumen4 halamanInforme Modulación Delta - AdaptativaCristian1032Belum ada peringkat

- Contadores y Registro de DesplazamientoDokumen22 halamanContadores y Registro de DesplazamientoCristhian AndresBelum ada peringkat

- Codificación UnipolarDokumen6 halamanCodificación UnipolarErick Joel ClaudioBelum ada peringkat

- Tabacos Chasi JonathanDokumen9 halamanTabacos Chasi JonathanJonathan ChasiBelum ada peringkat

- Sistemas Digitales Tarea 1 Flip Flops y OsciladoresDokumen39 halamanSistemas Digitales Tarea 1 Flip Flops y OsciladoresC Geramias MoralesBelum ada peringkat

- Preguntas Amplificador OperacionalDokumen7 halamanPreguntas Amplificador OperacionalWalter Acosta100% (1)

- Circuitos combinacionales MSI para sumar y restarDokumen4 halamanCircuitos combinacionales MSI para sumar y restarFabianBañoBelum ada peringkat

- Contador de DecadasDokumen12 halamanContador de Decadasjose manuel sotoBelum ada peringkat

- Proyecto Reloj DigitalDokumen6 halamanProyecto Reloj DigitalChekson AzamareBelum ada peringkat

- Analógicas vs digitales, conversiones binarias, circuitos lógicosDokumen16 halamanAnalógicas vs digitales, conversiones binarias, circuitos lógicosluisBelum ada peringkat

- ContadoresDokumen126 halamanContadoresPatrick Fs DeadLove92% (13)

- Informe Flip/Flop 7473Dokumen13 halamanInforme Flip/Flop 7473Ignacio Vera75% (4)

- Reloj digital formato 24 horasDokumen1 halamanReloj digital formato 24 horasSebaz LuisBelum ada peringkat

- Lab 3 N2 Sistemas DigitalesDokumen18 halamanLab 3 N2 Sistemas DigitalesChristian Huapaya ContrerasBelum ada peringkat

- Informe de Proyecto Sistemas DigitalesDokumen20 halamanInforme de Proyecto Sistemas DigitalesHans Cubeños MontoyaBelum ada peringkat

- Modelo MotorDokumen13 halamanModelo MotorVivivianaBelum ada peringkat

- Conversores ADDokumen7 halamanConversores ADPablo RafaelBelum ada peringkat

- Registros de DesplazamientoDokumen30 halamanRegistros de Desplazamientoabeat_1100% (2)

- Reporte Sumador Binario 4 BitsDokumen7 halamanReporte Sumador Binario 4 BitsWILDFHER100% (1)

- Sistemas ProgramablesDokumen4 halamanSistemas ProgramablesivantwrsBelum ada peringkat

- Contador binario de 4 y 8 bits y diseño de contador de 10 décadasDokumen7 halamanContador binario de 4 y 8 bits y diseño de contador de 10 décadasJoel Cad PadBelum ada peringkat

- Cad Apartir CdaDokumen7 halamanCad Apartir CdaJoz SanBallBelum ada peringkat

- Contador binario de 0 a 255 con dos 74LS193Dokumen9 halamanContador binario de 0 a 255 con dos 74LS193Ricardo salasBelum ada peringkat

- ElectronicaDokumen9 halamanElectronicameteo21Belum ada peringkat

- Contadores ElectrónicosDokumen4 halamanContadores ElectrónicosJavi ArévaloBelum ada peringkat

- Lo prometido es deudaDokumen2 halamanLo prometido es deudaAngel OrtizBelum ada peringkat

- Empalmes ElectricosDokumen5 halamanEmpalmes ElectricosAngel OrtizBelum ada peringkat

- Lo prometido es deudaDokumen2 halamanLo prometido es deudaAngel OrtizBelum ada peringkat

- Capitulo I (Reseña Historica)Dokumen7 halamanCapitulo I (Reseña Historica)Angel OrtizBelum ada peringkat

- Etapa 1 Lavado, Sistemas y AutomatismosDokumen7 halamanEtapa 1 Lavado, Sistemas y AutomatismosAngel OrtizBelum ada peringkat

- Linux Paso A PasoDokumen6 halamanLinux Paso A PasoAngel OrtizBelum ada peringkat

- Presentacion AlgoritmosDokumen28 halamanPresentacion AlgoritmosAngel OrtizBelum ada peringkat

- AnálisisDokumen9 halamanAnálisisAngel OrtizBelum ada peringkat

- Biodiversidad: Los 5 ReinosDokumen20 halamanBiodiversidad: Los 5 ReinosAngel OrtizBelum ada peringkat

- AlgoritmosDokumen28 halamanAlgoritmosAngel OrtizBelum ada peringkat

- Control de CostosDokumen1 halamanControl de CostosAngel OrtizBelum ada peringkat

- Hola Tu DEVCDokumen1 halamanHola Tu DEVCAngel OrtizBelum ada peringkat

- Parámetros Estadísticos de MantenimientoDokumen7 halamanParámetros Estadísticos de MantenimientoAngel OrtizBelum ada peringkat

- Laboratorio UPTA: control e instrumentaciónDokumen10 halamanLaboratorio UPTA: control e instrumentaciónAngel OrtizBelum ada peringkat

- Control de costos principios claveDokumen3 halamanControl de costos principios claveAngel Ortiz0% (1)

- Punta Logica de Prueba InformeDokumen17 halamanPunta Logica de Prueba InformeAngel OrtizBelum ada peringkat

- Educ FisicaDokumen16 halamanEduc FisicaAngel OrtizBelum ada peringkat

- Sistemas de Control (Introduccion)Dokumen12 halamanSistemas de Control (Introduccion)Angel OrtizBelum ada peringkat

- TemperaturaDokumen87 halamanTemperaturaAngel OrtizBelum ada peringkat

- NM3 Trigonometria FormularioDokumen2 halamanNM3 Trigonometria FormularioAngel OrtizBelum ada peringkat

- NormasISAproyectosInstrumentaciónDokumen34 halamanNormasISAproyectosInstrumentaciónAngel OrtizBelum ada peringkat

- TemperaturaDokumen87 halamanTemperaturaAngel OrtizBelum ada peringkat

- Laboratorio UPTA: control e instrumentaciónDokumen10 halamanLaboratorio UPTA: control e instrumentaciónAngel OrtizBelum ada peringkat

- Algoritmos NarrativosDokumen12 halamanAlgoritmos NarrativosdanyrojodecorazonBelum ada peringkat

- Trabajo Sobre La Contaminación SónicaDokumen5 halamanTrabajo Sobre La Contaminación SónicaAngel OrtizBelum ada peringkat

- Relatoria para RevisarDokumen5 halamanRelatoria para RevisarAngel OrtizBelum ada peringkat

- Signos Vitales - Wikipedia, La Enciclopedia LibreDokumen5 halamanSignos Vitales - Wikipedia, La Enciclopedia LibreJ ArmorBelum ada peringkat

- Fundicion Ejercicio RespuestaDokumen2 halamanFundicion Ejercicio RespuestaEmanuel Medina100% (1)

- AUTISMO - A Propósito Del AutismoDokumen44 halamanAUTISMO - A Propósito Del AutismoJuan Larbán VeraBelum ada peringkat

- Técnicas de Coordinación MotrizDokumen7 halamanTécnicas de Coordinación MotrizJULIETH CAROLINA LUNA TIMANABelum ada peringkat

- Técnicas de Inmunodiagnóstico - A1Dokumen30 halamanTécnicas de Inmunodiagnóstico - A1José MendesBelum ada peringkat

- Química Clase 4Dokumen5 halamanQuímica Clase 4jose bBelum ada peringkat

- Portfolio Gisela C Alestra Web PDFDokumen36 halamanPortfolio Gisela C Alestra Web PDFArhian NatariBelum ada peringkat

- La Voz De La Sangre Vampiros 01 - Jemiah JeffersonDokumen190 halamanLa Voz De La Sangre Vampiros 01 - Jemiah Jeffersonvarias tareasBelum ada peringkat

- Sindromes ColicosDokumen12 halamanSindromes ColicosKarly GarciaBelum ada peringkat

- Teorías y Modelos1Dokumen49 halamanTeorías y Modelos1Victor Daniel Pelagio QuintanaBelum ada peringkat

- Template Practica FundamentosDokumen5 halamanTemplate Practica Fundamentosmatematica fisica quimica boliviaBelum ada peringkat

- Las FuerzasDokumen5 halamanLas FuerzasmacacoBelum ada peringkat

- Matriz IAAS Por ÁreasDokumen156 halamanMatriz IAAS Por ÁreasMartha LaimeBelum ada peringkat

- Planificacion - Practica II - RevisadaDokumen6 halamanPlanificacion - Practica II - Revisadaprensa latamBelum ada peringkat

- Lengua Castellana - Tipos de TextosDokumen15 halamanLengua Castellana - Tipos de TextosYovanna MejiasBelum ada peringkat

- Taller 4Dokumen30 halamanTaller 4John CoronadoBelum ada peringkat

- Gremios tróficos de insectos acuáticos en el río El MolinoDokumen4 halamanGremios tróficos de insectos acuáticos en el río El MolinoJonathanPerezBritoBelum ada peringkat

- Técnicas de Estudio para Mejorar El AprendizajeDokumen7 halamanTécnicas de Estudio para Mejorar El AprendizajeLuis Enrique Contreras GuerreroBelum ada peringkat

- Riesgos y medidas de seguridad en maquinaria de construcciónDokumen4 halamanRiesgos y medidas de seguridad en maquinaria de construcciónJose Randolph Rodriguez HuamaniBelum ada peringkat

- Anexo N°01Dokumen9 halamanAnexo N°01Crst Keyshy Yura QBelum ada peringkat

- Malla Curricular Ciencias 2013 Biologia Quimica y FisicaDokumen13 halamanMalla Curricular Ciencias 2013 Biologia Quimica y Fisicadarkan22Belum ada peringkat

- Aforo Del Caudal de Mi CasaDokumen6 halamanAforo Del Caudal de Mi CasaFlorisel GomezBelum ada peringkat

- Práctica 5.equivalente Electrico de CalorDokumen5 halamanPráctica 5.equivalente Electrico de CalorDaniel Toledo71% (7)

- CALIBRACIONESDokumen24 halamanCALIBRACIONESKene Aguilar ZanabriaBelum ada peringkat

- Maual Asp NeoDokumen4 halamanMaual Asp NeoCenema CenemaBelum ada peringkat

- SERIAMOS OBJETOSDokumen16 halamanSERIAMOS OBJETOSSueña Desea ObtendrásBelum ada peringkat

- 35 EstadísticasDokumen6 halaman35 EstadísticasCarlos Ernesto Calderon RamirezBelum ada peringkat

- Informe de Experimentación de Física-Carril de AireDokumen3 halamanInforme de Experimentación de Física-Carril de AireCarlos Andres PeñaBelum ada peringkat