ECE448 Lecture15 ASIC Design

Diunggah oleh

Sunil PandeyHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

ECE448 Lecture15 ASIC Design

Diunggah oleh

Sunil PandeyHak Cipta:

Format Tersedia

ECE 448

Lecture 15

ASICs vs. FPGAs

ECE 448 FPGA and ASIC Design with VHDL

George Mason University

FPGAs vs. ASICs

ASICs

High performance

FPGAs

Off-the-shelf

Low development costs

Low power

Short time to the market

Low cost (but only

in high volumes)

ECE 448 FPGA and ASIC Design with VHDL

Reconfigurability

ASIC Design Example Factoring circuit/GMU

Global Memory

Local

Memory

ECE 448 FPGA and ASIC Design with VHDL

ASIC 130 nm vs. Virtex II 6000

Factoring/GMU

19.68 mm

19.80 mm

51x

Area of Xilinx Virtex II 6000

FPGA

(estimation by R.J. Lim Fong,

MS Thesis, VPI, 2004)

2.7 mm

2.82 mm

Area of an ASIC with equivalent functionality

ECE 448 FPGA and ASIC Design with VHDL

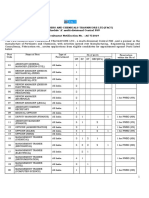

ASICs vs. FPGAs

Source:

I. Kuon, J. Rose,

University of Toronto

Measuring the Gap Between

FPGAs and ASICs

IEEE Transactions on Computer-Aided

Design of Integrated Circuits and Systems,

vol. 62, no. 2, Feb 2007.

ECE 448 FPGA and ASIC Design with VHDL

ASICs vs. FPGAs

23 representative circuits implemented using

FPGAs and ASICs

- computer arithmetic (booth, cordic18, cordic8, etc.)

- digital signal processing (rs_encoder, fir3, fir24,

etc.)

- communications (ethernet, mac1, atm, etc.)

- cryptography (des_area, des_perf, aes, aes192,

etc.)

- scientific computations (molecular, raytracer, etc.)

ECE 448 FPGA and ASIC Design with VHDL

ECE 448 FPGA and ASIC Design with VHDL

ECE 448 FPGA and ASIC Design with VHDL

ECE 448 FPGA and ASIC Design with VHDL

ECE 448 FPGA and ASIC Design with VHDL

10

ASIC Design Flow

Algorithm

Specification

RTL Design

Verilog, VHDL

Reference

Implementation

C, C++

Synopsys Design Compiler

stdcell lib

Logic Synthesis

Layout

VCS

Hercules

Calibre

die area

pin count

LVS

Mentor Calibre

Synopsys StarRCXT

Parasitic Extraction

latency

throughput

(post-synthesis)

Simulation

Synopsys IC Compiler

Cadence Encounter

process lib

Design

Quality

test vectors

VCD

Simulation

PrimeTime

latency

throughp

ut

(post

P&R)

power diss

11

Simplified ASIC Design Flow

Front-End

Design

Back-End

Design

Synthesis

Timing Analysis

Floorplanning

Placement

Clock Tree Synthesis

Routing

Design for Manufacturing

ECE 448 FPGA and ASIC Design with VHDL

12

31

Major ASIC Toolsets

Cadence

Magma

ECE 448 FPGA and ASIC Design with VHDL

13

Simplified ASIC Design Flow

Front-End

Design

Back-End

Design

Synthesis

Timing Analysis

Synopsys

Tools

Design Compiler

Primetime

Floorplanning

Placement

Clock Tree Synthesis

Astro

Routing

Design for Manufacturing

ECE 448 FPGA and ASIC Design with VHDL

14

31

A Complete Placed and Routed Chip

IP

ECE 448 FPGA and ASIC Design with VHDL

15

28

Digital system design technologies

coverage in the CpE & EE programs at GMU

Microprocessors

ECE 445

ASICs

FPGAs

Computer

Organization

ECE 431

Digital Circuit Design

ECE 447

Single Chip

Microcomputers

ECE 448

FPGA and ASIC Design with VHDL

ECE 511

ECE 611

Microprocessors

Advanced

Microprocessors

ECE 545

ECE 645

Digital System Design with VHDL

Computer Arithmetic

ECE 586

Digital

Integrated

Circuits

ECE 681

VLSI Design

for ASICs

DIGITAL SYSTEMS DESIGN

1. ECE 545 Digital System Design with VHDL

K. Gaj, project, FPGA design with VHDL, Aldec/Xilinx/Altera

2. ECE 645 Computer Arithmetic

K. Gaj, project, FPGA design with VHDL or Verilog,

Aldec/Xilinx/Altera/Synopsys

3. ECE 586 Digital Integrated Circuits

D. Ioannou

4. ECE 681 VLSI Design for ASICs

N. Klimavicz, project/lab, front-end and back-end ASIC design with

Synopsys tools

5. ECE 682 VLSI Test Concepts

T. Storey, homework

Anda mungkin juga menyukai

- Digital Design Interview QuestionsDokumen47 halamanDigital Design Interview QuestionsSangameshwer Enterprises100% (1)

- PID Based Temperature Controller Implementation On FPGADokumen11 halamanPID Based Temperature Controller Implementation On FPGAamitkumar_87Belum ada peringkat

- Schematic Diagram of Ip Camera With EthernetDokumen18 halamanSchematic Diagram of Ip Camera With EthernetnguyenminhtuanengineBelum ada peringkat

- Fuzzy Logic Design Using VHDL On FPGADokumen69 halamanFuzzy Logic Design Using VHDL On FPGAadaikammeik100% (1)

- g4 Project ReportDokumen60 halamang4 Project ReportDrake Moses KabbsBelum ada peringkat

- A Multi-Granularity FPGA With Hierarchical Interconnects For Efficient and Flexible Mobile Computing PDFDokumen13 halamanA Multi-Granularity FPGA With Hierarchical Interconnects For Efficient and Flexible Mobile Computing PDFBoppidiSrikanthBelum ada peringkat

- ECE448 Lecture2 VHDL RefresherDokumen73 halamanECE448 Lecture2 VHDL RefresherashishshuklabsBelum ada peringkat

- VLSI Design Flow: From Digital Design to IC ProductsDokumen33 halamanVLSI Design Flow: From Digital Design to IC ProductsUtsav ParasharBelum ada peringkat

- SOC - System On Chip SeminarDokumen8 halamanSOC - System On Chip SeminarUlhas N. GangjiBelum ada peringkat

- Comparison of ASIC TechnologyDokumen16 halamanComparison of ASIC Technologyasifpatel1234100% (1)

- Analog and Digital MEMS Microphone Design Considerations6Dokumen7 halamanAnalog and Digital MEMS Microphone Design Considerations6aragon1974Belum ada peringkat

- (Kota) Oled DocumentationDokumen37 halaman(Kota) Oled Documentationvenkykota33% (3)

- Nios 2Dokumen57 halamanNios 2Rohit PradhanBelum ada peringkat

- Implementation of A Streaming Camera Using An FPGA and CMOS Image SensorDokumen8 halamanImplementation of A Streaming Camera Using An FPGA and CMOS Image SensorPravin WilfredBelum ada peringkat

- Semiconductor RoadmapDokumen34 halamanSemiconductor RoadmapGary Ryan DonovanBelum ada peringkat

- Homulle-Zimmerling Thesis UAV Camera System PDFDokumen82 halamanHomulle-Zimmerling Thesis UAV Camera System PDFAlexandru CozmaBelum ada peringkat

- Power ElectronicsDokumen37 halamanPower ElectronicsMohammad Tabrez AlamBelum ada peringkat

- Alkaline HydrolysisDokumen28 halamanAlkaline Hydrolysissiamak77Belum ada peringkat

- Semiconductors Next WaveDokumen59 halamanSemiconductors Next WaveGary Ryan DonovanBelum ada peringkat

- Implementation of RISC-V SoC From RTL To GDS Flow Using Open-Source ToolsDokumen8 halamanImplementation of RISC-V SoC From RTL To GDS Flow Using Open-Source ToolsIJRASETPublicationsBelum ada peringkat

- VGA Video Signal GenerationDokumen34 halamanVGA Video Signal Generationgongster100% (14)

- Video Graphics Array (VGA) With FpgaDokumen22 halamanVideo Graphics Array (VGA) With FpgadsdsBelum ada peringkat

- MOSFET Scaling: Dr. Rajan Pandey Associate Professor, SENSEDokumen6 halamanMOSFET Scaling: Dr. Rajan Pandey Associate Professor, SENSEVibha M VBelum ada peringkat

- WP 01133 Ip CameraDokumen10 halamanWP 01133 Ip CameraBob HwknsBelum ada peringkat

- VGA Design On VHDL: Submitted By: Pranav Jain (UM 10504) Varun Yadav (UE 105106) Rachit Duggal (UM 10505)Dokumen15 halamanVGA Design On VHDL: Submitted By: Pranav Jain (UM 10504) Varun Yadav (UE 105106) Rachit Duggal (UM 10505)Pranav JainBelum ada peringkat

- Messenger Development Without Internet Using Zigbee TechnologyDokumen89 halamanMessenger Development Without Internet Using Zigbee TechnologyRaghu ReddyBelum ada peringkat

- Performance Comparison of 2D and 3D Torus Network-on-Chip ArchitecturesDokumen4 halamanPerformance Comparison of 2D and 3D Torus Network-on-Chip ArchitecturesJournal of ComputingBelum ada peringkat

- Samsung Globalfoundries 14nm Collaboration FinalDokumen10 halamanSamsung Globalfoundries 14nm Collaboration FinalTheodoros MaragakisBelum ada peringkat

- Analog and Digital Circuit DesignDokumen53 halamanAnalog and Digital Circuit DesignAkhil CMBelum ada peringkat

- Camera Controller Project Report - EDA385Dokumen18 halamanCamera Controller Project Report - EDA385thanhvnptBelum ada peringkat

- Thesis ChandraDokumen60 halamanThesis Chandraprabhu kiranBelum ada peringkat

- Break out Box Transmits Video, CAN Data over Gigabit EthernetDokumen91 halamanBreak out Box Transmits Video, CAN Data over Gigabit EthernetBookWorm1950Belum ada peringkat

- ECE545 Lecture5 Dataflow 6Dokumen15 halamanECE545 Lecture5 Dataflow 6Utpal DasBelum ada peringkat

- Project Alessandro MontanariDokumen69 halamanProject Alessandro MontanariFawaz LabeebBelum ada peringkat

- 8rf Esd GuideDokumen148 halaman8rf Esd GuidesalmanBelum ada peringkat

- Image ProcessingDokumen31 halamanImage ProcessingN180988 MANGARAJU THARUN KUMARBelum ada peringkat

- Using The SDRAMDokumen16 halamanUsing The SDRAMRichard SalavarriaBelum ada peringkat

- Designing With The Nios II Processor and SOPC Builder Exercise ManualDokumen55 halamanDesigning With The Nios II Processor and SOPC Builder Exercise ManualNatthaphob NimpitiwanBelum ada peringkat

- Introduction To VGA: Author: TrumenDokumen14 halamanIntroduction To VGA: Author: TrumenCarlosVillavicencioGBelum ada peringkat

- FPGA-Based Advanced Real Traffic Light Controller SystemDokumen89 halamanFPGA-Based Advanced Real Traffic Light Controller SystemAnil Mahankali100% (1)

- ADPLL Design and Implementation On FPGADokumen6 halamanADPLL Design and Implementation On FPGANavathej BangariBelum ada peringkat

- TLC Using VHDLDokumen30 halamanTLC Using VHDLnaren_cool05Belum ada peringkat

- TFT LCD Display-Camera - 1Dokumen40 halamanTFT LCD Display-Camera - 1thanhvnptBelum ada peringkat

- Zynq DocumentationDokumen82 halamanZynq Documentationgopi krishna100% (1)

- CPUs GPUs AcceleratorsDokumen22 halamanCPUs GPUs AcceleratorsKevin William DanielsBelum ada peringkat

- ASIC Tape Out: Designers' Perspective: C-DAC All Rights Reserved C-DAC/TVM/HDG/Aug'12Dokumen62 halamanASIC Tape Out: Designers' Perspective: C-DAC All Rights Reserved C-DAC/TVM/HDG/Aug'12Gopakumar GnairBelum ada peringkat

- Student's ManualDokumen69 halamanStudent's ManualMichael CagaoanBelum ada peringkat

- Lecture 0: Cpus and Gpus: Prof. Mike GilesDokumen36 halamanLecture 0: Cpus and Gpus: Prof. Mike GilesAashishBelum ada peringkat

- 3D IC TechnologyDokumen33 halaman3D IC TechnologyNikhilAKothariBelum ada peringkat

- Spectral PLL Built-In Self-Test For Integrated Cellular TransmittersDokumen231 halamanSpectral PLL Built-In Self-Test For Integrated Cellular TransmittersChipmuenkBelum ada peringkat

- Ap7202-Asic and FpgaDokumen12 halamanAp7202-Asic and FpgaMOTHI.R MEC-AP/ECEBelum ada peringkat

- ECE448 Lecture8 VGA 2Dokumen105 halamanECE448 Lecture8 VGA 2jenteBelum ada peringkat

- Metamaterial Inspired AntennaDokumen10 halamanMetamaterial Inspired AntennaUmar KhanBelum ada peringkat

- Fpga DSP WhitepaperDokumen15 halamanFpga DSP Whitepaperzohair_r66Belum ada peringkat

- Stereo VisionDokumen214 halamanStereo Visionvandung2290Belum ada peringkat

- JPEG DECODER USING VHDL AND IMPLEMENTING IT ON FPGA SPARTAN 3A KItProject Main Report1Dokumen21 halamanJPEG DECODER USING VHDL AND IMPLEMENTING IT ON FPGA SPARTAN 3A KItProject Main Report1Sachin RathodBelum ada peringkat

- DLD Lab 11 - VGA ControllerDokumen13 halamanDLD Lab 11 - VGA ControllerDania SalmanBelum ada peringkat

- VLSI Technology: History, Usage and Design ProcessDokumen3 halamanVLSI Technology: History, Usage and Design ProcessLearnyzenBelum ada peringkat

- CY8C27443Dokumen45 halamanCY8C27443Sreesh P RBelum ada peringkat

- Computer System Design: System-on-ChipDari EverandComputer System Design: System-on-ChipPenilaian: 2 dari 5 bintang2/5 (1)

- PDIL Notice 12 08Dokumen12 halamanPDIL Notice 12 08Manoj TyagiBelum ada peringkat

- FACT Recruitment Notice 30 04 PDFDokumen17 halamanFACT Recruitment Notice 30 04 PDFSunil PandeyBelum ada peringkat

- BSNL TTA - JE - Current Affairs - Test Paper - BSNL JE 2016Dokumen9 halamanBSNL TTA - JE - Current Affairs - Test Paper - BSNL JE 2016Sunil PandeyBelum ada peringkat

- BSNL JE Electronic Devices and Circuits - 2 - BSNL JE 2016Dokumen8 halamanBSNL JE Electronic Devices and Circuits - 2 - BSNL JE 2016Sunil PandeyBelum ada peringkat

- HPCL GATE 2019 Advertisment PDFDokumen17 halamanHPCL GATE 2019 Advertisment PDFSunil PandeyBelum ada peringkat

- BSNL TTA - Full Syllabus - Test Paper - 2 - BSNL JE 2016Dokumen45 halamanBSNL TTA - Full Syllabus - Test Paper - 2 - BSNL JE 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Je - Full Syllabus - Test Paper - BSNL Je 2016Dokumen41 halamanBSNL Tta - Je - Full Syllabus - Test Paper - BSNL Je 2016Sunil PandeyBelum ada peringkat

- MSME-TECHNOLOGY CENTRE RECRUITMENTDokumen3 halamanMSME-TECHNOLOGY CENTRE RECRUITMENTSunil PandeyBelum ada peringkat

- ECIL hiring Junior Technical Officer, ConsultantsDokumen7 halamanECIL hiring Junior Technical Officer, ConsultantsSandeep GoudBelum ada peringkat

- BSNL TTA - JE - Current Affairs (June) - Test Paper - BSNL JE 2016Dokumen9 halamanBSNL TTA - JE - Current Affairs (June) - Test Paper - BSNL JE 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Specialization - Test Paper - 2 - BSNL Je 2016Dokumen20 halamanBSNL Tta - Specialization - Test Paper - 2 - BSNL Je 2016Sunil PandeyBelum ada peringkat

- BSNL TTA - Full Syllabus - Test Paper - 2 - BSNL JE 2016Dokumen45 halamanBSNL TTA - Full Syllabus - Test Paper - 2 - BSNL JE 2016Sunil PandeyBelum ada peringkat

- BSNL TTA - JE - Current Affairs (June) - Test Paper - BSNL JE 2016Dokumen9 halamanBSNL TTA - JE - Current Affairs (June) - Test Paper - BSNL JE 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Je 2016 - Basic Engineering - Test Paper - BSNL Je 2016Dokumen21 halamanBSNL Tta - Je 2016 - Basic Engineering - Test Paper - BSNL Je 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Dokumen8 halamanBSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Je 2016 - GK & Current Affairs - 2 - BSNL Je 2016Dokumen8 halamanBSNL Tta - Je 2016 - GK & Current Affairs - 2 - BSNL Je 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Je 2016 - GK & Current Affairs - BSNL Je 2016Dokumen10 halamanBSNL Tta - Je 2016 - GK & Current Affairs - BSNL Je 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Je - Full Syllabus - Test Paper - BSNL Je 2016Dokumen41 halamanBSNL Tta - Je - Full Syllabus - Test Paper - BSNL Je 2016Sunil PandeyBelum ada peringkat

- BSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFDokumen8 halamanBSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFSunil PandeyBelum ada peringkat

- BSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFDokumen8 halamanBSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFSunil PandeyBelum ada peringkat

- BSNL TTA - JE 2016 - GK & Current Affairs - BSNL JE 2016 PDFDokumen10 halamanBSNL TTA - JE 2016 - GK & Current Affairs - BSNL JE 2016 PDFSunil PandeyBelum ada peringkat

- BSNL Tta 2016 - GK & English - Test Paper - BSNL Je 2016Dokumen12 halamanBSNL Tta 2016 - GK & English - Test Paper - BSNL Je 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Je 2016 - GK & Current Affairs - 2 - BSNL Je 2016Dokumen8 halamanBSNL Tta - Je 2016 - GK & Current Affairs - 2 - BSNL Je 2016Sunil PandeyBelum ada peringkat

- Network, Filters and Transmission Lines - BSNL JE 2016Dokumen8 halamanNetwork, Filters and Transmission Lines - BSNL JE 2016Sunil PandeyBelum ada peringkat

- BSNL JE Electronic Devices and Circuits - 2 - BSNL JE 2016Dokumen8 halamanBSNL JE Electronic Devices and Circuits - 2 - BSNL JE 2016Sunil PandeyBelum ada peringkat

- Electrical Measurements For GATE & Competitive Exams !Dokumen107 halamanElectrical Measurements For GATE & Competitive Exams !satishfactory82% (11)

- BSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFDokumen8 halamanBSNL TTA - JE 2016 - Microprocessors - BSNL JE 2016 PDFSunil PandeyBelum ada peringkat

- BSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Dokumen8 halamanBSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Sunil PandeyBelum ada peringkat

- BSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Dokumen8 halamanBSNL Tta - Je 2016 - GK & Current Affairs - 6 - BSNL Je 2016Sunil PandeyBelum ada peringkat

- New Lab SyllabusDokumen7 halamanNew Lab SyllabusKeshav PrasathBelum ada peringkat

- What Is IC Programming and IC ProgrammerDokumen18 halamanWhat Is IC Programming and IC ProgrammerjackBelum ada peringkat

- Pg144 Axi GpioDokumen34 halamanPg144 Axi GpioYohanes ErwinBelum ada peringkat

- Altera Opencl Getting StartedDokumen28 halamanAltera Opencl Getting StartedAbed MomaniBelum ada peringkat

- Design a TrustZone-Enabled SoC Using Xilinx VivadoDokumen28 halamanDesign a TrustZone-Enabled SoC Using Xilinx VivadoNguyen Van ToanBelum ada peringkat

- FPGA For Dummies - Part 1 - Historical Introduction PDFDokumen15 halamanFPGA For Dummies - Part 1 - Historical Introduction PDFujwala_512Belum ada peringkat

- MTech VLSI 1st Year Assignment QuestionsDokumen2 halamanMTech VLSI 1st Year Assignment QuestionsG.Kishore Kumar Asst. Professor, ECE DepartmentBelum ada peringkat

- Variable Voltage - Variable Frequency Controller - VVVF - An FPGA ApproachDokumen2 halamanVariable Voltage - Variable Frequency Controller - VVVF - An FPGA ApproachInternational Journal of Innovative Science and Research TechnologyBelum ada peringkat

- 7 Series DSP48E1 Slice: User GuideDokumen58 halaman7 Series DSP48E1 Slice: User GuideRakesh KhannaBelum ada peringkat

- DFT Basics and TypesDokumen17 halamanDFT Basics and TypessenthilkumarBelum ada peringkat

- Edge Detection On FpgaDokumen19 halamanEdge Detection On Fpgaajay kumar sainiBelum ada peringkat

- Professor Mohsin Jamali's ResumeDokumen20 halamanProfessor Mohsin Jamali's Resumeakbisoi1Belum ada peringkat

- Lecture 30,31Dokumen81 halamanLecture 30,31Piyush ParasharBelum ada peringkat

- Snake On An FPGA VerilogDokumen7 halamanSnake On An FPGA Verilogamal baBelum ada peringkat

- FPGA Implementation of A Smart Home LightingDokumen2 halamanFPGA Implementation of A Smart Home LightingSelamiBelum ada peringkat

- Appendix 1-Geochain and ACQ Compatibility Guide (USB Drivers and Driver Signature Enforcement) July 2019Dokumen32 halamanAppendix 1-Geochain and ACQ Compatibility Guide (USB Drivers and Driver Signature Enforcement) July 2019Gary TubridyBelum ada peringkat

- NCCS Technical Report v2 (6093)Dokumen122 halamanNCCS Technical Report v2 (6093)adnanBelum ada peringkat

- FPGA Implementation of DSP AlgorithmsDokumen12 halamanFPGA Implementation of DSP Algorithmsnitin11singhBelum ada peringkat

- Face It Your Brain Isa ComputerDokumen4 halamanFace It Your Brain Isa ComputerEkin DoganBelum ada peringkat

- DSP in FPGADokumen35 halamanDSP in FPGAkrajasekarantutiBelum ada peringkat

- Digital System Design Using VHDL Course OverviewDokumen1 halamanDigital System Design Using VHDL Course OverviewAshutoshBhattBelum ada peringkat

- FPGA IPUG 02001 1 4 12 11 MIPI DSI Display Interface BridgeDokumen32 halamanFPGA IPUG 02001 1 4 12 11 MIPI DSI Display Interface BridgeBruno MatonBelum ada peringkat

- Intel Aero Compute Board GuideDokumen19 halamanIntel Aero Compute Board GuideTimmyBelum ada peringkat

- الالكترونيات الرقمية المتقدمةDokumen4 halamanالالكترونيات الرقمية المتقدمةQUSI E. ABDBelum ada peringkat

- System Level Design of (DSRC) PDFDokumen89 halamanSystem Level Design of (DSRC) PDFBaluvu JagadishBelum ada peringkat

- Gated Clock ConversionDokumen8 halamanGated Clock ConversionKillivalavan KaliyamoorthyBelum ada peringkat

- I/O Buffer Megafunction (ALTIOBUF) User GuideDokumen54 halamanI/O Buffer Megafunction (ALTIOBUF) User GuideSergeyBelum ada peringkat

- FPGA-Based Coin Recognition Using Image ProcessingDokumen14 halamanFPGA-Based Coin Recognition Using Image ProcessingARTHI LAKSHMI K SBelum ada peringkat