Chap. 5 Basic Computer Org. and Design: 5-1 Instruction Codes

Diunggah oleh

Sisay ADDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Chap. 5 Basic Computer Org. and Design: 5-1 Instruction Codes

Diunggah oleh

Sisay ADHak Cipta:

Format Tersedia

Chap. 5 Basic Computer Org.

and Design

5-1

5-1 Instruction Codes

The user of a computer can control the process by means of a program

A program is a set of instructions that specify the operations, operand, the

Instruction

Cycle

sequence(control)

A instruction is a binary code that specifies a sequence of microoperations

Instruction codes together with data are stored in memory(=Stored Program

Concept)

The computer reads each instruction from memory and places it in a

control register. The control then interprets the binary code of the

instruction and proceeds to execute it by issuing a sequence of

microoperations.

Instruction Code :

A group of bits that instruct the computer to perform a specific operation

It is usually divided into parts(refer to Fig. 5-1 instruction format)

Instruction Format

15

12 11

0

Operation Code :

Op. Code

Address

The most basic part of an instruction code

A group of bits that define such operations as add, subtract, multiply, shift, and

complement(bit 12-15 : 24 = 16 distinct operations)

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-2

Stored Program Organization : Fig. 5-1

The simplest way to organize a computer

One processor register : AC(Accumulator)

The operation is performed with the memory operand and the content of AC

Instruction code format with two parts : Op. Code + Address

Exam)

Clear AC, Increment AC,

Complement AC, ...

Op. Code : specify 16 possible operations(4 bit)

Address : specify the address of an operand(12 bit)

If an operation in an instruction code does not need an operand from memory, the rest of the bits in

the instruction(address field) can be used for other purpose( 16 instruction

: Tab. 5-2 , 25 instruction)

Memory : 12 bit = 4096 word(Instruction and Data are stored)

Store each instruction code(program) and operand (data) in 16-bit memory word

Addressing Mode

Immediate operand address :

the second part of an instruction code(address field) specifies an operand

Direct operand address : Fig. 5-2(b)

the second part of an instruction code specifies the address of an operand

I=0 : Direct,

I=1 : Indirect

Indirect operand address : Fig. 5-2(c)

the bits in the second part of the instruction designate an address of a memory word in

which the address of the operand is found (Pointer )

One bit of the instruction code is used to distinguish between a direct and an indirect

address : Fig. 5-2(a)

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-3

Effective Address

The operand address in computation-type instruction or the target address in a

branch-type instruction

5-2 Computer Registers

List of Registers for the Basic Computer : Tab. 5-1

Basic computer registers and memory : Fig. 5-3

Data Register(DR) : hold the operand(Data) read from memory

Accumulator Register(AC) : general purpose processing register

Instruction Register(IR) : hold the instruction read from memory

Temporary Register(TR) : hold a temporary data during processing

Address Register(AR) : hold a memory address, 12 bit width

Program Counter(PC) :

hold the address of the next instruction to be read from memory after the current

instruction is executed

Instruction words are read and executed in sequence unless a branch instruction is

encountered

A branch instruction calls for a transfer to a nonconsecutive instruction in the program

The address part of a branch instruction is transferred to PC to become the address of

the next instruction

To read instruction, memory read cycle is initiated, and PC is incremented by one(next

instruction fetch)

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-4

Input Register(INPR) : receive an 8-bit character from an input device

Output Register(OUTR) : hold an 8-bit character for an output device

Common Bus System

The basic computer has eight registers, a memory unit, and a control unit(in Sec. 54)

Paths must be provided to transfer information from one register to another and

between memory and registers

A more efficient scheme for transferring information in a system with many registers

is to use a common bus(in Sec. 4-3)

The connection of the registers and memory of the basic computer to a common bus

system : Fig. 5-4

The outputs of seven registers and memory are connected to the common bus

The specific output is selected by mux(S0, S1, S2) :

Memory(7), AR(1), PC(2), DR(3), AC(4), IR(5), TR(6)

Device AC INPR OUTR

mux memory register bus

When LD(Load Input) is enable, the particular register receives the data from the bus

Control Input : LD, INC, CLR, Write, Read

Address Register : Address bus ( Bus address data

)

Computer System Architecture

AC DR memory read (p. 146, LDA )

Memory write AC write (p. 147, STA )

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-5

Accumulator(AC) : 3 Path

s2

s1

s0

1) Register Microoperation : clear AC,

shfift AC,

2) Data Register : add DR to AC, and

DR to AC( AC

End carry bit set/reset),

memory READ(DR )

3) INPR : Device

(Adder & Logic )

M e m o r y u n it

4096 16

W r it e

LD

IN R

1

C LR

PC

LD

IN R

C LR

DR

LD

DR AC : s2 s1s0 100( 4), DR (load )

Adder

and

l o g ic

Read

AR

Note) Two microoperations can be

executed at the same time

AC DR : DR Adder & Logic AC (load )

A d d re s s

Bus

IN R

3

C LR

AC

LD

IN R

C LR

IN P R

IR

TR

LD

LD

IN R

C LR

O UTR

LD

C lo c k

1 6 - b it c o m m o n b u s

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-6

5-3 Computer Instruction

3 Instruction Code Formats : Fig. 5-5

Memory-reference instruction

Opcode = 000 110

I=0 : Direct,

I=1 : Indirect

15 14

12

I=0 : 0xxx ~ 6xxx, I=1: 8xxx ~Exxx

11

I Opcode

Address

Register-reference instruction

7xxx (7800 ~ 7001) : CLA, CMA, .

15 14

12

11

0 1 1 1

Register Operation

Input-Output instruction

Fxxx(F800 ~ F040) : INP, OUT, ION, SKI, .

15 14

12

1 1 1 1

Computer System Architecture

11

Symbol

A ND

A DD

LDA

STA

BUN

BSA

ISZ

CLA

CLE

CMS

CME

CIR

CIL

INC

SPA

SNA

SZA

SZE

HLT

INP

OUT

SKI

SKO

ION

IOF

Hex Code

I=0 I=1

0x x x 8x xx

1x x x 9x xx

2x x x Ax x x

3x x x Bx x x

4x x x Cx x x

5x x x Dx x x

6x x x Ex x x

7800

7400

7200

7100

7080

7040

7020

7010

7008

7004

7002

7001

F800

F400

F200

F100

F080

F040

Description

A nd memory w ord to A C

A dd memory w ord to A C

Load memory w ord to A C

Store content of A C in memory

Branch unconditionally

Branch and Save return address

Increment and skip if z ero

Clear A C

Clear E

Complement A C

Comp e

m

Circulate right A C and E

Circulate left AC and E

Increment AC

Skip nex t instruction if A C positive

Skip nex t instruction if A C negativ e

Skip nex t instruction if A C z ero

Skip nex t instruction if E is 0

Halt computer

Input character to A C

Output character from AC

Skip on input flag

Skip on output flag

Interrup

Inter

I/O Operation

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-7

If the computer includes a sufficient number of

Instruction Set Completeness

instructions in each of the following categories

Arithmetic, Logical, and shift : CMA, INC, ..

Moving information to and from memory and AC : STA, LDA

Program control : BUN, BSA, ISZ

Input/Output : INP, OUT

5-4 Timing and Control

Clock pulses

A master clock generator controls the timing for all registers in the basic computer

The clock pulses are applied to all F/Fs and registers in system

The clock pulses do not change the state of a register unless the register is

enabled by a control signal

The control signals are generated in the control unit : Fig. 5-6

The control signals provide control inputs for the multiplexers in the common bus,

control inputs in processor registers, and microoperations for the accumulator

Two major types of control organization

Hardwired Control : Chap. 5

The control logic is implemented with gates, F/Fs, decoders, and other digital circuits

+ Fast operation, - Wiring change(if the design has to be modified)

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-8

Microprogrammed Control : Chap. 7

The control information is stored in a control memory, and the control memory is programmed

to initiate the required sequence of microoperations

+ Any required change can be done by updating the microprogram in control memory, Slow operation

In s t r u c t io n r e g is t e r ( IR )

Timing Signal = 4 X 16 Decoder +

4-bit Sequence Counter

11 - 0

3 8

decoder

7 6 5 4 3 2 1 0

O t h e r in p u t s

D0

D

Exam) Control timing : Fig. 5-7

Sequence Counter is cleared when

D3T4 =1 : D3T4 : SC 0

12

Memory R/W cycle time > Clock cycle

time

, wait

cycle .

Computer System Architecture

.

.

.

C o n tro l

l o g ic

g a te s

C o n tro l

o u tp u ts

T 15

T

.

.

.

Control Unit = Control Logic Gate +

3 X 8 Decoder + Instruction Register

+ Timing Signal

13

15 14

.

.

.

14

4 16

decoder

4 - b it

seq uenc e

c o u n te r

(S C )

.

.

.

Control Unit : Fig. 5-6

15

1 0

In c re m e n t( IN R )

C le a r ( C L R )

C lo c k

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-9

Exam) Register transfer statement : T0 : AR PC

A transfer of the content of PC into AR if timing signal T 0 is active

1) During T0 active, the content of PC is placed onto the bus ( S2 S1S0 )

2) LD(load) input of AR is enabled, the actual transfer occurs at the next positive

transition of the clock(T0 rising edge clock)

T0 : Inactive

3) SC(sequence counter) is incremented : 0000(T0 ) 0000(T1 )

T1 : Active

5-5 Instruction Cycle

Instruction Cycle

1) Instruction Fetch from Memory

2) Instruction Decode

3) Read Effective Address(if indirect addressing mode)

4) Instruction Execution

5) Go to step 1) : Next Instruction[PC + 1]

Instruction Fetch : T0, T1(Fig. 5-8)

Continue

indefinitely

unless HALT

instruction is

encountered

T0 : AR PC

T1 : IR M [ AR], PC PC 1

T0 = 1

T0 : AR PC

1) Place the content of PC onto the bus by making the bus selection inputs S 2S1S0=010

2) Transfer the content of the bus to AR by enabling the LD input of AR

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-10

T1 = 1

T1 : IR M [ AR], PC PC 1

1) Enable the read input memory

2) Place the content of memory onto the bus by making S 2S1S0= 111

3) Transfer the content of the bus to IR by enable the LD input of IR

4) Increment PC by enabling the INR input of PC

Instruction Decode : T2

T1=1

T2 : D0 ,...., D7 Decode IR (12 14), AR IR (0 11), I IR (15)

Op.code

s2

T0=1

s1

Address Di/Indirect

IR(12-14) Fig. 5-6 D0 - D7

IR (12 14)

D7=1

Register(I=0)

A d d re s s

R ead

D 7IT3(Execute)

Read effective

Address

I/O

(I=1)

D 7IT3 (Execute)

D7=0 : Memory Ref. Indirect(I=1)

D 7IT3( AR M [ AR

) ]

Direct (I=0)

nothing in T 3

Register I/O T3 Memory Ref.

T3 Operand effective address

Memory Ref. T4, T5, T6 : Fig.

5-11

Flowchart for instruction cycle(Initial

Configuration) : Fig. 5-9

Computer System Architecture

MM ee mm oo rryy uu nn i itt

Instruction Execution : T3, T4, T5, T6

111

Bus

s0

0

1

0

Chap. 5 Basic Computer Organization and Design

AR

PC

LD

IN R

IR

LD

C lo c k

C om m on bus

Dept. of Info. Of Computer

1

1

1

5-11

Register Ref. Instruction

Address

r = D7IT3 :

IR(i) = Bi

IR(0 -11)

B0 - B11 : 12 Register Ref.

Instruction (Tab. 5-3)

5-6 Memory Ref. Instruction

3X8

Decoder

D7 : Register or I/O = 1

Fig. 5-9 Flowchart for instruction cycle(initial)

S ta rt

SC

0

T0

AR

PC

T1

IR

IR(12,13,14)

= 111

T2

Instruction(Tab. 5-4)

( R e g is te r o r I/O ) = 1

( I/O ) = 1

D0T4 : DR M [ AR ]

PC +1

D e c o d e o p e r a t io n c o d e in I R ( 1 2 - 1 4 )

AR

IR ( 0 - 1 1 ) , I

I( 1 5 )

D6 - D0 : 7 Memory Ref.

AND to AC

M [AR], PC

0 = ( r e g is te r)

0 = ( M e m o ry - re fe re n c e

( in d ir e c t ) = 1

D0T5 : AC AC DR , SC 0

T3

E x e c u te

in p u t- o u tp u t

in s tr u c tio n

SC

0

ADD to AC

D1T4 : DR M [ AR ]

T3

E x e c u te

r e g is t e r - r e f e r e n c e

in s tru c tio n

SC

0

D1T5 : AC AC DR , E Cout , SC 0

0 = ( d ire c t)

T3

AR

M [AR]

T3

N o th in g

E x e c u te

m e m o ry - re fe re n c e

in s tr u c tio n

SC

0

LDA : memory read

D2T4 : DR M [ AR]

D2T5 : AC DR , SC 0

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-12

Fig. 5-10 Example of BSA

STA : memory write

D3T4 : M [ AR] AC , SC 0

PC = 10

PC = 21

BUN : branch unconditionally

D4T4 : PC AR, SC 0

BSA : branch and save return address

135 21(return address)

PC = 136

Subroutine

D5T4 : M [ AR] PC , AR AR 1

D5T5 : PC AR, SC 0

0

BSA 135

next instruction

BUN 135

Return Address : save return address ( 135

21 )

D5T4 : M [135] 21( PC ), 136( AR) 135 1

Subroutine Call : Fig. 5-10

ISZ : increment and skip if zero

D5T5 : 136( PC ) 136( AR), SC 0

D6T4 : DR M [ AR ]

D6T5 : DR DR 1

D6T6 : M [ AR ] DR , if ( DR 0) then ( PC PC 1), SC 0

Control Flowchart : Fig. 5-11

Flowchart for the 7 memory reference instruction

The longest instruction : ISZ(T6)

3 bit Sequence Counter ( 4 )

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-13

5-7 Input-Output and Interrupt

Input-Output Configuration : Fig. 5-12

Input Register(INPR), Output Register(OUTR)

These two registers communicate with a communication interface serially and with the

AC in parallel

Each quantity of information has eight bits of an alphanumeric code

1 : Ready

0 : Not ready

Input Flag(FGI), Output Flag(FGO)

FGI : set when INPR is ready( ), clear when INPR is empty

FGO : set when operation is completed( ), clear when output device is

in the process of printing

Input-Output Instruction : Tab. 5-5

Address

p = D7IT3 :

IR(i) = Bi

IR(6 -11)

B6 - B11 : 6 I/O Instruction

Program Interrupt

I/O Transfer Modes

1) Programmed I/O, 2) Interrupt-initiated I/O, 3) DMA, 4) IOP

2) Interrupt-initiated I/O (FGI FGO 1 Int. )

Maskable Interrupt ( ION IOF Int. mask )

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-14

Interrupt Cycle : Fig. 5-13

In s tr u c tio n c y c le

During the execute phase, IEN is checked by the control

In te r r u p t c y c le

=1

F e tc h a n d d e c o d e

in s t r u c t io n

IEN = 0 : the programmer does not want to use the interrupt,

so control continues with the next instruction cycle

IEN = 1 : the control circuit checks the flag bit, If either flag

set to 1, R F/F is set to 1

S to r e r e tu r n a d d r e s s

in lo c a t io n 0

M [ 0]

PC

=0

IE N

E x e c u te

in s t r u c t io n

=1

=1

B r a n c h to lo c a tio n 1

PC

1

FG I

=0

At the end of the execute phase, control checks the value of R

=0

=1

R = 0 : instruction cycle

R = 1 : Instruction cycle

IE N

R

FG O

0

0

=0

Demonstration of the interrupt cycle : Fig. 5-14

The memory location at address 0 as the place for storing the return address

Interrupt Branch to memory location 1

Interrupt cycle IEN=0 ( ISR Interrupt

ISR ION )

0

PC = 1

The condition

for R = 1

' ' '

T0T1 T2 ( IEN )( FGI FGO) : R 1

Modified Fetch Phase

Modified Fetch and Decode Phase

Save Return

Address(PC) at 0

Jump to 1(PC=1)

Interrupt

Here

256(return address)

0

BUN 1120

Main Program

255

256

RT0 : AR 0, TR PC

RT1 : M [ AR ] TR, PC 0

RT2 : PC PC 1, IEN 0, R 0, SC 0

Computer System Architecture

Interrupt

1120

Chap. 5 Basic Computer Organization and Design

Service Routine

1

BUN

Dept. of Info. Of Computer

5-15

5-8 Complete Computer Description

The final flowchart of the instruction cycle : Fig. 5-15

The control function and microoperation : Tab. 5-6

5-9 Design of Basic Computer

The basic computer consists of the following hardware components

1. A memory unit with 4096 words of 16bits

2. Nine registers : AR, PC, DR, AC, IR, TR, OUTR, INPR, and SC(Fig. 2-11)

3. Seven F/Fs : I, S, E, R, IEN, FGI, and FGO

4. Two decoder in control unit : 3 x 8 operation decoder, 4 x 16 timing

Section

decoder(Fig. 5-6)

5. A 16-bit common bus(Fig. 5-4)

6. Control Logic Gates : Fig. 5-6 Box Control Output

7. Adder and Logic circuit connected to the AC input

Control Logic Gates

1. Signals to control the inputs of the nine registers

2. Signals to control the read and write inputs of memory

3. Signals to set, clear, or complement the F/Fs

4. Signals for S 2 S1 S0 to select a register for the bus

5. Signals to control the AC adder and logic circuit

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-16

Register Control : AR

Control inputs of AR : LD, INR, CLR

Find all the statements that change the AR

AR ?

in Tab. 5-6

R' T0 : AR PC

Control functions

R' T1 : AR IR (0 11)

LD( AR) R' T0 R' T1 D7 ' IT3 D7 ' IT3 : AR M [ AR]

CLR( AR) RT0

RT0 : AR 0

INR ( AR) D5T4

12

F ro m B u s

LD

D '7

I

T3

Computer System Architecture

C lo c k

R

D

T4

D5T4 : AR AR 1

F/F Control : IEN IEN ?

Control functions

RT2 : IEN 0

C LR

T0

? M [ AR]

READ R' T1 D7 ' IT3 ( D0 D1 D2 D3 )T4

pB6 : IEN 0

IN R

To Bus

T2

Memory Control : READ

M [ AR ] ?

Control inputs of Memory : READ, WRITE

Find all the statements that specify a read operation in Tab. 5-6

Control function

pB7 : IEN 1

12

AR

D '7

I

T3

J

0

1

KQ(t+1)

1

0

0

1

B7

SET

C lo c k

B6

IE N

C LR

R

T2

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-17

Bus Control

Encoder for Bus Selection : Tab. 5-7

S 0 = x 1 + x 3 + x5 + x7

S 1 = x 2 + x 3 + x6 + x7

S 0 = x 4 + x 5 + x5 + x7

x1 = 1 :

Bus AR Find ? AR

D4T4 : PC AR

D5T5 : PC AR

Control Function :

x2 = 1 :

x1 D4T4 D5T5

Bus PC Find ? PC

x1

x2

x3

x4

x5

x6

x7

S0

Encoder

S1

S2

Multiplexer

Bus Select

Input

x7 = 1 :

Same Bus

as Memory

Read

Memory

Control Function :

Find ? M [ AR]

x7 R ' T1 D7 ' IT3 ( D0 D1 D2 D3 )T4

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-18

5-10 Design of Accumulator Logic

Circuits associated with AC : Fig. 5-19

Fig. 5-21

Fig. 2-11

16

16

F ro m D R

8

F r o m IN P R

Adder and

lo g ic

c ir c u it

A c c u m u la t o r

r e g is te r

(A C )

16

LD

Fig. 5-20

Computer System Architecture

IN R

16

To Bus

C L R C lo c k

C o n tro l

g a te s

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-19

Control of AC : Fig. 5-20

Find the statement that change the AC : AC ?

F ro m a d d e r

a n d lo g ic

D

AND

16

AC

LD

IN R

C LR

To Bus

C lo c k

T5

D0T5 : AC AC DR

D1T5 : AC AC DR

D2T5 : AC DR

pB11 : AC (0 7) INPR

16

ADD

DR

T5

LD

rB9 : AC AC

IN P R

B 11

r

rB7 : AC shr AC , AC (15) E

rB6 : AC shr AC , AC (0) E

rB11 : AC 0

CLR

rB5 : AC AC 1

INR

C O M

SHR

SHL

IN C

C LR

B 11

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

5-20

Adder and Logic Circuit : Fig. 5-21 ( 16 bit = 16 )

D R ( i)

A C ( i)

( O u tp u t o f O R g a te in F ig . 5 - 2 0 )

AND

C

ADD

FA

C

i+ 1

F ro m

IN P R

b it ( i)

J

0

1

LD

Ii ( F ig . 2 - 1 1 )

DR

KQ(t+1)

1

0

0

1

A C ( i)

IN P R

C lo c k

C O M

SHR

* Fig. 2-11

Increment, Clear,

Count

A C ( i+ 1 )

SHL

A C ( i- 1 )

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

Mano Machine

Integration !

5-21

Fig. 5-4 : Common Bus(p.130)

Fig. 2-11 : Register(p. 59)

Fig. 5-6 : Control Unit(p. 137)

Fig. 5-16, 17,18 : Control Logic Gate(p.161- 163)

Fig. 5-4 Component Control Input

Register, Memory, F/Fs, Bus Selection

Fig. 5-20 : AC control(p.165)

Fig. 5-21 : Adder and Logic(p.166)

Due Date : 1

Computer System Architecture

Chap. 5 Basic Computer Organization and Design

Dept. of Info. Of Computer

Anda mungkin juga menyukai

- Chapter 4Dokumen71 halamanChapter 4Yididiya TilahunBelum ada peringkat

- Chap. 5 Basic Computer Org. and Design: 5-1 Instruction CodesDokumen21 halamanChap. 5 Basic Computer Org. and Design: 5-1 Instruction CodesVedant BondeBelum ada peringkat

- CSA Notes Unit 3Dokumen43 halamanCSA Notes Unit 3BADMANBelum ada peringkat

- Basic Computer OrganizationDokumen23 halamanBasic Computer OrganizationKibrom HaftuBelum ada peringkat

- Lec12 Basic Computer OrganizationDokumen75 halamanLec12 Basic Computer OrganizationAya AbdAllah AmmarBelum ada peringkat

- Instruction CodesDokumen35 halamanInstruction Codesanilk_patiBelum ada peringkat

- Fundamentals of Processor Design: Using Figures From by Hamblen and FurmanDokumen35 halamanFundamentals of Processor Design: Using Figures From by Hamblen and Furmanwilliamjamir2295Belum ada peringkat

- Microprocessor BC 0046Dokumen50 halamanMicroprocessor BC 0046ubuntu_linuxBelum ada peringkat

- Chapter 5Dokumen53 halamanChapter 5binaboss24Belum ada peringkat

- Chapter 3 - CO - BIM - III PDFDokumen11 halamanChapter 3 - CO - BIM - III PDFBhola ShroffBelum ada peringkat

- IT18302 - Computer Organization and Architecture Lecture Notes Unit 1-Basic Computer Organization and DesignDokumen17 halamanIT18302 - Computer Organization and Architecture Lecture Notes Unit 1-Basic Computer Organization and DesignNAVINRAJ RSBelum ada peringkat

- Introduction To MicroprocessorDokumen39 halamanIntroduction To MicroprocessorDeepika BansalBelum ada peringkat

- Timing and Control Instruction Cycle Memory Reference Instructions Input-Output and Interrupt Complete Computer DescriptionDokumen38 halamanTiming and Control Instruction Cycle Memory Reference Instructions Input-Output and Interrupt Complete Computer DescriptionGeorgian ChailBelum ada peringkat

- Hapter Outline: Cpu Memory Input and Output UnitDokumen34 halamanHapter Outline: Cpu Memory Input and Output UnittoswaroopBelum ada peringkat

- Coa 2nd LessonDokumen17 halamanCoa 2nd LessonMukeshBelum ada peringkat

- Morris ManoDokumen29 halamanMorris Manojupillisjohn_9650432100% (4)

- SsDokumen60 halamanSsponns100% (1)

- Prepared By: Mohd Norfitri Nordin Faculty Information Communication TechnologyDokumen32 halamanPrepared By: Mohd Norfitri Nordin Faculty Information Communication TechnologyIntan SyuhadaBelum ada peringkat

- Hardwired ControlDokumen6 halamanHardwired Controlapi-19967001Belum ada peringkat

- Unit - Iv 4.0) Introduction: Digital Logic and Computer OrganizationDokumen18 halamanUnit - Iv 4.0) Introduction: Digital Logic and Computer OrganizationJit AggBelum ada peringkat

- CH 5 AdditionalDokumen34 halamanCH 5 AdditionalKriti GautamBelum ada peringkat

- Basic Computer Organization and DesignDokumen20 halamanBasic Computer Organization and DesignMag Creation100% (1)

- CHAPTER 5, Inside Digital DesignDokumen33 halamanCHAPTER 5, Inside Digital DesignSyed Abdullah RizviBelum ada peringkat

- Ch01 Basic Concepts and Computer EvolutionDokumen36 halamanCh01 Basic Concepts and Computer EvolutionMark ShanBelum ada peringkat

- Co & MPDokumen31 halamanCo & MPSainikshay ReddyBelum ada peringkat

- GFG - CoaDokumen203 halamanGFG - CoaKaran100% (1)

- Computer Architecture - Chapt 5Dokumen45 halamanComputer Architecture - Chapt 5for_booksBelum ada peringkat

- Microprocessor Systems I 1Dokumen28 halamanMicroprocessor Systems I 1Lester Yrwiz V. RamosBelum ada peringkat

- Introduction To MicrocontrollersDokumen52 halamanIntroduction To MicrocontrollersSanjayaRangaLSenavirathnaBelum ada peringkat

- Coa 5Dokumen37 halamanCoa 5pahujahimankBelum ada peringkat

- Basic Computer Organization and DesignDokumen42 halamanBasic Computer Organization and DesignSachin MalikBelum ada peringkat

- Basic Computer Organisation and DesignDokumen5 halamanBasic Computer Organisation and DesignAadhya JyothiradityaaBelum ada peringkat

- ECE 5570 Design of Reconfigurable Digital Machines Design of 16 Bit RISC ProcessorDokumen11 halamanECE 5570 Design of Reconfigurable Digital Machines Design of 16 Bit RISC Processorpitler999Belum ada peringkat

- Vss Paper MicroprocessorDokumen4 halamanVss Paper MicroprocessorAnil JhaBelum ada peringkat

- Unit - Ii 2.0) Introduction: Digital Logic and Computer OrganizationDokumen32 halamanUnit - Ii 2.0) Introduction: Digital Logic and Computer OrganizationJit AggBelum ada peringkat

- Sap-1 ArchitectureDokumen9 halamanSap-1 ArchitectureAshna100% (1)

- Basic Computer ch-5Dokumen48 halamanBasic Computer ch-5Subbu ReddyBelum ada peringkat

- Preliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Dari EverandPreliminary Specifications: Programmed Data Processor Model Three (PDP-3) October, 1960Belum ada peringkat

- Introduction To Microprocessors: Gopikrishnan G Asst. Prof. Elx & TcomDokumen29 halamanIntroduction To Microprocessors: Gopikrishnan G Asst. Prof. Elx & Tcomsahil babaniBelum ada peringkat

- Microprocessor Architecture and Assembly Language: Week # 1Dokumen6 halamanMicroprocessor Architecture and Assembly Language: Week # 1Bibah GeeBelum ada peringkat

- Following Is The List of Some of The Most Common Registers Used in A Basic ComputerDokumen12 halamanFollowing Is The List of Some of The Most Common Registers Used in A Basic Computerrajesh5500Belum ada peringkat

- Elec 263 Computer Architecture and OrganizationDokumen4 halamanElec 263 Computer Architecture and Organizationbebo_ha2008Belum ada peringkat

- CH 5Dokumen46 halamanCH 5Vijaya GoelBelum ada peringkat

- Programming 8-Bit Pic Microcontrollers Inc: Martin Bates Elsevier 2008Dokumen30 halamanProgramming 8-Bit Pic Microcontrollers Inc: Martin Bates Elsevier 2008SonyKurupBelum ada peringkat

- Basic Computer Organization and DesignDokumen46 halamanBasic Computer Organization and DesignKirollos ShawkyBelum ada peringkat

- Computer Organization-Basic Processing UnitDokumen48 halamanComputer Organization-Basic Processing Unitwww.entcengg.com100% (2)

- CSA CompleteDokumen196 halamanCSA CompleteNishant SehgalBelum ada peringkat

- 2 16 1350130228 7. Flexible Wireless DataDokumen6 halaman2 16 1350130228 7. Flexible Wireless DataSumeet SauravBelum ada peringkat

- Chapter 3: Computer Instructions: ObjectivesDokumen7 halamanChapter 3: Computer Instructions: ObjectivesSteffany RoqueBelum ada peringkat

- Unit IV Cpu OrganizationDokumen124 halamanUnit IV Cpu Organizationrajendra.rajuBelum ada peringkat

- E 4160 Introduction To MicroprocessorDokumen39 halamanE 4160 Introduction To MicroprocessorSyaz ZanaBelum ada peringkat

- SAP-1 (Simple As Possible-1) Computer ArchitectureDokumen8 halamanSAP-1 (Simple As Possible-1) Computer ArchitecturesaikotBelum ada peringkat

- Cs/Coe 1541: Single and Multi-Cycle ImplementationsDokumen93 halamanCs/Coe 1541: Single and Multi-Cycle ImplementationsBobo JooBelum ada peringkat

- Computer Architecture & Organization - Control Unit ALU Register Set Accumulator RISC CISC STACK Register Stack Memory StackDokumen3 halamanComputer Architecture & Organization - Control Unit ALU Register Set Accumulator RISC CISC STACK Register Stack Memory StackWaqas GhaffariBelum ada peringkat

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDari EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationBelum ada peringkat

- PLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Dari EverandPLC: Programmable Logic Controller – Arktika.: EXPERIMENTAL PRODUCT BASED ON CPLD.Belum ada peringkat

- Bitcoin Price Prediction 5 - ColaboratoryDokumen5 halamanBitcoin Price Prediction 5 - ColaboratorySisay ADBelum ada peringkat

- Chapter OneDokumen27 halamanChapter OneSisay ADBelum ada peringkat

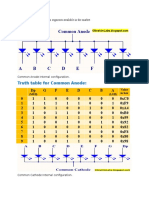

- Truth Table For Common AnodeDokumen3 halamanTruth Table For Common AnodeSisay ADBelum ada peringkat

- April 16th Presentation-JSDokumen7 halamanApril 16th Presentation-JSSisay ADBelum ada peringkat

- Advanced Design For Robot in Mars ExplorationDokumen6 halamanAdvanced Design For Robot in Mars ExplorationSisay ADBelum ada peringkat

- Introduction To Artificial Intelligence: By: Getaneh TDokumen55 halamanIntroduction To Artificial Intelligence: By: Getaneh TSisay ADBelum ada peringkat

- Interface LCD and Keypad With 8051 MicroDokumen7 halamanInterface LCD and Keypad With 8051 MicroSisay ADBelum ada peringkat

- Office2007 Excel TrainfffingDokumen65 halamanOffice2007 Excel TrainfffingSisay ADBelum ada peringkat

- 0 BBDokumen6 halaman0 BBSisay ADBelum ada peringkat

- FishggDokumen63 halamanFishggSisay ADBelum ada peringkat

- Medal Log 20220907Dokumen14 halamanMedal Log 20220907ryannqii10Belum ada peringkat

- Benchman 4000 WIN ManualDokumen250 halamanBenchman 4000 WIN ManualAndres LlerenaBelum ada peringkat

- RK3566 Brief DatasheetDokumen3 halamanRK3566 Brief DatasheetДраго ТитевBelum ada peringkat

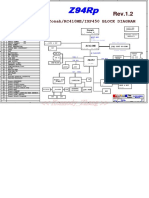

- Z94RP Rev 1 2Dokumen45 halamanZ94RP Rev 1 2NDCEBelum ada peringkat

- Padlock User Manual V1.0Dokumen2 halamanPadlock User Manual V1.0florenciaBelum ada peringkat

- Wiring DiagramDokumen4 halamanWiring Diagramivo rodriguesBelum ada peringkat

- HP Pavilion G4 G6 G7 Quanta R13 DA0R13MB6E0, DA0R13MB6E1 REV E UMA-DIS Schematics PDFDokumen39 halamanHP Pavilion G4 G6 G7 Quanta R13 DA0R13MB6E0, DA0R13MB6E1 REV E UMA-DIS Schematics PDFeneid jimenez0% (1)

- DS2431 PDFDokumen27 halamanDS2431 PDFSudhagarSubbiyanBelum ada peringkat

- TUTORIAL - How To Install EmuELEC Onto Android TV BoxDokumen13 halamanTUTORIAL - How To Install EmuELEC Onto Android TV Boxrusli77Belum ada peringkat

- Imp Datastage NewDokumen158 halamanImp Datastage NewDinesh Sanodiya100% (1)

- MAME RetroPie - RetroPie-Setup WikiDokumen4 halamanMAME RetroPie - RetroPie-Setup WikiBobbyBelum ada peringkat

- DX DiagDokumen11 halamanDX DiagAhmed HusseinBelum ada peringkat

- Kode Nama Harga Jual: Notebook AcerDokumen4 halamanKode Nama Harga Jual: Notebook AcerAkademi Kebidanan Bina Sehat NusantaraBelum ada peringkat

- Face Recognition Based Door Unlocking System Using Raspberry PiDokumen5 halamanFace Recognition Based Door Unlocking System Using Raspberry PiAzmi AbdulbaqiBelum ada peringkat

- The Soul of A New Machine - Chapter 9-10Dokumen5 halamanThe Soul of A New Machine - Chapter 9-10Bhimo BhaskoroBelum ada peringkat

- MCQ Books List 1Dokumen1 halamanMCQ Books List 1BelagaviBelum ada peringkat

- Brand Awareness of Acer LaptopsDokumen68 halamanBrand Awareness of Acer LaptopsPratik Gajjar100% (2)

- LogDokumen143 halamanLogBelly VictoriaBelum ada peringkat

- EN25F16 16 Megabit Serial Flash Memory With 4kbytes Uniform SectorDokumen36 halamanEN25F16 16 Megabit Serial Flash Memory With 4kbytes Uniform SectorPeter FreimannBelum ada peringkat

- P5Q Deluxe EFI BIOS User Guide v1.2Dokumen2 halamanP5Q Deluxe EFI BIOS User Guide v1.2Gannon101Belum ada peringkat

- HD Matrix Decoder ZXNVM C9112-H-E: FeaturesDokumen1 halamanHD Matrix Decoder ZXNVM C9112-H-E: FeaturesAlexander MontoyaBelum ada peringkat

- PLC Hardware ComponentsDokumen37 halamanPLC Hardware ComponentsPANDARAVEL KANNAN MBelum ada peringkat

- QJ71MB91 ManualDokumen356 halamanQJ71MB91 Manualboochuck87Belum ada peringkat

- Microprocessor System Design: Three Key Technologies For Embedded SystemsDokumen4 halamanMicroprocessor System Design: Three Key Technologies For Embedded SystemsvardhanBelum ada peringkat

- Roland Fantom x6Dokumen66 halamanRoland Fantom x6Diego RosalesBelum ada peringkat

- S7-300 CPU SpecificationDokumen190 halamanS7-300 CPU Specificationdragon_tudvn100% (1)

- Data Center Disaster RecoveryDokumen48 halamanData Center Disaster Recoverysanthoshbr1975Belum ada peringkat

- 25U6435F MacronixDokumen92 halaman25U6435F MacronixAdrian EGBelum ada peringkat