8237

Diunggah oleh

Basheer V.P0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

85 tayangan14 halaman8237

Hak Cipta

© © All Rights Reserved

Format Tersedia

PPT, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen Ini8237

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PPT, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

85 tayangan14 halaman8237

Diunggah oleh

Basheer V.P8237

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PPT, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 14

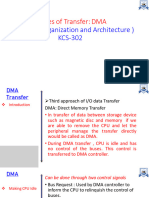

DMA

Direct Memory Access

Introduction to 8237

DMA Controller

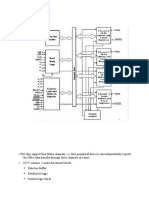

A DMA controller interfaces with several peripherals that may request

DMA.

The controller decides the priority of simultaneous DMA requests

communicates with the peripheral and the CPU, and provides memory

addresses for data transfer.

DMA controller commonly used with 8086 is the 8237 programmable

device.

The 8237 is in fact a special-purpose microprocessor.

Normally it appears as part of the system controller chip-sets.

The 8237 is a 4-channel device. Each channel is dedicated to a specific

peripheral device and capable of addressing 64 K bytes section of

memory.

Intel 8237A DMA Controller

Interfaces to 80x86 family and DRAM

When DMA module needs buses it sends HOLD signal to

processor

CPU responds HLDA (hold acknowledge)

DMA module can use buses

E.g. transfer data from memory to disk

1. Device requests service of DMA by pulling DREQ (DMA request) high

2. DMA puts high on HRQ (hold request),

3. CPU finishes present bus cycle (not necessarily present instruction)

and puts high on HDLA (hold acknowledge). HOLD remains active for

duration of DMA

4. DMA activates DACK (DMA acknowledge), telling device to start

transfer

5. DMA starts transfer by putting address of first byte on address bus and

activating MEMR; it then activates IOW to write to peripheral. DMA

decrements counter and increments address pointer. Repeat until

count reaches zero

6. DMA deactivates HRQ, giving bus back to CPU

DMA

Some important signal pins:

DREQ3 DREQ0 (DMA request): Used to

request a DMA transfer for a particular DMA

channel.

DACK3 DACK0 (DMA channel

acknowledge): Acknowledges a channel

DMA request from a device.

HRQ (Hold request): Requests a DMA

transfer.

HLDA (Hold acknowledge) signals the

8237 that the microprocessor has

relinquished control of the address, data

and control buses.

DMA

Some important signal pins:

A7 A4 : address pins are outputs that

provide part of the DMA transfer address

during a DMA operation.

DB0 DB7 : data bus, connected to

microprocessor and are used during the

programming DMA controller.

Internal registers:

CAR : The current address register, is used to hold the 16-bit

memory address used for the DMA transfer.

CWCR : The current word count register, programs a channel for

the number of bytes (up to 64K) transferred during a DMA action.

BA & BWC : The base address and base word count , registers

are used when auto-initialization is selected for a channel. In this

mode, their contents will be reloaded to the CAR and CWCR after

the DMA action is completed.

The command register (CR) programs the operation of the

8237 DMA controller

Each channel has its own CAR, CWCR, BA and BWC.

MR : The mode register, programs the mode of operation for a

channel. Each channels has its own mode register (RD/WR-INC/DEC..)

RR : The request register, is used to request a DMA transfer

via software, which is very useful in memory-to-memory

Transfers where external signals is not available for DMA transfer

MRSR : The mask register set/reset, sets or clears the channel

mask to disable or enable particular DMA channels. If the mask is set,

The channel is disabled

MSR : The mask register, clears or sets all of the masks with

one command instead of individual channels as with the

MRSR.

SR : The status register, shows the status of each DMA channel. TC

Bits indicate, terminal count

Modes of Operation

Single Transfer Mode

In Single Transfer mode the device is programmed to make one

transfer only.

The word count will be decremented and the address

decremented or incremented following each transfer.

When the word count ``rolls over'' from zero to FFFFH, a

Terminal Count (TC) will cause an Auto initialize if the channel

has been programmed to do so.

Block Transfer Mode

In Block Transfer mode the device is activated by DREQ to

continue making transfers during the service until a TC, caused

by word count going to FFFFH, or an external End of Process

(EOP) is encountered.

DREQ need only be held active until DACK becomes active.

Again, an Autoinitialization will occur at the end of the service

if the channel has been programmed for it.

Demand Transfer Mode:

In Demand Transfer mode the device is programmed to continue

making transfers until a TC or external EOP is encountered or until

DREQ goes inactive.

Transfers may continue until the I/O device has exhausted its data

capacity. the DMA service can be re-established by means of a DREQ.

During the time between services when the microprocessor is

allowed to operate, the intermediate values of address and word

count are stored in the 8237A Current Address and Current Word

Count registers.

EOP can cause an Autoinitialize at the end of the service. EOP is

generated either by TC or by an external signal.

DMA

Cascade Mode:

more than one 8237A

together for simple system

expansion.

The HRQ and HLDA signals

from the additional 8237A are

connected to the DREQ and

DACK signals of a channel of

the initial 8237A.

This allows the DMA requests

of the additional device to

propagate through the priority

network circuitry of the

preceding device.

Advanced Microprocessor 14

Anda mungkin juga menyukai

- Practical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationDari EverandPractical Reverse Engineering: x86, x64, ARM, Windows Kernel, Reversing Tools, and ObfuscationBelum ada peringkat

- 8237 DMA ControllerDokumen41 halaman8237 DMA ControllerDebakantaKarBelum ada peringkat

- Direct Memory Access (DMA) Operation and DMA ControllerDokumen60 halamanDirect Memory Access (DMA) Operation and DMA ControllerAanchalAdhikari100% (1)

- Presentation Microprocessors: 8237 DMA ControllerDokumen13 halamanPresentation Microprocessors: 8237 DMA ControllerMimansha SharmaBelum ada peringkat

- DM A ControllerDokumen5 halamanDM A ControllerDoris MwimaliBelum ada peringkat

- 8257 DmaDokumen29 halaman8257 DmanupurnehaBelum ada peringkat

- Microprocessor DMADokumen14 halamanMicroprocessor DMAvivek_may12Belum ada peringkat

- Direct Memory AccessDokumen3 halamanDirect Memory AccessAmisha SinghBelum ada peringkat

- Dma 8237Dokumen51 halamanDma 8237Sanket ChavanBelum ada peringkat

- DMA and DMA ControllerDokumen14 halamanDMA and DMA ControllerGaurav JaiswalBelum ada peringkat

- 8237 DMA Controller: Microprocessor & InterfacingDokumen14 halaman8237 DMA Controller: Microprocessor & Interfacingbharti.sukhija21Belum ada peringkat

- DMA Controller - 8257/8237Dokumen16 halamanDMA Controller - 8257/8237infinity InfinityBelum ada peringkat

- Dma 8257Dokumen12 halamanDma 8257Ishmeet KaurBelum ada peringkat

- 8237Dokumen7 halaman8237Laxmanaa GajendiranBelum ada peringkat

- Direct Memory Access (DMA) and The DMA Controller (DMAC) 8237Dokumen24 halamanDirect Memory Access (DMA) and The DMA Controller (DMAC) 8237abu sayedBelum ada peringkat

- The Dma Controller 8257 and 8237 .Dokumen78 halamanThe Dma Controller 8257 and 8237 .BETHWEL KIPROTICHBelum ada peringkat

- 8237 DMA ControllerDokumen22 halaman8237 DMA ControllerAbdullah AhmedBelum ada peringkat

- DMA Mod4 PDFDokumen20 halamanDMA Mod4 PDFAjnamol N RBelum ada peringkat

- SYSC3601 Microprocessor Systems: Unit 8: Direct Memory Access (DMA)Dokumen14 halamanSYSC3601 Microprocessor Systems: Unit 8: Direct Memory Access (DMA)josephBelum ada peringkat

- 8237 DMA ControllerDokumen11 halaman8237 DMA ControllerRojot SahaBelum ada peringkat

- 8257 DMA Controller:: To Fetch The Instruction To Decode The Instruction and To Execute The InstructionDokumen25 halaman8257 DMA Controller:: To Fetch The Instruction To Decode The Instruction and To Execute The Instructionsatyanarayana12Belum ada peringkat

- Irect Emory Address AND Dma Controller: By: Vrunda Shah Vardhani Vangara Rutvi Shah Kangan ShuklaDokumen10 halamanIrect Emory Address AND Dma Controller: By: Vrunda Shah Vardhani Vangara Rutvi Shah Kangan Shuklavrunda shahBelum ada peringkat

- Unit 5Dokumen26 halamanUnit 5veenayak sirohiBelum ada peringkat

- Microprocessor - 8257 DMA Controller TutorialspointDokumen5 halamanMicroprocessor - 8257 DMA Controller Tutorialspointpreethiu19phd036Belum ada peringkat

- DMA ControllerDokumen9 halamanDMA ControllerVanga Shiva Rama KrishnaBelum ada peringkat

- DMA Controller - 8237Dokumen9 halamanDMA Controller - 8237Umesh Harihara sudanBelum ada peringkat

- Direct Memory Access (DMA)Dokumen9 halamanDirect Memory Access (DMA)Doris MwimaliBelum ada peringkat

- 8237 Dma ControllerDokumen13 halaman8237 Dma ControllerAmanda AvilaBelum ada peringkat

- Programmable Interval Timer 8253: Architecture of 8253Dokumen13 halamanProgrammable Interval Timer 8253: Architecture of 8253Srikanth KodothBelum ada peringkat

- The Real Time ClockDokumen8 halamanThe Real Time Clockrobern ndoloBelum ada peringkat

- Direct Memory Access (DMA) : Burst ModeDokumen7 halamanDirect Memory Access (DMA) : Burst ModeAnand ReddyBelum ada peringkat

- Direct Memory Access and DMA-controlled I/ODokumen3 halamanDirect Memory Access and DMA-controlled I/ODeepak SinghBelum ada peringkat

- 8257 - Microprocessors and Microcontrollers NotesDokumen25 halaman8257 - Microprocessors and Microcontrollers NotesFathima HeeraBelum ada peringkat

- 8257 Dmac RNMDokumen32 halaman8257 Dmac RNMRajBelum ada peringkat

- Dma Operation in An 8086 Based SystemDokumen3 halamanDma Operation in An 8086 Based SystemSowmya PBelum ada peringkat

- 8257 DmaDokumen6 halaman8257 DmaAdarsh AmzeBelum ada peringkat

- 8237 DmaDokumen20 halaman8237 DmaNil AgrawalBelum ada peringkat

- Pin Diagram of 8086Dokumen21 halamanPin Diagram of 8086adithya123456100% (5)

- DMA Is Implemented Using A DMA ControllerDokumen35 halamanDMA Is Implemented Using A DMA Controllerparveshtext100% (1)

- DMADokumen17 halamanDMAvpmanimcaBelum ada peringkat

- DmaDokumen16 halamanDmaavireddy1Belum ada peringkat

- The Dma Chip 8237aDokumen24 halamanThe Dma Chip 8237aatorresh090675Belum ada peringkat

- Microprocessor - 8257 DMA ControllerDokumen5 halamanMicroprocessor - 8257 DMA ControllerFraud PriyanBelum ada peringkat

- Unit 6Dokumen16 halamanUnit 6sung hooBelum ada peringkat

- DMA Controller 8237:: Comparison of 8257 and 8237Dokumen15 halamanDMA Controller 8237:: Comparison of 8257 and 8237SuryaRajitha InpBelum ada peringkat

- Pin Diagram of 8086Dokumen21 halamanPin Diagram of 8086Radha SudheeraBelum ada peringkat

- Direct Memory Access With DMA Controller 8257Dokumen4 halamanDirect Memory Access With DMA Controller 8257SoldsBelum ada peringkat

- Dma 8257Dokumen11 halamanDma 8257amruthakollaraBelum ada peringkat

- 01DMA Controller-8257Dokumen37 halaman01DMA Controller-8257Vedant BohraBelum ada peringkat

- 8237 DmaDokumen19 halaman8237 DmaadiyaljatBelum ada peringkat

- FALLSEM2021-22 ECE3004 TH VL2021220101856 Reference Material I 20-10-2021 Module 5 - 3 DMADokumen31 halamanFALLSEM2021-22 ECE3004 TH VL2021220101856 Reference Material I 20-10-2021 Module 5 - 3 DMABharath P NairBelum ada peringkat

- DMA Controller - DMA Controller 8257: Internal Architecture of 8257Dokumen8 halamanDMA Controller - DMA Controller 8257: Internal Architecture of 8257LAVANYA DURAISAMYBelum ada peringkat

- DMA Controller: Motorola DSP56300 Family Manual 1Dokumen28 halamanDMA Controller: Motorola DSP56300 Family Manual 1Youssef AadelBelum ada peringkat

- NotesDokumen10 halamanNotesKishore KishuBelum ada peringkat

- 4.6 Direct Memory Access (DMA)Dokumen6 halaman4.6 Direct Memory Access (DMA)lakshmiraniBelum ada peringkat

- 8237 Dma ControllerDokumen14 halaman8237 Dma ControllerSAIF ULLAH100% (1)

- Direct Memory AccessDokumen19 halamanDirect Memory Accessayan deyBelum ada peringkat

- Direct Memory Access: Direct Memory Access (DMA) Is A Process in Which An External Device TakesDokumen21 halamanDirect Memory Access: Direct Memory Access (DMA) Is A Process in Which An External Device TakesLeonardo Cavero FarfánBelum ada peringkat

- Modes of Transfer DMADokumen9 halamanModes of Transfer DMAAditya SharmaBelum ada peringkat

- Ee 309 M1Dokumen7 halamanEe 309 M1Basheer V.PBelum ada peringkat

- 8259A Programmable Interrupt ControllerDokumen18 halaman8259A Programmable Interrupt ControllerBasheer V.PBelum ada peringkat

- Unit Ii Hardware Interfacing With Intel 8085Dokumen44 halamanUnit Ii Hardware Interfacing With Intel 8085Basheer V.PBelum ada peringkat

- Features of 8051Dokumen21 halamanFeatures of 8051Basheer V.PBelum ada peringkat

- What Does It Do An Infant Incubator Is Used Mainly To Keep A Baby's Core Temperature Stable at 37 Degrees PhysiologyDokumen1 halamanWhat Does It Do An Infant Incubator Is Used Mainly To Keep A Baby's Core Temperature Stable at 37 Degrees PhysiologyBasheer V.PBelum ada peringkat

- Adder Sub AluDokumen22 halamanAdder Sub AluBasheer V.PBelum ada peringkat

- Combinational Logic Design&AnalysisDokumen34 halamanCombinational Logic Design&AnalysisBasheer V.PBelum ada peringkat

- EncoderDokumen15 halamanEncoderBasheer V.PBelum ada peringkat

- DecoderDokumen17 halamanDecoderBasheer V.P100% (1)

- Chapter 3 - Combinational Logic DesignDokumen32 halamanChapter 3 - Combinational Logic DesignBasheer V.PBelum ada peringkat

- Vlsi Design: Mos TransistorDokumen162 halamanVlsi Design: Mos TransistorBasheer V.PBelum ada peringkat

- Vlsi Design: Mos TransistorDokumen162 halamanVlsi Design: Mos TransistorBasheer V.PBelum ada peringkat

- DiblDokumen25 halamanDiblBasheer V.PBelum ada peringkat

- DSDDokumen56 halamanDSDBasheer V.PBelum ada peringkat

- SIGTRAN DescriptionDokumen108 halamanSIGTRAN Descriptiondion132Belum ada peringkat

- Casa ModelDokumen1 halamanCasa ModelJosé A Leon VasquezBelum ada peringkat

- Data Communications Summary Forouzan PDFDokumen27 halamanData Communications Summary Forouzan PDFerwin rosumanBelum ada peringkat

- SYS 500 Installation: 1MRS751254-MENDokumen132 halamanSYS 500 Installation: 1MRS751254-MENmihirandesilvaBelum ada peringkat

- Tutorial1 AnswersDokumen8 halamanTutorial1 AnswersvinoBelum ada peringkat

- Lec 8 - Network CardsDokumen16 halamanLec 8 - Network CardsAbhikalpThakurBelum ada peringkat

- E350M1USB3 multiQIGDokumen144 halamanE350M1USB3 multiQIGfoca529Belum ada peringkat

- With The Block Diagram Explain Basic Elements of DSPDokumen4 halamanWith The Block Diagram Explain Basic Elements of DSPAnil Shrestha100% (3)

- LCD TV: User ManualDokumen69 halamanLCD TV: User ManualMario Rosas VargasBelum ada peringkat

- DEH-P3590MP - Operational ManualDokumen89 halamanDEH-P3590MP - Operational ManualIon CioriciBelum ada peringkat

- Cdex Exact Audio Copy (Eac) Cdex: CD Ripping / Encoding GuideDokumen3 halamanCdex Exact Audio Copy (Eac) Cdex: CD Ripping / Encoding GuideabhijitchBelum ada peringkat

- DSS Installation Configuration and Bussiness Use Guide V1.0Dokumen91 halamanDSS Installation Configuration and Bussiness Use Guide V1.0castnhBelum ada peringkat

- Intermec 5250 TE2000 Programmers GuideDokumen278 halamanIntermec 5250 TE2000 Programmers GuidedjkibBelum ada peringkat

- HP ProBook 640 G1 Notebook PC - Identifying Components PDFDokumen10 halamanHP ProBook 640 G1 Notebook PC - Identifying Components PDFsuper_facaBelum ada peringkat

- Graphics and Image Data RepresentationsDokumen46 halamanGraphics and Image Data RepresentationsbobbbuilderBelum ada peringkat

- C Users Aishu Desktop Sss - XpsDokumen37 halamanC Users Aishu Desktop Sss - XpsShivaraman ShankarBelum ada peringkat

- BR Wave Converter Manual Win EDokumen6 halamanBR Wave Converter Manual Win ESylvain GagneBelum ada peringkat

- EE480 Week 1Dokumen43 halamanEE480 Week 1M Usman RiazBelum ada peringkat

- EVOLUTION OF MEDIA v1Dokumen20 halamanEVOLUTION OF MEDIA v1Mica Angela CestinaBelum ada peringkat

- Mobile Commerce and Ubiquitous Computing: E-BusinessDokumen43 halamanMobile Commerce and Ubiquitous Computing: E-BusinessGul Rahim khanBelum ada peringkat

- CBLM Module NetworkingDokumen10 halamanCBLM Module NetworkingSAMMY PALAGANASBelum ada peringkat

- LG 440 SM ComponentDokumen39 halamanLG 440 SM ComponentMalvinBelum ada peringkat

- Created by Image To PDF Trial Version, To Remove This Mark, Please Register This SoftwareDokumen37 halamanCreated by Image To PDF Trial Version, To Remove This Mark, Please Register This SoftwareShantanu SinghBelum ada peringkat

- T1, T1c, T2, T3, T4 LinesDokumen4 halamanT1, T1c, T2, T3, T4 LinesdhawanrishBelum ada peringkat

- 9 Line Coding and ISIDokumen17 halaman9 Line Coding and ISIHarshil AmbagadeBelum ada peringkat

- Descargar Gratis El Libro La Rebelion de Las RatasDokumen3 halamanDescargar Gratis El Libro La Rebelion de Las RatasDiego Alejandro Montoya RamirezBelum ada peringkat

- Computer DefinitionDokumen5 halamanComputer DefinitionPastidyuso C. NinzBelum ada peringkat

- Laserjet Pro m101-m106 m129 m134 Troubleshooting Manual PDFDokumen262 halamanLaserjet Pro m101-m106 m129 m134 Troubleshooting Manual PDFnelque402Belum ada peringkat

- Marantz Complete Catalogue 2015/16Dokumen31 halamanMarantz Complete Catalogue 2015/16Klementina MlakarBelum ada peringkat