Scan and JTAG Principles: Advanced RISC Machines

Diunggah oleh

mivaepaoDeskripsi Asli:

Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Scan and JTAG Principles: Advanced RISC Machines

Diunggah oleh

mivaepaoHak Cipta:

Format Tersedia

ARM

Advanced RISC Machines

Scan and JTAG Principles

Scan and JTAG Principles 1

Module Contents

* Scan Fundamentals

• Full and partial scan techniques

• Level sensitive and edge triggered methods

* JTAG and the Test Access Port (TAP)

• JTAG Interface Signals

• Test Access Port Controller

• Test Access Port Instructions

Scan and JTAG Principles 2

Scan Basics

* Flip-flop elements within a circuit can be connected serially to

form a shift register structure.

* Access to the scan chain data via 2 pins, Test Data In (TDI) and

Test Data Out (TDO).

* Data can be applied serially on TDI to set up the system state,

while state data can be read serially on TDO.

Scan and JTAG Principles 3

Level Sensitive Scan Design

* 2 basic design principles:

• Master-slave gated flip-flops form the basic scan element.

• Each register can be converted to form a serial shift register

* Advantages:

• Hazard Free

* Disadvantages

• Complexity (Size - speed).

Scan and JTAG Principles 4

Serial Scan

* Uses edge triggered latches to form the scan element.

* Lower complexity; higher speed.

* Sensitive to clock skew.

* May need synchronisation (redundant) opposite edge triggered

scan elements to rectify.

Scan and JTAG Principles 5

ARM Scan Cell

Shift/Load G1

1 1D To next

From last 1

cell

cell C1

1D

C1

G1

From logic 1 To logic

or pin 1 or pin

Clock Update Mode

Scan and JTAG Principles 6

Scan Nomenclature

* Full Scan

• Connection of all flip-flop elements into a single serial shift

register.

* Partial Scan

• Connection of a subset of all flip-flop elements to form a serial

shift register.

• There can be more than one partial scan chain.

* Boundary Scan

• All I/Os are isolated from the core logic by a serial shift register.

• This shift register can be used to apply system-level stimuli to the

core serially.

Scan and JTAG Principles 7

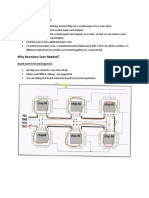

System Level Test

* Increasing board complxities and use of multichip modules has

stretched traditional system test techniques.

* Joint Test Action Group (JTAG) to formulate a unified scan-based

system test method.

* Result was the IEEE 1149 Boundary Scan architecture.

Scan and JTAG Principles 8

JTAG System Test

TAP TAP

Control Control

TAP

TDI

TCK

TMS

TRST

TDO

Scan and JTAG Principles 9

Extra JTAG Logic

Boundary-Scan

Cell Test Registers

and Decoder

TAP

Controller

TAP

Control

Package Pin Test Access Port

(TAP)

Test Access Port

(TAP)

Scan and JTAG Principles 10

TAP Pin Descriptions I

* Test Clock Input (TCK)

• Independent of the system clock.

• Rising edge used to load signals applied at the TAP input pins

(TDI,TMS).

• Falling edge used to clock data out of the TAP data output (TDO).

* Test Mode Select (TMS)

• Test logic operation determined by input sequence on this pin.

• In undriven state, TMS should be a logic 1.

* Test Data Input (TDI)

• Serial test data applied at this input.

• Again, should be pulled up to logic 1when undriven.

Scan and JTAG Principles 11

TAP Pin Descriptions II

* Test Data Output (TDO)

• Serial data out.

• When there is no shift activity, TDO is set to a high-impedence

state.

* Test Reset (TRST)

• TAP controller can be initialised via TCK and TMS.

• Optional TRST pin allows reset independently of TCK and TMS.

• Pulling TRST to 0 asynchronously forces the test logic into its

reset state.

Scan and JTAG Principles 12

TAP Architecture

Test Data Registers

Device ID Register

Bypass register

Instruction Decode

TDO

TDI Instruction Reg.

TMS TAP

Controller

TCK

nTDOEN

nTRST

Scan and JTAG Principles 13

TAP Control State Machine

Test-Logic

Reset

TMS=1 TMS=0

TMS=1 TMS=1 TMS=1

Run-Test/Idle Select-DR-Scan Select-IR-Scan

TMS=0 TMS=0 TMS=0

TMS=1 TMS=1

Capture-DR Capture-IR

TMS=0 TMS=0

TMS=0 TMS=0

Shift-DR Shift-IR

TMS=0 TMS=1

TMS=1 TMS=1

Exit1-DR Exit1-IR

TMS=0 TMS=0

TMS=0

Pause-DR TMS=0 Pause-IR

TMS=1 TMS=1

TMS=0 TMS=0

Exit2-DR Exit2-IR

TMS=1 TMS=1

Update-DR Update-IR

TMS=1 TMS=0 TMS=1

TMS=0

Scan and JTAG Principles 14

Controller States I

* TEST-LOGIC-RESET

• Test logic disabled; allows for normal chip operation.

* RUN-TEST-IDLE

• Controller state between scan operations.

* SELECT-DR/IR-SCAN

• Temporary controller states in which all test data registers selected

by the current instruction retain their current state.

• Initiates register scan sequence.

* CAPTURE-DR

• The selected test data register captures its data inputs on the rising

edge of TCK.

Scan and JTAG Principles 15

Controller States II

* CAPTURE-IR

• The instruction register loads a fixed bit pattern on rising TCK.

* SHIFT-DR/IR

• In these states the test data register (DR) or the instruction register

(IR), shifts its data by one stage on each rising edge of TCK.

* EXIT1-DR/IR

• These are temporary controller states. If TMS = 1, then on the

next rising TCK, the state machine will enter the Update-DR/IR

states.

* UPDATE-DR

• Some test data registers have latched parallel outputs.

• These outputs are latched on falling TCK

Scan and JTAG Principles 16

Controller States III

* UPDATE-IR

• On TCK falling the instruction shifted in during SHIFT-IR is

latched into the instruction register.

* PAUSE-DR/IR

• These states allow for the instruction/data shift operations to be

halted temporarily.

* EXIT2-DR/IR

• Temporary controller states allowing either resumption of or

termination of the current scan instruction.

Scan and JTAG Principles 17

TAP Instructions I

* SCAN_N (0010)

• Connects the Scan Path Select Register between TDI and TDO.

• Selects scan chain for subsequent test operations.

* EXTEST (0000)

• Allows for testing of external logic.

• During SHIFT-DR scanned-in data is applied immediately to the

system.

* INTEST (1100)

• Allows for testing of internal logic.

Scan and JTAG Principles 18

TAP Instructions II

* IDCODE (1110)

• Connects device identification register between TDI and TDO.

* BYPASS (1111)

• Connects a single stage shift register between TDI and TDO.

• Allows testing of individual devices to take place.

* CLAMP (0101)

• Connects a single stage shift register between TDI and TDO.

• Output signals are defined by values previously loaded into the

currently selected scan chain.

Scan and JTAG Principles 19

TAP Instructions III

* HIGHZ (0111)

• Connects a single stage shift register between TDI and TDO.

• All outputs are forced to high impedence state.

* CLAMPZ (1001) NB. ARM-SPECIFIC

• Connects a single stage shift register between TDI and TDO.

• All tri-state outputs are inactive, but data supplied to outputs is

derived from the scan cells.

* SAMPLE/PRELOAD (0011)

• Selects the boundary scan register as DR, and samples or preloads

the chip I/Os.

Scan and JTAG Principles 20

ARM Implementation Details

* ARM7 family cores have *no* boundary scan.

* SAMPLE/PRELOAD instructions must not be used.

* 3 Scan chains are available as test data registers.

* JTAG inputs (TDI andTMS) have no internal pullups and must be

driven correctly at all times.

Scan and JTAG Principles 21

Summary

* Serial test methods offer a route towards an automated method of

providing test coverage.

* IEEE 1149 extends this serial test architecture to cover system

level testing.

* ARM implements key components of the 1149 standard within its

debug-aware cores, but requires external support to completely

adhere to the standard.

Scan and JTAG Principles 22

Anda mungkin juga menyukai

- Practical Digital Electronics for TechniciansDari EverandPractical Digital Electronics for TechniciansPenilaian: 3 dari 5 bintang3/5 (1)

- Practical Data Acquisition for Instrumentation and Control SystemsDari EverandPractical Data Acquisition for Instrumentation and Control SystemsBelum ada peringkat

- JTAG Principles and InterfaceDokumen27 halamanJTAG Principles and InterfaceMotamarri AravindBelum ada peringkat

- Jtag 2 PDFDokumen21 halamanJtag 2 PDFravisguptajiBelum ada peringkat

- An Introduction To JTAG Boundary Scan From Sun MicroelectronicsDokumen10 halamanAn Introduction To JTAG Boundary Scan From Sun MicroelectronicsJoemill Veloso FlordelisBelum ada peringkat

- Vinay Sharma: Director, Ni2designsDokumen6 halamanVinay Sharma: Director, Ni2designspranithpreethBelum ada peringkat

- IEEE 1149.1 Test Access PortDokumen17 halamanIEEE 1149.1 Test Access PortChinmay100% (1)

- Jtag PresentationDokumen21 halamanJtag PresentationNivaz ChockkalingamBelum ada peringkat

- Jtag System: With Openocd ExplanationDokumen17 halamanJtag System: With Openocd ExplanationMohammed Publications100% (1)

- 5 JtagDokumen64 halaman5 Jtagsharad2208Belum ada peringkat

- JTAG TAP ControllerDokumen5 halamanJTAG TAP ControllerTanmayKabra100% (1)

- Boundary Scan: Joint Test Action Group (Jtag)Dokumen10 halamanBoundary Scan: Joint Test Action Group (Jtag)anuBelum ada peringkat

- Target Hardware Debugging Boundary ScanDokumen13 halamanTarget Hardware Debugging Boundary ScanLakshika LakshBelum ada peringkat

- IEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III DevicesDokumen22 halamanIEEE 1149.1 (JTAG) Boundary-Scan Testing in Stratix III DevicesYadav RaviBelum ada peringkat

- What Is JTAG and How Can I Make Use of ItDokumen4 halamanWhat Is JTAG and How Can I Make Use of ItThein Htoon lwinBelum ada peringkat

- (IEEE 1149.1/P1149.4) : Tutorial IntermediateDokumen57 halaman(IEEE 1149.1/P1149.4) : Tutorial Intermediatesenthilkumar100% (1)

- Boundary Scan TesterDokumen5 halamanBoundary Scan Testerrohitsingh2909Belum ada peringkat

- JTAG MaterialDokumen2 halamanJTAG Materialchinnureddyseelam07100% (1)

- 1 Introduction To Boundary-ScanDokumen60 halaman1 Introduction To Boundary-ScanHassine OueslatiBelum ada peringkat

- Tap ControllerDokumen16 halamanTap ControllerMoin PashaBelum ada peringkat

- Design of Ieee 1149.1 Tap Controller Ip CoreDokumen12 halamanDesign of Ieee 1149.1 Tap Controller Ip CoreCS & ITBelum ada peringkat

- BS PDFDokumen31 halamanBS PDFRohith RajBelum ada peringkat

- IEEE 1149.1 (JTAG) Boundary-Scan Testing For Cyclone II DevicesDokumen20 halamanIEEE 1149.1 (JTAG) Boundary-Scan Testing For Cyclone II DevicesKesavaram ChallapalliBelum ada peringkat

- Why Boundary Scan Needed?Dokumen39 halamanWhy Boundary Scan Needed?srikanth100% (1)

- Scan Insertion - Week2&3Dokumen48 halamanScan Insertion - Week2&3VENKATRAMAN100% (1)

- ATPG Methodology FlowDokumen37 halamanATPG Methodology FlowaanbalanBelum ada peringkat

- Boundary Scan, JTAG, IEEE 1149.1 TutorialDokumen6 halamanBoundary Scan, JTAG, IEEE 1149.1 Tutorialmelvin45Belum ada peringkat

- Boundary Scan ArchitectureDokumen6 halamanBoundary Scan ArchitectureHARISH DAMARLABelum ada peringkat

- DFTDokumen23 halamanDFTChaitanya VarmaBelum ada peringkat

- 1149.1 JTAG Boundary Scan Standard: System View of Boundary Scan Hardware Elementary Scan CellDokumen20 halaman1149.1 JTAG Boundary Scan Standard: System View of Boundary Scan Hardware Elementary Scan CellNikhil Chauhan100% (1)

- AS 1149.1 Nov'10Dokumen42 halamanAS 1149.1 Nov'10JYOTI PRAKASHBelum ada peringkat

- Jtag PDFDokumen22 halamanJtag PDFamitwangoo0% (1)

- Scan PDFDokumen49 halamanScan PDFferoz100% (1)

- 4 JtagDokumen10 halaman4 JtagJai Kiran RBelum ada peringkat

- Boundary ScanDokumen12 halamanBoundary ScanMukul TanwarBelum ada peringkat

- ATPG Methodology FlowDokumen37 halamanATPG Methodology FlowAdhi SuruliBelum ada peringkat

- Boundary ScanDokumen8 halamanBoundary Scanmechbull11Belum ada peringkat

- Jtag - AN IEEE 1149.1 STDDokumen42 halamanJtag - AN IEEE 1149.1 STDkanchanstiwariBelum ada peringkat

- Jtag 1Dokumen12 halamanJtag 1lavanyaBelum ada peringkat

- Agenda: - Test StrategyDokumen87 halamanAgenda: - Test Strategypravallika vysyarajuBelum ada peringkat

- Pulsatrix ADTS PaperDokumen5 halamanPulsatrix ADTS PaperVince AlturaBelum ada peringkat

- Boundary ScanDokumen61 halamanBoundary ScanGéza HorváthBelum ada peringkat

- 02 - Principles of Boundary ScanDokumen27 halaman02 - Principles of Boundary ScanPaulo HermidaBelum ada peringkat

- Boundary Scan LogicDokumen26 halamanBoundary Scan LogicAkshay Kumar MBelum ada peringkat

- Debugging With JTAGDokumen43 halamanDebugging With JTAGGlen MonetteBelum ada peringkat

- Testing and Boundary Scan: Roth Text: Chapter 10.1 - 10.4Dokumen25 halamanTesting and Boundary Scan: Roth Text: Chapter 10.1 - 10.4JosephBelum ada peringkat

- Boundary Scan: - Developed To Test Interconnect Between Chips On PCBDokumen8 halamanBoundary Scan: - Developed To Test Interconnect Between Chips On PCBVeeranjaneyulu DhikondaBelum ada peringkat

- 8 JTAG Unit 8Dokumen19 halaman8 JTAG Unit 8nareshBelum ada peringkat

- Rpi JtagDokumen5 halamanRpi JtagLa Abeja Sana BoBelum ada peringkat

- 5 - ES - 8051 MC - ArchitectureDokumen89 halaman5 - ES - 8051 MC - ArchitectureSaket GoluBelum ada peringkat

- CDC 3272G ARM7-Based Car Dashboard ControllerDokumen2 halamanCDC 3272G ARM7-Based Car Dashboard ControlleranonbeatBelum ada peringkat

- JTAG and Multi - ICEDokumen20 halamanJTAG and Multi - ICEjcyBelum ada peringkat

- DEFCON 21 Grand JTAGulator PDFDokumen62 halamanDEFCON 21 Grand JTAGulator PDFhisohisoBelum ada peringkat

- JTAGDokumen12 halamanJTAGShiva KumarBelum ada peringkat

- 3F9488 Datasheet PDFDokumen251 halaman3F9488 Datasheet PDFsunder punjabiBelum ada peringkat

- Programming On-Chip Flash Memories of 56F80X Devices Using The Jtag/Once InterfaceDokumen20 halamanProgramming On-Chip Flash Memories of 56F80X Devices Using The Jtag/Once InterfaceTaiwoBelum ada peringkat

- JTAG TutorialDokumen8 halamanJTAG TutorialVinay KrBelum ada peringkat

- Transistor Electronics: Use of Semiconductor Components in Switching OperationsDari EverandTransistor Electronics: Use of Semiconductor Components in Switching OperationsPenilaian: 1 dari 5 bintang1/5 (1)

- 8051 Microcontroller: An Applications Based IntroductionDari Everand8051 Microcontroller: An Applications Based IntroductionPenilaian: 5 dari 5 bintang5/5 (6)

- Trimble Gps in STDokumen65 halamanTrimble Gps in STMohamedAlAmineBelum ada peringkat

- Tehman Alam Siddiqui CVDokumen2 halamanTehman Alam Siddiqui CVMuhammad Haris BaigBelum ada peringkat

- Fabless Semiconductor ImplementationDokumen358 halamanFabless Semiconductor ImplementationPaulo Carvalho100% (3)

- 1 - Angle ModulationDokumen34 halaman1 - Angle ModulationNilegn Vllgn100% (1)

- Tac07csk (1) UnlockedDokumen43 halamanTac07csk (1) UnlockedJuan AlbertoBelum ada peringkat

- Indicating InstrumentsDokumen26 halamanIndicating InstrumentsSweetMaina100% (1)

- Information Technology Past Paper June 2006Dokumen9 halamanInformation Technology Past Paper June 2006Dudley Clarke75% (4)

- MOS MemoryDokumen53 halamanMOS Memoryskh_1987100% (1)

- File FormatsDokumen24 halamanFile Formatssravan100% (1)

- MT 4100 March 2013Dokumen2 halamanMT 4100 March 2013Dario Gabriel Coz RojasBelum ada peringkat

- User Manual PB EnglishDokumen108 halamanUser Manual PB EnglishFonchy CastroBelum ada peringkat

- Usage: Universal Programmable Poe Injector (P/N I0Atpi24)Dokumen4 halamanUsage: Universal Programmable Poe Injector (P/N I0Atpi24)jimpomaBelum ada peringkat

- Music With Matlab PDFDokumen2 halamanMusic With Matlab PDFali aminBelum ada peringkat

- Power: Circuit Diagrams and PWB LayoutsDokumen4 halamanPower: Circuit Diagrams and PWB LayoutsAmin SantanaBelum ada peringkat

- Bobisoft Winding Design Software PDFDokumen17 halamanBobisoft Winding Design Software PDFxxBelum ada peringkat

- Lec10 PDFDokumen29 halamanLec10 PDFNaresh BirudalaBelum ada peringkat

- SOLLATEK Kenya Pricelist 01 07 2014Dokumen17 halamanSOLLATEK Kenya Pricelist 01 07 2014Washington Anjichi Okang'a0% (1)

- 1Dokumen784 halaman1Prasanth Bitla100% (1)

- Screen-Printed, Flexible, Parasitic Beam-Switching Millimeter-Wave Antenna Array For Wearable ApplicationsDokumen9 halamanScreen-Printed, Flexible, Parasitic Beam-Switching Millimeter-Wave Antenna Array For Wearable Applicationsantonio ScacchiBelum ada peringkat

- LGP4247H-12LPB Eay62512701Dokumen75 halamanLGP4247H-12LPB Eay62512701Роман КирильчукBelum ada peringkat

- TT2190LS: Color TV Horizontal Deflection Output ApplicationsDokumen4 halamanTT2190LS: Color TV Horizontal Deflection Output ApplicationsFreddyBelum ada peringkat

- Annual Report 2012: ERTMS/GSM-R & Panel of Telecom ExpertsDokumen65 halamanAnnual Report 2012: ERTMS/GSM-R & Panel of Telecom ExpertsMoyGar2014100% (1)

- TransformersDokumen11 halamanTransformersHimanshu KhandelwalBelum ada peringkat

- Effect of Temperature On ResistanceDokumen3 halamanEffect of Temperature On ResistanceKiran KarthikBelum ada peringkat

- PN-Junction Diode Characteristics: Forward BiasDokumen17 halamanPN-Junction Diode Characteristics: Forward BiasyasaslitBelum ada peringkat

- CS QuestionsDokumen2 halamanCS QuestionsKarthik MambersBelum ada peringkat

- UoN SyllabusDokumen40 halamanUoN SyllabusSam AngBelum ada peringkat

- Monitoring-Times Magazine Aug 1996Dokumen116 halamanMonitoring-Times Magazine Aug 1996Benjamin DoverBelum ada peringkat

- Sensory QuestionnaireDokumen11 halamanSensory QuestionnaireElisa DellaBelum ada peringkat