Asdasdasdasd

Asdasdasdasd

Diunggah oleh

Restyan Adi WirawanJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Asdasdasdasd

Asdasdasdasd

Diunggah oleh

Restyan Adi WirawanHak Cipta:

Format Tersedia

HALF ADDER, FULL ADDER & FULL SUBSTRACTOR Gerbang logika atau sering juga disebut gerbang logika

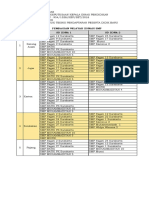

Boolean merupakan sebuah sistem pemrosesan dasar yang dapat memproses input-input yang berupa bilangan biner menjadi sebuah output yang berkondisi yang akhirnya digunakan untuk proses selanjutnya. Gerbang logika dapat mengkondisikan input-input yang masuk kemudian menjadikannya sebuah output yang sesuai dengan apa yang ditentukan olehnya. Terdapat tiga gerbang logika dasar, yaitu : gerbang AND, gerbang OR, gerbang NOT. Ketiga gerbang ini menghasilkan empat gerbang berikutnya, yaitu : gerbang NAND, gerbang NOR, gerbang XNOR. Tabel 1. Tabel Kebenaran Gerbang Logika.

Rangkaian aritmatika dasar termasuk ke dalam rangkaian kombinasional yaitu suatu rangkaian yang output-nya tidak tergantung pada kondisi output sebelumnya, hanya tergantung pada present state dari input. A. Half Adder (Penjumlahan Paruh) dan Full Adder (Penjumlahan Penuh) Sebuah rangkaian kombinasional yang melaksanakan penjumlahan 2 digit biner disebut dengan half adder, sedangkan rangkaian yang melaksanakan penjumlahan 3 bit disebut full adder. Penjumlah atau Adder adalah komponen elektronika digital yang dipakai untuk menjumlahkan dua buah angka dalam sistem bilangan biner. Rangkaian full

adder dapat tersusun dari dua buah half adder. Di pasaran rangkaian full adder sudah ada yang berbentuk IC, seperti 74LS83 (4-bit full adder). Dalam komputer dan mikroprosesor, Adder biasanya berada di bagian ALU (Arithmetic & Logic Unit). Sistem bilangan yang dipakai dalam proses penjumlahan, selain bilangan biner, juga bilangan BCD (binary-coded decimal).

Gambar 1. Blok Diagram Rangkaian Half-Adder Pembicaraan mengenai Adder biasanya dimulai dari Half-Adder, kemudian Full-Adder, dan yang ketiga adalah Ripple-Carry-Adder. Pada Half-Adder, berdasarkan dua input A dan B, maka output Sum, S dari Adder ini akan dihitung berdasarkan operasi XOR dari A dan B. Selain output S, ada satu output yang lain yang dikenal sebagai C atau Carry, dan C ini dihitung berdasarkan operasi AND dari A dan B. Pada prinsipnya output S menyatakan penjumlahan bilangan pada input A dan B, sedangkan output C menyatakan MSB (most significant bit atau carry bit) dari hasil jumlah itu.

Tabel logika/kebenaran dari Half-Adder akan mengikuti seperti berikut: Input Output A B C 0 0 0 1 1 0 1 1 0 0 0 1 S 0 1 1 0

Half Adder (Penjumlahan Paruh)

Gambar 2. Diagram blok Full-Adder Rangkaian Full-Adder, pada prinsipnya bekerja seperti Half-Adder, tetapi mampu menampung bilangan Carry dari hasil penjumlahan sebelumnya. Jadi jumlah inputnya ada 3: A, B dan Ci, sementara bagian output ada 2 yaitu S dan Co. Ci ini dipakai untuk menampung bit Carry dari penjumlahan sebelumnya.

Gambar 3. Blok Diagram sirkuit Full-Adder

Input Output A B Ci Co S 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 0 1 0 1 1 1 0 1 1 0 1 0 0 1

Rangkaian dari n buah Full-Adder bisa dipakai untuk menjumlahkan n bit bilangan biner. Maka dalam hal ini, kita akan memperoleh rangkaian yang disebut RippleCarry-Adder.

Gambar 4. Diagram sirkuit untuk ripple carry adder 4-bit B. Half Substractor (Pengurangan Paruh) dan Full Substractor(Pengurangan Penuh) Substractor (Pengurangan)

Rangkaian half substractor hampir sama dengan rangkaian half adder. D (Difference) ekivalen dengan S (sum), dan B (borrow) ekivalen dengan C (carry) pada half adder. Kedua rangkaian ini melakukan operasi pengurangan biner. Half substractor untuk pengurangan satu bit biner, sedangkan full substractor untuk pengurangan lebih dari satu bit biner. Subtractor atau pengurang adalah rangkaian elektronika digital yang dipakai untuk melakukan operasi pengurangan dari dua buah bilangan biner. Proses operasi pengurangan ini menggunakan prinsip dasar yang sama dengan rangkaian Adder (rangkaian penjumlah). Jika dua buah angka: Xi dan Yi, dikurangkan satu sama lain membentuk Xi Yi, maka akan kita perolah dua buah hasil di bagian outputnya: bit Beda (Difference) Di dan bit Pinjaman (Borrow) Bi + 1. Jika kita juga mengikutkan bit pinjaman, Bi dari bagian MSB (Most Significant Bit), operasi pengurangan yang lengkap adalah BiXi Yi. Operasi untuk mendapatkan dua bit output akan mengikuti proses seperti di bawah ini:

Bi + 1 = K-map Bi(1,2,3,7)

Soal Latihan :

Tabel Perlakuan Input Output A B Bout D 0 0 0 0 0 1 -1 1 1 0 0 1 1 1 0 0

Nb: Ci = 0

Anda mungkin juga menyukai

- Soal Uts Pemrograman Jaringan - d3tkDokumen1 halamanSoal Uts Pemrograman Jaringan - d3tksolobreak05Belum ada peringkat

- Topologi JaringanDokumen25 halamanTopologi Jaringansolobreak05Belum ada peringkat

- Seikat Serat OptikDokumen6 halamanSeikat Serat Optiksolobreak05Belum ada peringkat

- Hasil Final Zonasi SMPDokumen14 halamanHasil Final Zonasi SMPsolobreak05Belum ada peringkat

- Pemrograman Dengan Algoritma Greedy Arduino Atmega328 PDFDokumen31 halamanPemrograman Dengan Algoritma Greedy Arduino Atmega328 PDFsolobreak05Belum ada peringkat

- Presensi So 2Dokumen2 halamanPresensi So 2solobreak05Belum ada peringkat

- Makalah Kukuh GelarDokumen72 halamanMakalah Kukuh Gelarsolobreak05Belum ada peringkat