Proposal Proyek Perancangan Sistem Elektronis

Diunggah oleh

Muslim MunawarHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Proposal Proyek Perancangan Sistem Elektronis

Diunggah oleh

Muslim MunawarHak Cipta:

Format Tersedia

Proposal Proyek Perancangan Sistem Elektronis Simulasi Filter Butterworth menggunakan ModelSim

1. Latar Belakang Perancangan Kelompok kami memilih judul ini karena cukup unik karena butteworth sendiri merupakan sebuah rangkaian tapis yang berfungsi menapis frekuensi tertentu, unik disini karena kami akan mencoba menganalisis sebisa kami bagaimana filter butterworth ini di analisis menggunakan modelsim. Yang setahu kami yang namanya filter akan meloloskan pita frekuensi tertentu sesuai rangkaian yang ada. Mulanya kami membayngkan dengan simulasi ini akan dilakukan inputan besar frekuensi berapa dan akan ditapis bagaimana, dan itu yang ingin kami buktikan disini. Dan kami juga merasa tertantang karena kami memang benar benar belum menguasai apa itu filter butterworth (yang ada di perkuliahan Pengolahan Sinyal Digital) serta karakteristiknya, sehingga ekspektasinya kami bias lebih belajar lebih banyak lagi. 2. Tujuan Tujan kami melakukan perancangan ini adalah :

2.A sebagai salah satu persyaratan kurikulum pada matakuliah Perancangan Sistem Elektronis 2.B Menganalisis tapis butterworth menggunakan modelsim 2.C Menganalisis parameter yang ada pada butterworth

3. Pembahasan Umum Teknik desain filter digital IIR didasarkan pada transformasi bilinear dari prototipe fungsi transfer analog. Fungsi transfer analog biasanya salah satu dari tipe fungsi transfer: Butterworth, Chebyshev Tipe 1, Chebyshev Tipe 2 dan Elliptic (atau Cauer). Perbedaan antara tipe-tipe filter tersebut dapat dijelaskan dengan melihat filter lolos bawah (lowpass) analog seperti dibawah ini [Antoniou, 1993]. a. Fungsi transfer lolos bawah Butterworth mempunyai tanggap magnitude mendatar maksimum dan tanggap magnitude berkurang secara mendatar dengan frekuensi bertambah. b. Fungsi transfer lolos bawah Chebyshev Tipe 1 mempunyai tanggap magnitude dengan riak setimbang pada pita lolos dan tanggap magnitude berkurang secara mendatar dengan frekuensi bertambah di sebelah luar pita lolos. c. Fungsi transfer lolos bawah Chebyshev

Tipe 2 mempunyai tanggap magnitude berkurang secara mendatar pada pita lolos dengan frekuensi bertambah dan tanggap magnitude riak setimbang pada pita cegah. d. Fungsi transfer lolos bawah Elliptic mempunyai tanggap magnitude riak setimbang pada kedua pita, pita lolos maupun pita cegah.

Dari gambar tersebut perancangan akan mempunyai parameter komponen sebagai berikut : Komponen D Filp Flop (DFF) sebanyak 8 unit. Komponen Multiplier sebanyak 7 unit. Komponen Adder sebanyak 6 unit.

3. METODE PENELITIAN Langkah simulasi rancangan rangkaian filter sebagai berikut : a. Menyusun program menggunakan Matlab. Program Matlab yang disusun, didasarkan pada penetapan rancangan rangkaian filter menggunakan butterworth orde 2 berjenis band pass filter. Filter ditetapkan dapat melewatkan rentang frekuensi pada frekuensi cutoff bawah sebesar 50 Hz dan frekuensi cutoff atas sebesar 3000 Hz. Frekuensi sampling yang digunakan pada penelitian ini sebesar 44100 Hz. Berikut ini program Matlab dari fungsi pemfilteran :

%Pemfilteran : Band Pass Filter w1 = 50*2/fs; w2 = 3000*2/fs; [b,a]=butter(2,[f1 f2]); s = [filter(b,a,y)];

Hasil dari program tersebut diperoleh nilai koefisien filter yaitu Numerator (b) and Denominator (a) yang besarnya sebagai berikut :

b = 0.034 0 -0.067 0 0.034 a = 1 -3.41 4.31 -2.52 0.55

b. Membuat skematik rangkaian filter butterworth. Berdasarkan hasil keluaran koefisien pada program Matlab, selanjutnya dirancang skematik rangkaian filter

c. Membuat program menggunakan ModelSim Komponenkomponen yang diperlukan untuk menyusun rangkaian seperti terlihat gambar 2 terdiri atas : a. Komponen D Filp Flop (DFF) sebanyak 8 unit. Setiap komponen DFF ditulis dengan program :

-- Delay 16 BIT Unit Use D FlipFlop(2)--DFF2 ------------------------------------library ieee;

use ieee.std_logic_1164.all; ENTITY dff2 IS PORT( D : IN STD_LOGIC_VECTOR(15 downto 0); Clk, Res : IN STD_LOGIC; Q : OUT STD_LOGIC_VECTOR(15 downto 0)); END dff2; ARCHITECTURE behavioral OF dff2 IS BEGIN PROCESS(Clk, Res) --We only care about Clk BEGIN IF Res = '1' THEn Q <= X"0000"; -- determine Q=0 Hexa Else IF (Clk'event) AND (Clk='1') THEN --Positive Edge Q <= D; END IF; END IF; END PROCESS; END behavioral;

Pada komponen D ini lebih kepada delay terhadap D yang diberikan hal ini dapat terlihat dari source code yang ada yaitu IF Res = '1' THEn Q <= X"0000"; -- determine Q=0 Hexa Else IF (Clk'event) AND (Clk='1') THEN --Positive Edge Q <= D; Dari situ bahwa reset berlogika aktif (1) maka Q akan bernilai 0000 apapun nilai clocknya, lalu saat clock event dan clok bernilai 1 maka Q akan bernilai D.

b. Komponen Multiplier sebanyak 7 unit. Setiap komponen Multiplier ditulis dengan program :

-- MULTIPLIER 32 BIT -------------------------------LIBRARY ieee; USE ieee.std_logic_1164.ALL; USE ieee.std_logic_arith.ALL; USE ieee.std_logic_signed.ALL;

USE ieee.std_logic_unsigned.ALL; ENTITY signed_mult IS PORT ( a: IN STD_LOGIC_VECTOR (15 DOWNTO 0); b: IN STD_LOGIC_VECTOR (15 DOWNTO 0); result: OUT STD_LOGIC_VECTOR (31 DOWNTO 0) ); END signed_mult; ARCHITECTURE rtl OF signed_mult IS SIGNAL a_int, b_int: SIGNED (15 downto 0); SIGNAL pdt_int: SIGNED (31 downto 0); BEGIN a_int <= SIGNED (a); b_int <= SIGNED (b); pdt_int <= a_int * b_int;

result <= STD_LOGIC_VECTOR(pdt_int); END rtl;

Multiplier ini digunakan untuk mengalikan komponen numerator (koefisien b) dengan komponen denumerator (koefisien a). hal ini dapat terihat pada source code pdt_int <= a_int * b_int; c. Komponen Adder sebanyak 6 unit. Source code komponen adder

-- Adder 32 bit -------------------------------------------LIBRARY IEEE; use IEEE.STD_LOGIC_1164.ALL; entity add32i is port( a, b : in STD_LOGIC_VECTOR(31 downto 0); sum : out STD_LOGIC_VECTOR(31 downto 0));

-- cout : outSTD_LOGIC ); end add32i; architecture STRUCTURE of add32i is component add16 port( a, b : in STD_LOGIC_VECTOR(15 downto 0); cin : in STD_LOGIC; sum : out STD_LOGIC_VECTOR(15 downto 0); cout : out STD_LOGIC ); end component; signal cout1, cout2, scin : STD_LOGIC; begin scin <= '0'; add16i1: add16 port map (a(15 downto 0), b(15 downto 0), scin, sum(15 downto 0), cout1); add16i2: add16 port map (a(31 downto 16), b(31 downto 16), cout1, sum(31 downto 16), cout2);

end structure; d. Komponen Divider sebanyak 2 unit. Source code nya sbb :

--Component Divider1000 --================================ library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; entity divider1000 is Port ( ain : in STD_LOGIC_VECTOR (31 downto 0); dvdout : out STD_LOGIC_VECTOR (31 downto 0)); end divider1000; architecture Behavioral of divider1000 is -- signal a ,b : bit_vector (31 downto 0);

begin

-- a <= to_bitvector(ain); -- b <= a sra 10; dvdout <= to_stdlogicvector(to_bitvector(ain) sra 10); end Behavioral;

d. Melakukan simulasi menggunakan Modelsim

Pada program Modelsim dilakukan pemberian sinyal masukan sebagai berikut :

restart -f force RST 0 10 force Din X"0A" 0, X"05" 100, X"A0" 200, X"11" 300, X"2B" 400, X"45" 500, X"32" 600, X"62" 700, X"B2" 800, X"AA" 900, X"02" 1000 force CLOCK 1 50,0 100 -repeat 100 run 1000

Progress perancangan Progress proposal ini adalah telah membuat source code untuk masing masing komponen yang kami perlukan dalam hal ini adalah :Divider,Adder,Multiplier, dan D flip flop, dan delay. Progress yang telah dilakukan adalah membuat source code yang terdiri atas komponen komponen yang ada, lalu terdapat beberapa kendala yang ada yaitu tantangan pada testbacnh dan pemberian sinyal masukan nyang berupa numerator (koefisien b) dan denumerator (koefisen (a).

Anda mungkin juga menyukai

- Kuliah 2Dokumen20 halamanKuliah 2Muslim MunawarBelum ada peringkat

- Kisi Kisi RLDokumen2 halamanKisi Kisi RLMuslim MunawarBelum ada peringkat

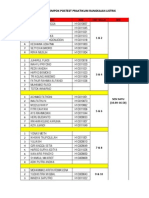

- Jadwal Jaga RLDokumen1 halamanJadwal Jaga RLMuslim MunawarBelum ada peringkat

- Kelompok Postest RLDokumen3 halamanKelompok Postest RLMuslim MunawarBelum ada peringkat

- Kuliah 2Dokumen20 halamanKuliah 2Muslim MunawarBelum ada peringkat

- Zat Yang Dalam Air Dapat Menghasilkan Ion Hidrogen Positif DisebutDokumen1 halamanZat Yang Dalam Air Dapat Menghasilkan Ion Hidrogen Positif DisebutMuslim MunawarBelum ada peringkat

- Jadwal Praktikum Semester Genap 2012,2013Dokumen1 halamanJadwal Praktikum Semester Genap 2012,2013Muslim MunawarBelum ada peringkat

- Ru IV CilacapDokumen92 halamanRu IV CilacapAmirudin100% (3)

- Prsktikum RL Kisi2Dokumen1 halamanPrsktikum RL Kisi2Muslim MunawarBelum ada peringkat

- Pengolahan Sinyal Digital B 2011 2012 12 (Bab 7 & 8)Dokumen28 halamanPengolahan Sinyal Digital B 2011 2012 12 (Bab 7 & 8)Muslim MunawarBelum ada peringkat

- 03 Isi Gabungan (Updated)Dokumen136 halaman03 Isi Gabungan (Updated)Muslim MunawarBelum ada peringkat

- Pengolahan Sinyal Digital B 2011 2012 12 (Bab 7 & 8)Dokumen28 halamanPengolahan Sinyal Digital B 2011 2012 12 (Bab 7 & 8)Muslim MunawarBelum ada peringkat

- Tugas Perancangan Sistem ElektronisDokumen17 halamanTugas Perancangan Sistem ElektronisMuslim MunawarBelum ada peringkat

- H1C010051 - Bestleader NababanDokumen11 halamanH1C010051 - Bestleader NababanMuslim MunawarBelum ada peringkat

- Soal Latihan Bab Alat OptikDokumen2 halamanSoal Latihan Bab Alat OptikMuslim MunawarBelum ada peringkat

- H1C010051 - Bestleader NababanDokumen11 halamanH1C010051 - Bestleader NababanMuslim MunawarBelum ada peringkat

- Tugas Perancangan Sistem Listrik IndustriDokumen26 halamanTugas Perancangan Sistem Listrik IndustriMuslim MunawarBelum ada peringkat

- 1 FixDokumen4 halaman1 FixMuslim MunawarBelum ada peringkat

- PR Sistem LinierDokumen1 halamanPR Sistem LinierMuslim MunawarBelum ada peringkat

- H1C010051 - Bestleader NababanDokumen11 halamanH1C010051 - Bestleader NababanMuslim MunawarBelum ada peringkat

- Simulasi Rancangan Filter Butterworth Menggunakan ModelsimDokumen4 halamanSimulasi Rancangan Filter Butterworth Menggunakan ModelsimMuslim MunawarBelum ada peringkat

- Ss - Gama Ss - GamaDokumen4 halamanSs - Gama Ss - GamaMuslim MunawarBelum ada peringkat

- Seorang Pengamat Berada Sejauh 2 M Dari Sumber Bunyi Dan Menerima Intensitas Bunyi 5 9x10Dokumen1 halamanSeorang Pengamat Berada Sejauh 2 M Dari Sumber Bunyi Dan Menerima Intensitas Bunyi 5 9x10Muslim MunawarBelum ada peringkat

- Teknologi Sistem Pengendalian Tenaga Listrik Berbasis ScadaDokumen355 halamanTeknologi Sistem Pengendalian Tenaga Listrik Berbasis ScadaMuslim Munawar100% (6)

- 1Dokumen3 halaman1Muslim MunawarBelum ada peringkat

- Program Kreatifitas Mahasiswa Adalah Pr1Dokumen3 halamanProgram Kreatifitas Mahasiswa Adalah Pr1Muslim MunawarBelum ada peringkat

- Tugas Take HomeDokumen25 halamanTugas Take HomeMuslim MunawarBelum ada peringkat

- (Pse TB) Kelompok 05Dokumen23 halaman(Pse TB) Kelompok 05Amran MaulanaBelum ada peringkat

- AK 2010 1 PendahuluanDokumen24 halamanAK 2010 1 Pendahuluanrizal4121Belum ada peringkat