Tugas Perancangan Sistem Elektronis

Diunggah oleh

Muslim MunawarHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Tugas Perancangan Sistem Elektronis

Diunggah oleh

Muslim MunawarHak Cipta:

Format Tersedia

TUGAS PERANCANGAN SISTEM ELEKTRONIS

DISUSUN OLEH : Muslim Munawar ( H1C010040)

KEMENTRIAN PENDIDIKAN DAN KEBUDAYAAN UNIVERSITAS JENDERAL SOEDIRMAN FAKULTAS SAINS DAN TEKNIK JURUSAN TEKNIK TEKNIK ELEKTRO PURBALINGGA 2012

register 4 bit

Register adalah suatu rangkaian sekuensial yang akan berfungsi menyimpan data secara sementara lalu akan mengoutputkanya jika syarat dan ketentuanya terpenuhi. Pengertian Register Register adalah komponen dalam computer yang dibangun dari gerbang logika dan flipflop.Register biasanya diukur berdasarkan bit (binary digit) yang dapat disimpan. Misalnya, register geser 4 bit, adalah register yang dapat menyimpan 4 bit. Berdasarkan data yang dikelolanya, register dapat dibedakan menjadi : 1. Register Data, digunakan untuk menyimpan bilangan integer. 2. Register Alamat, digunakan untuk menyimpan alamat yang digunakan mengakses memori. 3. Register Tujuan Umum, digunakan untuk menyimpan data maupun alamat, 4. Register floating point, digunakan untuk menyimpan bilangan titik mengambang. 5. Register Konstanta, digunakan untuk menyimpan nilai yang dapat dibaca. 6. Register Vektor, digunakan untuk menyimpan data dalam melakukan pemrosesan vector. 7. Register Tujuan Khusus, digunakan untuk menyimpan kondisi program (program state) termasuk di dalamnya pencacah program, penunjuk tumpukan (stack pointer) dan register status. 8. Register yang berhubungan dengan pengaksesan memori seperti register penahan (buffer register) register data, register alamat dan register lainnya. Register terdiri dari beberapa gerbang atau flip-flop yang saling berhubungan disusun dalam sebuahrangkaian. untuk

D flip-flop with asynchronous reset D flip flop dengan asynchronus reset adalah suatu rangkaian sekuensial yang berfungsi sebagai register dalam hal ini, lalu akan mempunyai reset asynchronus yang nantinya akan dibandingkan dengan synchronus reset, Saya akan mencoba merancang D flip-flop with asynchronous reset, berikut adalah source code dari perancangan yang telah saya buat.

LIBRARY ieee ; USE ieee.std_logic_1164.all ;

ENTITY flipflop IS PORT ( D : IN : OUT : IN std_logic_vector(3 DOWNTO 0); STD_LOGIC ; std_logic_vector(3 DOWNTO 0)) ;

Resetn, Clock Q END flipflop ;

ARCHITECTURE Behavior OF flipflop IS BEGIN PROCESS ( Resetn, Clock ) BEGIN IF Resetn = '0' THEN Q <= "0000" ; ELSIF Clock'EVENT AND Clock = '1' THEN Q <= D ; END IF ; END PROCESS ; END Behavior ; LIBRARY ieee ;

USE ieee.std_logic_1164.all ;

ENTITY flipflop_tb IS end flipflop_tb;

architecture bench of flipflop_tb is signal D : std_logic_vector(3 DOWNTO 0); signal Resetn : std_logic; signal clock :std_logic; signal Q : std_logic_vector(3 DOWNTO 0);

begin M: entity work.flipflop port map (D => D, Resetn => Resetn, clock => clock, Q => Q);

arithmetic : process is begin

D <= "1010";

Resetn <= '0'; clock <= '0'; wait for 30 ns; Resetn <= '0'; clock <= '1'; wait for 60 ns; Resetn <= '1'; clock <= '0'; wait for 80 ns; Resetn <= '1'; clock <= '1'; wait for 100 ns; Resetn <= '0'; clock <= '0'; wait for 120 ns; Resetn <= '0'; clock <= '1';

wait for 140 ns; Resetn <= '1'; clock <= '0'; wait for 160 ns; Resetn <= '1'; clock <= '1'; wait for 180 ns;

wait; end process; end architecture bench;

Hasil data flow simulasi :

Pada saat waktu 1

Pada saat waktu 2

Pada saat waktu 3

Pada saat waktu 4

syinkronus reset Entity

LIBRARY ieee ; USE ieee.std_logic_1164.all ; ENTITY flipflop IS PORT ( D : IN std_logic_vector(3 DOWNTO 0); Resetn, Clock : IN STD_LOGIC ; Q : OUT std_logic_vector(3 DOWNTO 0)) ; END flipflop ; ARCHITECTURE Behavior OF flipflop IS BEGIN PROCESS(Clock) BEGIN IF rising_edge(Clock) THEN IF Resetn = '0' THEN Q <= "0000" ; ELSE Q <= D ; END IF ; END IF; END PROCESS ; END Behavior ;

LIBRARY ieee ; USE ieee.std_logic_1164.all ;

ENTITY flipflop_tb IS end flipflop_tb;

architecture bench of flipflop_tb is signal D : std_logic_vector(3 DOWNTO 0); signal Resetn : std_logic; signal clock :std_logic;

signal Q : std_logic_vector(3 DOWNTO 0);

begin M: entity work.flipflop port map (D => D, Resetn => Resetn, clock => clock, Q => Q);

arithmetic : process is begin

D <= "1010";

Resetn <= '0'; clock <= '0'; wait for 30 ns; Resetn <= '0'; clock <= '1';

wait for 60 ns; Resetn <= '1'; clock <= '0'; wait for 80 ns; Resetn <= '1'; clock <= '1'; wait for 100 ns; Resetn <= '0'; clock <= '0'; wait for 120 ns; Resetn <= '0'; clock <= '1'; wait for 140 ns; Resetn <= '1'; clock <= '0'; wait for 160 ns; Resetn <= '1'; clock <= '1'; wait for 180 ns;

wait; end process; end architecture bench;

LIBRARY ieee ; USE ieee.std_logic_1164.all ;

ENTITY flipflop_tb IS end flipflop_tb;

architecture bench of flipflop_tb is signal D : std_logic_vector(3 DOWNTO 0); signal Resetn : std_logic; signal clock :std_logic; signal Q : std_logic_vector(3 DOWNTO 0);

begin M: entity work.flipflop port map (D => D, Resetn => Resetn, clock => clock, Q => Q);

arithmetic : process is begin

D <= "1010";

Resetn <= '0'; clock <= '0'; wait for 30 ns; Resetn <= '0'; clock <= '1'; wait for 60 ns;

Resetn <= '1'; clock <= '0'; wait for 80 ns; Resetn <= '1'; clock <= '1'; wait for 100 ns; Resetn <= '0'; clock <= '0'; wait for 120 ns; Resetn <= '0'; clock <= '1'; wait for 140 ns; Resetn <= '1'; clock <= '0'; wait for 160 ns; Resetn <= '1'; clock <= '1'; wait for 180 ns;

wait;

end process; end architecture bench;

Anda mungkin juga menyukai

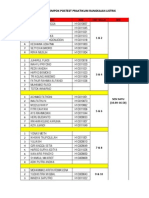

- Jadwal Praktikum Semester Genap 2012,2013Dokumen1 halamanJadwal Praktikum Semester Genap 2012,2013Muslim MunawarBelum ada peringkat

- Zat Yang Dalam Air Dapat Menghasilkan Ion Hidrogen Positif DisebutDokumen1 halamanZat Yang Dalam Air Dapat Menghasilkan Ion Hidrogen Positif DisebutMuslim MunawarBelum ada peringkat

- Kisi Kisi RLDokumen2 halamanKisi Kisi RLMuslim MunawarBelum ada peringkat

- Kuliah 2Dokumen20 halamanKuliah 2Muslim MunawarBelum ada peringkat

- Kelompok Postest RLDokumen3 halamanKelompok Postest RLMuslim MunawarBelum ada peringkat

- Kuliah 2Dokumen20 halamanKuliah 2Muslim MunawarBelum ada peringkat

- H1C010051 - Bestleader NababanDokumen11 halamanH1C010051 - Bestleader NababanMuslim MunawarBelum ada peringkat

- 03 Isi Gabungan (Updated)Dokumen136 halaman03 Isi Gabungan (Updated)Muslim MunawarBelum ada peringkat

- Jadwal Jaga RLDokumen1 halamanJadwal Jaga RLMuslim MunawarBelum ada peringkat

- Pengolahan Sinyal Digital B 2011 2012 12 (Bab 7 & 8)Dokumen28 halamanPengolahan Sinyal Digital B 2011 2012 12 (Bab 7 & 8)Muslim MunawarBelum ada peringkat

- Prsktikum RL Kisi2Dokumen1 halamanPrsktikum RL Kisi2Muslim MunawarBelum ada peringkat

- PR Sistem LinierDokumen1 halamanPR Sistem LinierMuslim MunawarBelum ada peringkat

- Ru IV CilacapDokumen92 halamanRu IV CilacapAmirudin100% (3)

- Pengolahan Sinyal Digital B 2011 2012 12 (Bab 7 & 8)Dokumen28 halamanPengolahan Sinyal Digital B 2011 2012 12 (Bab 7 & 8)Muslim MunawarBelum ada peringkat

- Soal Latihan Bab Alat OptikDokumen2 halamanSoal Latihan Bab Alat OptikMuslim MunawarBelum ada peringkat

- H1C010051 - Bestleader NababanDokumen11 halamanH1C010051 - Bestleader NababanMuslim MunawarBelum ada peringkat

- H1C010051 - Bestleader NababanDokumen11 halamanH1C010051 - Bestleader NababanMuslim MunawarBelum ada peringkat

- Simulasi Rancangan Filter Butterworth Menggunakan ModelsimDokumen4 halamanSimulasi Rancangan Filter Butterworth Menggunakan ModelsimMuslim MunawarBelum ada peringkat

- 1 FixDokumen4 halaman1 FixMuslim MunawarBelum ada peringkat

- Proposal Proyek Perancangan Sistem ElektronisDokumen14 halamanProposal Proyek Perancangan Sistem ElektronisMuslim MunawarBelum ada peringkat

- Ss - Gama Ss - GamaDokumen4 halamanSs - Gama Ss - GamaMuslim MunawarBelum ada peringkat

- Teknologi Sistem Pengendalian Tenaga Listrik Berbasis ScadaDokumen355 halamanTeknologi Sistem Pengendalian Tenaga Listrik Berbasis ScadaMuslim Munawar100% (6)

- Seorang Pengamat Berada Sejauh 2 M Dari Sumber Bunyi Dan Menerima Intensitas Bunyi 5 9x10Dokumen1 halamanSeorang Pengamat Berada Sejauh 2 M Dari Sumber Bunyi Dan Menerima Intensitas Bunyi 5 9x10Muslim MunawarBelum ada peringkat

- Tugas Perancangan Sistem Listrik IndustriDokumen26 halamanTugas Perancangan Sistem Listrik IndustriMuslim MunawarBelum ada peringkat

- (Pse TB) Kelompok 05Dokumen23 halaman(Pse TB) Kelompok 05Amran MaulanaBelum ada peringkat

- Tugas Take HomeDokumen25 halamanTugas Take HomeMuslim MunawarBelum ada peringkat

- 1Dokumen3 halaman1Muslim MunawarBelum ada peringkat

- AK 2010 1 PendahuluanDokumen24 halamanAK 2010 1 Pendahuluanrizal4121Belum ada peringkat

- Program Kreatifitas Mahasiswa Adalah Pr1Dokumen3 halamanProgram Kreatifitas Mahasiswa Adalah Pr1Muslim MunawarBelum ada peringkat