Paper Poak

Paper Poak

Diunggah oleh

Alvian Dwi KHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Paper Poak

Paper Poak

Diunggah oleh

Alvian Dwi KHak Cipta:

Format Tersedia

Tabel 4 juga menunjukkan pitch pad yang diperlukan untuk CPU IC.

Jika kami telah menerapkan sistem A dengan bantalan I/O perifer sebagai pengganti daerah I/O, CPU pitch pad akan di bawah 60 mikron. Sebuah konfigurasi akan sulit untuk ikatan kawat, dan pemasangan flip-chip akan menjadi mustahil. Pada daerah I/O teknologi yang digunakan dalam sistem A, di sisi lain, memungkinkan pitch pad nyaman. Biaya Implikasi Dalam membandingkan biaya implementasi tiga studi kasus, kami dianggap sebagai daerah yang dikonsumsi pada PCB motherboard. Semua data biaya diasumsikan pada sebuah produksi volume yang tinggi per tahun (lebih dari 1.000.000). Oleh karena itu kami tidak mempertimbangkan perubahan biaya tidak berulang yang akan dihasilkan dari metodologi desain berbeda. Berdasarkan asumsi kami, biaya kubus/ chip pada dua pertimbangan. Pertama, beberapa program kubus yang dikenal baik menawarkan biaya yang sama dan sama-sama menguji tingkat untuk dikemas dan kubus terbuka. Kedua, ukuran kubus mengemudi biaya kubus: mengurangi ukuran kubus mengurangi biaya kubus (Lihat sistem A dalam tabel 5). Di tingkat chip, tidak ada tambahan lapisan logam yang diperlukan untuk daerah I/O, seperti bantalan untuk bump interkoneksi dapat ditempatkan di atas daerah aktif. Juga, kepadatan routing jauh lebih rendah di atas dua lapisan logam pada IC karena desainer tempat pin elektronik dekat dengan bantalan I/O dan output inti. Selain itu, dengan menghubungkan kekuatan lokal, kita dapat menghapus rel listrik yang besar. Di tingkat substrat, 44% ukuran pengurangan substrat MCM pada sistem A memerlukan lapisan logam tambahan untuk memberikan cukup ruang kabel. Di tingkat utama papan PCB, daerah bisa berkurang sebesar 20% dibandingkan dengan sistem S. CHIP-KEMASAN KODE TANDA Selain itu, substrat biaya yang lebih tinggi pada system A diharapkan menurun sebab produksi panel daerah besar substrat MCM-D, yang mengurangi biaya keseluruhan bahkan lebih. Masa Depan Arsitektur Area I/O segera dapat meningkatkan sistem kinerja serta mengurangi ukuran sistem, berdasarkan keadaan seni arsitektur. Arsitektur jalur seperti dual independen bus pada Intel dan grafis port bus yang canggih, dan pendekatan yang lebih baru, juga dapat memanfaatkan I/O hitungan yang lebih tinggi pada Area I/O. Area I/O juga menawarkan pilihan partisi baru. Gambar 5 menunjukkan arsitektur masa depan yang mungkin di mana desainer dapat memindahkan blok fungsional atau menonaktifkan chip. Dengan proses lebih efisien SRAM, daripada SRAM terintegrasi dalam proses logika, daerah aktif menyusut oleh lebih dari setengah. Oleh karena itu, firstlevel cache dapat dipindahkan dari chip yang meningkatkan hasil mati CPU tanpa kerugian kinerja. Selain itu, Gambar 5 menunjukkan controller DRAM dilaksanakan pada chip CPU, yang menjamin latency rendah dan memungkinkan dua independen DRAM Bank. Dengan arsitektur ini, desainer bebas dapat mendistribusikan CPU % u2019s fungsi MCM untuk mencapai kinerja yang optimal dan hasil.

Kami menggunakan alat pemodelan biaya lingkungan optimasi Modular (MOE) untuk membuat perhitungan. Biaya proses berorientasi struktur representasi MOE memungkinkan kita mudah menganggap berbeda manufaktur hasil konfigurasi. Simulasi Monte Carlo menggunakan, MOE menghitung biaya untuk garis virtual proses, termasuk biaya langsung, biaya nonrecurring, tes, dan hasil. Dalam baris ini proses virtual, MOE mengasumsikan tes fungsional sebelum sistem adalah dikirim, yang memilah setiap unit yang mengandung kesalahan. Kerugian hasil ini ditambahkan ke biaya langsung setiap sistem yang dikirim. Tabel 6 rincian hasil. Tabel 6 menunjukkan bahwa sistem S memiliki biaya langsung yang lebih tinggi daripada sistem P. Hal ini sebagian besar disebabkan MCM substrat biaya tinggi dan kerugian hasil yang disebabkan oleh kawat ikatan. System sebuah memiliki biaya langsung terendah dari semua tiga implementasi. Interkoneksi adalah kunci untuk menutup kesenjangan antara kecepatan bus on dan offchip. Daerah I/O interkoneksi teknologi tertentu menunjukkan janji untuk bertemu hitung pin peningkatan yang diramalkan oleh NTRS. Menawarkan peningkatan bandwidth (karena hitungan I/O yang lebih tinggi), dan manufaktur kendala yang lebih sedikit (karena substrat besar pad lapangan) dengan lebih sedikit biaya (karena ukuran chip berkurang). Karena ikatan benjolan, area I/O memiliki lebih pendek interkoneksi panjang dan parasitics lebih rendah, yang meningkatkan sinyal kecepatan dan kualitas. Lapangan santai juga meningkatkan manufakturabilitas serta keandalan perakitan. Daerah I/O juga akan menguntungkan masyarakat CSP karena interposer bisa tetap sangat sederhana, tanpa pad redistribusi. Akhirnya, degradasi kecepatan diperkenalkan oleh CSP menjadi marjinal. Tantangan berikutnya akan menjadi bukti hardware dari konsep. Kesulitan termasuk kurangnya alat yang cocok yang memungkinkan pertukaran data antara paket, IC dan PCB Designer, dan bangunan virtual prototipe untuk merancang sistem yang optimal. Chip-tingkat daerah I/O, di terpadu chip, paket, dan tingkat sistem Desain, memiliki potensi untuk menawarkan banyakperbaikan kinerja komputasi. Tapi pertemuan prediksi menantang peta jalan NTRS, terutama yang berkaitan dengan bus off-chip optimis, memerlukan kerjasama yang lebih erat antara desainer chip, paket dan sistem. Kemudian, kita dapat yakin bahwa sistem mikroprosesor cepat memang hanya di sekitar corner. Ucapan terima kasih Kami berterima kasih kepada rekan-rekan D. Ammann, A. Thiel, dan C. Habiger untuk diskusi berharga dan komentar berguna.

Referensi 1. National Technology Roadmap for Semiconductors, Sematech, Austin, Texas, 1994; http://www.sematech.org/public/ roadmap/. 2. D. Patterson et al., A Case for Intelligent RAM, IEEE Micro, Vol. 17, No. 2, Apr. 1997, pp. 34-44. 3. P.D. Franzon, Multichip ModuleTechnologies and Alternatives, Van Nostrand Reinhold, New York, 1993. 4. R. Fillion et al., Demonstration of a Chip-Scale Chip-on-Flex Technology, Proc. Intl Conf. Multichip Modules, Intl Soc. for Hybrid Microelectronics, Reston, Va., Apr. 1996, pp. 351-356. 5. Q. Zhu and S. Tam, Package Clock Distribution Design Optimization for High-Speed and Low-Power VLSIs, IEEE Trans. CPMT, Part B, Feb. 1997. 6. P. Phiroze et al., CAD Tools for Area-Distributed I/O Pad Packaging, Proc. IEEE Multichip Module Conf., IEEE Press, Piscataway, N.J., 1997, pp. 125-129. 7. E. Hirt et al., A Pentium-Based MCM for Embedded Computing, Proc. 11th European Microelectronics Conf., Intl Soc. for Hybrid Microelectronics, 1997, pp. 516- 523. 8. Intel Corp., Mobile Pentium Processor with MMX Technology on .25 Micron, 1997; http://developer.intel.com/design/mobile/datashts/243468.htm. 9. Intel Corp., Pentium Processor Family Developers Manual, Mt. Prospect, Ill., 1995. 10. M. Scheffler et al., MOEA Modular Optimization Environment for Concurrent Cost Reduction, Proc. Fifth European Concurrent Eng. Conf., SCS Europe Bvba, Ghent, Belgium, 1998, pp. 115-119. 11. N. Ammann, LapThe Key to Low Cost Multichip Packaging, Future Circuits Intl, Vol. 2, 1997, pp. 25-28. 12. L. Schaper, Seamless High Off-Chip Connectivity (SHOCC), Proc. IEEE Intl Workshop on Chip Package Co-Design, CPD 98 Secretary, c/o Electronics Laboratory ETH, Zrich, Switzerland, 1998, pp. 39-45. 13. E. Hirt et al., On the Impact of Area I/O on Partitioning: A New Perspective, Proc. IEEE Intl Workshop on Chip Package Co-Design, CPD 98 Secretary, c/o Electronics Laboratory ETH, 1998, pp. 33-38.

Etienne Hirt adalah calon PhD dalam kelompok MCM laboratorium elektronik di Swiss Federal Institute of Technology (ETH) Z kaya, Swiss. Minat penelitiannya mencakup metodologi desain sistem dan paket yang menggunakan teknologi MCM. Hirt menerima gelar MS di bidang electrical engineering dari ETH Z kaya. Dia adalah anggota IEEE mahasiswa. Michael Scheffler adalah calon PhD dalam kelompok MCM laboratorium elektronik, ETH Z kaya. Minat penelitiannya mencakup Otomasi perancangan rangkaian elektronika, biaya pemodelan dan optimasi. Scheffler menerima Dipl.Ing. (MS) gelar di bidang electrical engineering dari Technical University, Berlin, Jerman. Dia adalah anggota IEEE mahasiswa. Jean-Pierre Wyss adalah calon PhD dalam kelompok MCM laboratorium elektronik, ETH Z kaya. Ketertarikannya termasuk MCM tes strategi dan desain MCMs tinggi-kompleksitas. Dia adalah salah seorang pendiri dari Anda-blox ag, sebuah perusahaan spin-off kaya ETH Z. u-blox ag menyediakan solusi inovatif dan efektif Elektronik kemasan untuk berbagai macam aplikasi. Wyss menerima gelar MS di bidang electrical engineering dari ETH Z kaya. Dia adalah mahasiswa anggota IEEE dan IEEE Computer Society. Pertanyaan langsung mengenai artikel ini untuk Etienne Hirt, laboratorium elektronik, ETH Z kaya, CH-8092, Z kaya, Swiss; Hirt@Ife.ee.ethz.ch.

Anda mungkin juga menyukai

- Soal Ujian Akhir Sarmag Si Smsi03 2012Dokumen2 halamanSoal Ujian Akhir Sarmag Si Smsi03 2012Alvian Dwi KBelum ada peringkat

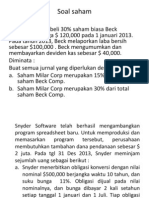

- Contoh Soal Latihan FirmaDokumen1 halamanContoh Soal Latihan FirmaAlvian Dwi KBelum ada peringkat

- Soal Latihan ObligasiDokumen5 halamanSoal Latihan ObligasiAlvian Dwi K100% (1)

- Soal HPP ProsesDokumen3 halamanSoal HPP ProsesAlvian Dwi KBelum ada peringkat

- PKMDokumen17 halamanPKMAlvian Dwi KBelum ada peringkat

- Peripheral and Area IDokumen2 halamanPeripheral and Area IAlvian Dwi KBelum ada peringkat

- Metode Simpleks, Metode Simpleks Yang Direvisi DanDokumen36 halamanMetode Simpleks, Metode Simpleks Yang Direvisi DanAlvian Dwi K50% (2)