Bab Iii

Diunggah oleh

Nesta89Judul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Bab Iii

Diunggah oleh

Nesta89Hak Cipta:

Format Tersedia

BAB III PERENCANAAN SISTEM

Pada bab ini akan di bahas perencanaan dan pembuatan hardware sistem yang akan di gunakan meliputi : 1. Tujuh Rangkaian Elektronika 1 Bagian Dua 2. Volmeter Dc Dan Potensio Meter Untuk Mengukur Setiap Tegangan/Arus Yang Ada Di 7 Percobaan Rangkaian Elektronika 1 Bagian Dua. 3. Resistor,Transistor,dan Dioda

Power Supply

Prcb n8

Prcbn 9

Prcbn 10

Prcb n 11

Prcbn 12

Prcbn 13

Prcb n 14

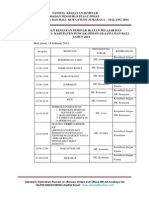

Gambar 3.1 Block Diagram Sistem Keseluruhan Rangkaian Percobaan

25

26

3.1

Transistor Emitter Biasing

Gambar 3.2 Rangkaian bias emitter Tujuan Pembuktian tegangan dan arus pada rangkaian bias emitter, sebagaimana perencanaannya dengan garis beban, untuk menentukan titik kerja rangkaian (Q). Tidak seperti rangkaian bias yang lain, Rangkaian bias emitter ini menggunakan supply tegangan positip dan negatip. 3.2 Transistor Voltage Divider Biasing Tujuan :

Pembuktian tegangan dan arus pada rangkaian bias pembagi tegangan sebagaimana perencanaannya dengan garis beban untuk menentukan titik kerja rangkaian (Q). Rangkaian bias pembagi tegangan seringkali dugunakan karena arus base dibuat kecil dibanding dengan arus yang melalui resistansi pada sisi base (voltage divider). Sebagai hasilnya, arus pada kolektor relatif stabil terhadap perubahan nilai dari transistor.

27

Gambar 3.3 Rangkaian bias pembagi tegangan

3.3 Transistor Collector-Feedback Biasing Tujuan Pembuktian tegangan dan arus pada rangkaian bias collector-feedback sebagaimana perencanaannya dengan garis beban untuk menentukan titik kerja rangkaian (Q). Rangkaian bias collector-feedback berbeda dengan rangkaian bias yang lain. Perbedaannya adalah, tegangan collector memberikan bias untuk junction baseemitter. Hasilnya adalah titik Q sangat stabil, sehingga akan mengurangi efek dari penguatan arus ().

Gambar 3.4 Rangkaian bias collector-feedback

28

3.4 Kurva Transfer Karakteristik Jfet Tujuan Membuat kurva tranfer karakteristik JFET pada layar oscilloscope. Kurva ini memperlihatkan variasi arus drain (ID) sebagai fungsi tegangan gate-source (VGS). Dari kurva ini dapat diestimasikan nilai dari parameter-parameter JFET, meliputi IDSS (nilai arus drain, dimana gate dan source kondisi short, atau VGS = 0), VGS (off) (tegangan cut-off dari gate-source) dan gm0 (transkonduktansi forward).

Gambar 3.5 Rangkaian penyearah setengah gelombang (HW)

3.5 Jfet Self Bias Tujuan Tujuan dari percobaan ini adalah verifikasi tegangan dan arus pada rangkaian JFET dengan menggunakan self bias. Yaitu membuktikan kesesuaian tegangan dan

29

arus pada rangkaian self bias dari JFET dengan perencanaan sebelumnya, untuk menentukan titik kerja rangkaian (Q).

Gambar 3.6 Rangkaian penyearahan gelombang penuh metoda bridge 3.6 Rangkaian Penguat Common Emitter Tujuan : Mendemonstrasikan prinsip kerja dan karakteristik dari rangkaian penguat common emtter sinyal kecil. Investigasi pengaruh dari penguatan tegangan.

Gambar 3.7 Rangkaian penguat common emitter

30

3.7

Rangkaian Penguat Common Colector

Tujuan : 1. Mendemonstrasikan prinsip kerja dan karakteristik dari rangkaian penguat sinyal kecil common collector. 2. Investigasi pengaruh dari penguatan tegangan.

Gambar 3.8 Rangkaian percobaan penguat common collector

Anda mungkin juga menyukai

- Visi Dan Misi Intan Jaya 17-23Dokumen27 halamanVisi Dan Misi Intan Jaya 17-23Nesta89Belum ada peringkat

- Contoh Rancangan Satpol PPDokumen18 halamanContoh Rancangan Satpol PPNesta89Belum ada peringkat

- Contoh Rancangan PerawatDokumen19 halamanContoh Rancangan PerawatNesta89Belum ada peringkat

- Contoh Rancangan Surat MasukDokumen20 halamanContoh Rancangan Surat MasukNesta89Belum ada peringkat

- Rancangan Aktualisasi PrintDokumen35 halamanRancangan Aktualisasi PrintNesta89Belum ada peringkat

- Organisasi IpmapDokumen32 halamanOrganisasi IpmapNesta89100% (2)

- Contoh Rancangan BidanDokumen21 halamanContoh Rancangan BidanNesta89Belum ada peringkat

- Themah 2Dokumen34 halamanThemah 2Nesta89Belum ada peringkat

- Hari Jumat, 14 Februari 2014Dokumen4 halamanHari Jumat, 14 Februari 2014Nesta89Belum ada peringkat

- Daftar PustakaDokumen3 halamanDaftar PustakaNesta89Belum ada peringkat

- IsiDokumen21 halamanIsiNesta89Belum ada peringkat

- Bab IiDokumen21 halamanBab IiNesta89Belum ada peringkat

- Bab VDokumen2 halamanBab VDianyanekBelum ada peringkat

- Bab IvDokumen16 halamanBab IvNesta89Belum ada peringkat

- Bab IDokumen3 halamanBab INesta89Belum ada peringkat

- Daftar IsiDokumen9 halamanDaftar IsiNesta89Belum ada peringkat