Job Sheet 2 Gate or (Ic 7432)

Diunggah oleh

hadhiutomoJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Job Sheet 2 Gate or (Ic 7432)

Diunggah oleh

hadhiutomoHak Cipta:

Format Tersedia

Nama : Mohamad Sidik H.

Kelas : XI KM A GATE OR ( IC 7432 )

Tanggal : 14 Oktober 2012 Nilai : Paraf :

I.

Tujuan - Membuktikan tabel kebanaran Gate OR - Mempelajari konsep multiple input Gate OR - Menyatakan persamaan Boolean dari suatu rangkaian Gate OR

II.

Pendahuluan Gerbang OR akan memberikan sinyal keluaran tinggi jika salah satu atau semua sinyal masukan bernilai tinggi, sehingga dapat dikatakan bahwa gerbang OR hanya memiliki sinyal keluaran rendah jika semua sinyal masukan bernilai rendah. Gerbang OR akan memberikan nilai output yang berlogic 1 apabila salah satu inputnya bernilai 1, apabila menginginkan berlogic 0 kedua input harus berlogic 0.

III.

Peralatan - IC 7432 - Trainer Digital - Kabel Jumper

IV.

Gambar Kerja

V.

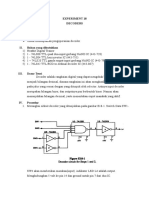

Langkah Kerja 1. Rangkai seperti gambar di bawah ini !

Gambar Rangkaian 1 2. Tuliskan persamaan output di : L1 = Sa + Sb L2 = (Sa + Sb) + Sc Rangkaian seperti di atas disebut Gate OR 3 Input, sehingga simbolnya menjadi :

3. Atur switch - switch (Sa, Sb dan Sc ) input menurut tabel kebenaran di bawah dan catat hasil output di L1 dan L2 ! (Tabel Kebenaran Rangkaian 1) 4. Rangkai gambar di bawah !

Gambar Rangkaian 2 5. Tuliskan persamaan output di : L1 = Sa + Sb L2 = (Sa + Sb) + Sc L3 = ((Sa + Sb) + Sc) + Sd 6. Atur switch-switch (Sa, Sb, Sc dan Sd) input menurut tabel kebanaran di bawah dan catat hasil output di L1, L2 dan L3 ! (Tabel Kebenaran Rangkaian 2)

VI.

Hasil Praktikum OR 3 INPUT

0-0-0

INPUT Sa 0 0 0-0-1 0 0 1 1 1 1 Sb 0 0 1 1 0 0 1 1 Sc 0 1 0 1 0 1 0 1

OUTPUT L1 0 0 1 1 1 1 1 1 L2 0 1 1 1 1 1 1 1

Tabel Kebenaran Rangkaian 1 0-1-0

0-1-1

100 11

1-0-1

1-1-0

1-1-1

OR 4 INPUT

0-0-0-0

INPUT 0-0-0-1 Sa 0 0 0 0 0 0 0 0-0-1-0 0 1 1 1 1 1 1 1 1 Sb 0 0 0 0 1 1 1 1 0 0 0 0 1 1 1 1 Sc 0 0 1 1 0 0 1 1 0 0 1 1 0 0 1 1 Sd 0 1 0 1 0 1 0 1 0 1 0 1 0 1 0 1 L1 0 0 0 0 1 1 1 1 1 1 1 1 1 1 1 1

OUTPUT L2 0 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 L3 0 1 1 1 1 1 1 1 1 1 1 1 1 1 1 1

Tabel Kebenaran Rangkaian 2

0-0-1-1

0-1-0-0

0-1-0-1

0-1-1-0

0-1-1-1

1-0-0-0

1-0-0-1

1-0-1-0

1-0-1-1

1-1-0-0

1-1-0-1

1-1-1-0

1-1-1-1

VII.

Analisa Persamaan output yang didapat setelah melakukan pengujian, yaitu : a. L1 = Sa+Sb b. L1 = (Sa+Sb)+Sc c. L3 = ((Sa+Sb)+Sc+Sd

Berdasar kepada perhitungan output berlogic 1 (high) apabila salah satu atau semua input diberi logic 1.

VIII.

Pertanyaan 1. Diketahui Gate OR 3 input A, B dan C. Input A dan B tidak diketahui sedangkan input C diketahui High, maka outputnya adalah high 2. Kalau kita mempunyai Gate OR 2 input, berapa buah Gate OR seperti tersebut untuk menghasilkan 8 input ? 7 Gate 3. Gambarkan rangkaian digital untuk persamaan Q = ( A + B ). C !

4.

Output Gate OR akan Low jika semua inputnya adalah low

IX.

Kesimpulan GATE OR ini akan memiliki output berlogic 1 (high) apabila salah satu atau semua input diberi logic 1. Dan sebaliknya, jika semua input diberi logic 0, maka outputnya akan berlogic 0.

Anda mungkin juga menyukai

- 6th Central Pay Commission Salary CalculatorDokumen15 halaman6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- 6th Central Pay Commission Salary CalculatorDokumen15 halaman6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Job Sheet 5 Gate Nor (Ic 7402)Dokumen8 halamanJob Sheet 5 Gate Nor (Ic 7402)hadhiutomoBelum ada peringkat

- Job Sheet 1 Gate and (Ic 7408)Dokumen9 halamanJob Sheet 1 Gate and (Ic 7408)hadhiutomoBelum ada peringkat

- Laporan Gate or (IC 7432)Dokumen12 halamanLaporan Gate or (IC 7432)Fraiza Geraldi Alghifary100% (2)

- Job Sheet 3 Gate Nand (Ic 7400)Dokumen7 halamanJob Sheet 3 Gate Nand (Ic 7400)hadhiutomoBelum ada peringkat

- Job Sheet 7 Gate Ex - NorDokumen3 halamanJob Sheet 7 Gate Ex - NorhadhiutomoBelum ada peringkat

- Laporan Gate and (IC 7408)Dokumen12 halamanLaporan Gate and (IC 7408)Fraiza Geraldi AlghifaryBelum ada peringkat

- Job Sheet 3Dokumen5 halamanJob Sheet 3intan103Belum ada peringkat

- Gerbang EX-ORDokumen10 halamanGerbang EX-OROpal Afra RamizBelum ada peringkat

- Job Sheet 6Dokumen7 halamanJob Sheet 6FarhanihanBelum ada peringkat

- Job Sheet 1 - Gate andDokumen11 halamanJob Sheet 1 - Gate andintan103Belum ada peringkat

- Laporan Gate EX-Or (IC 7486)Dokumen9 halamanLaporan Gate EX-Or (IC 7486)Fraiza Geraldi AlghifaryBelum ada peringkat

- GERBANG DASAR DAN TAMBAHANDokumen30 halamanGERBANG DASAR DAN TAMBAHANAngga T. NugrohoBelum ada peringkat

- Laporan Gate Ex - orDokumen11 halamanLaporan Gate Ex - orDoniramdani17Belum ada peringkat

- Laporan Job 3 NandDokumen7 halamanLaporan Job 3 NandaaswardaniBelum ada peringkat

- OR IrwanDokumen5 halamanOR Irwanabigaels3Belum ada peringkat

- AND-OR-GATESDokumen6 halamanAND-OR-GATESpakpak chanelBelum ada peringkat

- Revin Nor (Ic 7402)Dokumen5 halamanRevin Nor (Ic 7402)revin novian juliadiBelum ada peringkat

- LAPORAN LAB ELDA SekuensialDokumen17 halamanLAPORAN LAB ELDA SekuensialNabilaBelum ada peringkat

- Laporan Digital 1.shantyDokumen22 halamanLaporan Digital 1.shantySantiPutriBelum ada peringkat

- MODUL GERBANG LOGIKADokumen37 halamanMODUL GERBANG LOGIKAWesley RondonuwuBelum ada peringkat

- Laporan Gerbang Dasar LogikaDokumen10 halamanLaporan Gerbang Dasar Logikaamy_hamida5283Belum ada peringkat

- Bab1 KonsepDasarDokumen42 halamanBab1 KonsepDasarIndo NesiaBelum ada peringkat

- Revin Ex-OR (IC 7486)Dokumen3 halamanRevin Ex-OR (IC 7486)revin novian juliadiBelum ada peringkat

- Laporan Gate NAND (IC 7400)Dokumen7 halamanLaporan Gate NAND (IC 7400)Fraiza Geraldi AlghifaryBelum ada peringkat

- EncoderDokumen19 halamanEncoderNoor Muhammad RizkiBelum ada peringkat

- Gerbang LogikaDokumen27 halamanGerbang LogikaArlita Kusuma Dewi0% (1)

- Laporan Praktikum - SD 2 - M.Rizqi - Maulana - 211091900049Dokumen16 halamanLaporan Praktikum - SD 2 - M.Rizqi - Maulana - 211091900049MUHAMAD RIZQI MAULANABelum ada peringkat

- Gerbang NANDDokumen5 halamanGerbang NANDOpal Afra RamizBelum ada peringkat

- Gerbang NORDokumen7 halamanGerbang NOROpal Afra RamizBelum ada peringkat

- Jobsheet 2Dokumen11 halamanJobsheet 2trafalgar48Belum ada peringkat

- Gerbang Dasar Logika (Elementary Logic Gate)Dokumen15 halamanGerbang Dasar Logika (Elementary Logic Gate)Abie TamaBelum ada peringkat

- GERBANG LOGIKADokumen18 halamanGERBANG LOGIKAtonnyBelum ada peringkat

- Laporan Lab Digital Praktikum 1Dokumen11 halamanLaporan Lab Digital Praktikum 1hakazawahikariBelum ada peringkat

- OPTIMIZED TITLE FOR LOGIC GATE DOCUMENTDokumen7 halamanOPTIMIZED TITLE FOR LOGIC GATE DOCUMENTnoeditaBelum ada peringkat

- Gerbang Logika DigitalDokumen5 halamanGerbang Logika DigitalAinun Widi CahyaningrumBelum ada peringkat

- Laporan Praktikum Sistem Digital Gerbang-Gerbang LogikaDokumen76 halamanLaporan Praktikum Sistem Digital Gerbang-Gerbang LogikanisaBelum ada peringkat

- Modul Pertemuan 5Dokumen10 halamanModul Pertemuan 5Ika CandradewiBelum ada peringkat

- Praktikum Elektronika Digital Gerbang LogikaDokumen10 halamanPraktikum Elektronika Digital Gerbang LogikaAnanda imeeBelum ada peringkat

- Unit 11 Nota Digital1Dokumen11 halamanUnit 11 Nota Digital1Fedrick EdwinBelum ada peringkat

- TEKNIK DIGITALDokumen37 halamanTEKNIK DIGITALVano HashiramaBelum ada peringkat

- PraktikumDokumen10 halamanPraktikumAndi NurfauziaBelum ada peringkat

- Experiment 18 - DecoderDokumen7 halamanExperiment 18 - DecoderWildana HusnaBelum ada peringkat

- elektronika digital gerbang logikaDokumen5 halamanelektronika digital gerbang logikaFukuda MineBelum ada peringkat

- LAPORAN PRAKTIKUM LOGIKA DASARDokumen35 halamanLAPORAN PRAKTIKUM LOGIKA DASARalisaBelum ada peringkat

- Laporan Praktikum Gerbang Logika or Gate Not Gate Dan CampuranDokumen10 halamanLaporan Praktikum Gerbang Logika or Gate Not Gate Dan Campuran11. Chania Rizgita DewiBelum ada peringkat

- MODUL DASAR GERBANG LOGIKADokumen17 halamanMODUL DASAR GERBANG LOGIKARendy MuhammadBelum ada peringkat

- Gerbang LogikaDokumen22 halamanGerbang LogikamutiaBelum ada peringkat

- Laporan Gate NOR (IC 7402)Dokumen11 halamanLaporan Gate NOR (IC 7402)Fraiza Geraldi AlghifaryBelum ada peringkat

- MODUL LOGIKA DIGITALDokumen72 halamanMODUL LOGIKA DIGITALImtiyaz ZuhanBelum ada peringkat

- 4 Gebang LogikaDokumen36 halaman4 Gebang LogikaGaluh SandiBelum ada peringkat

- Laporan Logika IDokumen12 halamanLaporan Logika Iluh_eka100% (1)

- Laporan Rangkaian DigitalDokumen37 halamanLaporan Rangkaian DigitalV-Tex AchielBelum ada peringkat

- Laporan Percobaan 1 Gerbang Logika DasarDokumen44 halamanLaporan Percobaan 1 Gerbang Logika DasarTedoHarisChandra100% (1)

- GERBANG DASARDokumen10 halamanGERBANG DASARRenasSinaga 0308Belum ada peringkat

- Gerbang LogikaDokumen18 halamanGerbang LogikaArya Wahyu Wibowo100% (1)

- Counter UpDokumen6 halamanCounter UphadhiutomoBelum ada peringkat

- Register JKDokumen7 halamanRegister JKhadhiutomoBelum ada peringkat

- JK FFDokumen5 halamanJK FFhadhiutomoBelum ada peringkat

- Counter UpDokumen6 halamanCounter UphadhiutomoBelum ada peringkat

- Register JKDokumen7 halamanRegister JKhadhiutomoBelum ada peringkat

- Counter DownDokumen6 halamanCounter DownhadhiutomoBelum ada peringkat

- D FFDokumen5 halamanD FFhadhiutomoBelum ada peringkat

- JK FFDokumen5 halamanJK FFhadhiutomoBelum ada peringkat

- SR FFDokumen5 halamanSR FFhadhiutomoBelum ada peringkat

- Job Sheet 8 AdderDokumen6 halamanJob Sheet 8 AdderhadhiutomoBelum ada peringkat

- Job Sheet 4 Gate Not (Ic 7404)Dokumen3 halamanJob Sheet 4 Gate Not (Ic 7404)hadhiutomoBelum ada peringkat