SR FF

Diunggah oleh

hadhiutomoHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

SR FF

Diunggah oleh

hadhiutomoHak Cipta:

Format Tersedia

Nama : Mohamad Sidik H.

Kelas : XI KM A SR FLIP FLOP

Tanggal : 22 Mei 2013 Nilai : Paraf :

I. Tujuan - Menguji dan mengobservasi rangkaian SR FLIP FLOP - Membuat tabel kebenaran untuk masing-masing flip flop dengan eksperimen

II. Pendahuluan SR FLIP FLOP adalah sirkit logic yang mempunyai dua kemungkinan kedudukan atau bi-stabil (memory). Sirkit itu disusun sedemikian rupa sehingga kalau ada suatu taraf siap berfungsi (enable) pada S (adalah kedudukan lawannya) maka akan menghasilkan Q = Rendah.

III. Peralatan - IC 7402, 7400 - Trainer Digital - Kabel Jumper - Circuit maker

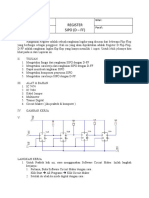

IV. Gambar Kerja

V.

Langkah Kerja 1. Siapkan alat dan bahan 2. Rangkai rangkaian sesuai gambar 3. Catat hasil praktikum pada tabel kebenaran 4. Periksakan hasilnya ke guru 5. Bila ada yang kurang jelas tanyakan ke guru

VI.

Hasil Praktikum

TIMING DIAGRAM

TABEL KEBENARAN C 1 1 1 1 1 1 1 1 1 1 S 0 1 1 1 0 0 1 1 1 0 R 1 0 1 0 1 0 0 1 0 1 L1 0 1 1 1 0 0 1 1 1 0 L2 1 0 1 0 1 1 0 1 0 1

VII.

Analisa Flip flop adalah rangkaian logika yang merupakan gabungan dari gerbang logika yang memiliki variasi input dan mempunyai 2 input.

VIII.

Kesimpulan Jika kedua input SR flip flop dasar berada pada kondisi R=tinggi S=tinggi kemudian diset bersama-sama R=rendah S=tinggi maka akan terjadilah kondisi balapan.

Anda mungkin juga menyukai

- Register JKDokumen7 halamanRegister JKhadhiutomoBelum ada peringkat

- Laporan 13 Flip-Flop SC (NAND, NOR Dan ENABLE) Egi Baihaqi 1305869Dokumen17 halamanLaporan 13 Flip-Flop SC (NAND, NOR Dan ENABLE) Egi Baihaqi 1305869ptyreBelum ada peringkat

- LK 4. Format LKPD-1Dokumen6 halamanLK 4. Format LKPD-1Arys Jumaris0% (1)

- Adisti Nastiti 2NK Laporan Praktikum IIDokumen10 halamanAdisti Nastiti 2NK Laporan Praktikum IIADISTI NASTITIBelum ada peringkat

- Laporan Register Sipo (D-FF)Dokumen4 halamanLaporan Register Sipo (D-FF)Kurniawan SugandaBelum ada peringkat

- Laporan Praktikum Flip FlopDokumen8 halamanLaporan Praktikum Flip Flopasri andiBelum ada peringkat

- Muhammad Algi Algifari - Laporan Praktikum JK-FF - Elektronika Digital LanjutDokumen13 halamanMuhammad Algi Algifari - Laporan Praktikum JK-FF - Elektronika Digital LanjutMuhammad Algi AlgifariBelum ada peringkat

- Muhammad Algi Algifari - Laporan Praktikum JK-FF - Elektronika Digital LanjutDokumen14 halamanMuhammad Algi Algifari - Laporan Praktikum JK-FF - Elektronika Digital LanjutMuhammad Algi AlgifariBelum ada peringkat

- Acara 7 Laporan Praktikum ElektronikaDokumen16 halamanAcara 7 Laporan Praktikum ElektronikaCahaya HatiBelum ada peringkat

- E-10 - Modul 4 - Hazirin Safrian Utama - 119130072 - FandillaDimasPrayogaDokumen5 halamanE-10 - Modul 4 - Hazirin Safrian Utama - 119130072 - FandillaDimasPrayogaHazirin Safrian UtamaBelum ada peringkat

- RPP Flip FlopDokumen10 halamanRPP Flip FlopJimi DbonoBelum ada peringkat

- Laporan Register Sipo (JK-FF)Dokumen4 halamanLaporan Register Sipo (JK-FF)Kurniawan SugandaBelum ada peringkat

- Meity Damaria LRP Modul 4Dokumen7 halamanMeity Damaria LRP Modul 4Meity DamariaBelum ada peringkat

- Laporan Teknik Digital Flip-Flop RSDokumen5 halamanLaporan Teknik Digital Flip-Flop RSIrfan Dwi SetiadiBelum ada peringkat

- Laporan Praktikum Teknik Digital Tegangan Logika KerjaDokumen21 halamanLaporan Praktikum Teknik Digital Tegangan Logika Kerjapergendangen801Belum ada peringkat

- Modul PLC2 B 2019Dokumen23 halamanModul PLC2 B 2019Andrian DongiBelum ada peringkat

- Muhammad Algi Algifari - Laporan Praktikum JK-FF - Elektronika Digital LanjutDokumen13 halamanMuhammad Algi Algifari - Laporan Praktikum JK-FF - Elektronika Digital LanjutMuhammad Algi AlgifariBelum ada peringkat

- Laporan Praktikum2 (Tanpa NAND Dan NOR)Dokumen37 halamanLaporan Praktikum2 (Tanpa NAND Dan NOR)Sofiyan Arif KurniawanBelum ada peringkat

- Percobaan 1 Dan Percobaan 2 - Modul Praktikum Elektronika DigitalDokumen7 halamanPercobaan 1 Dan Percobaan 2 - Modul Praktikum Elektronika DigitalRobbialifianBelum ada peringkat

- RPP SMK ElindDokumen18 halamanRPP SMK ElindJimi DbonoBelum ada peringkat

- Analisa Berbagai IC MikroprosesorDokumen61 halamanAnalisa Berbagai IC Mikroprosesorilayyinan100% (2)

- Muhammad Algi Algifari - Laporan Praktikum D Flip-Flop - Elektronika Digital LanjutDokumen9 halamanMuhammad Algi Algifari - Laporan Praktikum D Flip-Flop - Elektronika Digital LanjutMuhammad Algi AlgifariBelum ada peringkat

- C1 - 1207070096 - Rajasabian Ardhi Awangga - UTS - Laporan3Dokumen16 halamanC1 - 1207070096 - Rajasabian Ardhi Awangga - UTS - Laporan3Lulu Sadiah LatikaBelum ada peringkat

- Muhammad Algi Algifari - Laporan Praktikum D Flip-Flop - Elektronika Digital LanjutDokumen9 halamanMuhammad Algi Algifari - Laporan Praktikum D Flip-Flop - Elektronika Digital LanjutMuhammad Algi AlgifariBelum ada peringkat

- 17 - Kel.06 - TT 2c - Clarissa Nadya ADokumen16 halaman17 - Kel.06 - TT 2c - Clarissa Nadya Aicang09Belum ada peringkat

- Laporan Rencana Praktikum Sistem DigitalDokumen7 halamanLaporan Rencana Praktikum Sistem DigitalAuriel Diya Ulhaque M.WBelum ada peringkat

- Rencana 4Dokumen7 halamanRencana 4Dian furnomoBelum ada peringkat

- Laporan Risky JK-FFDokumen19 halamanLaporan Risky JK-FFyesi sakina nababanBelum ada peringkat

- Jobsheet Praktik Digital 2019 FnlB2Dokumen28 halamanJobsheet Praktik Digital 2019 FnlB201XII TMK 2Abdullah Ni'amBelum ada peringkat

- Laprak Flip FlopDokumen19 halamanLaprak Flip Flopditajulianty490Belum ada peringkat

- Review Video 13 - 140310190034 - Florentia GabbyDokumen1 halamanReview Video 13 - 140310190034 - Florentia GabbyalikaBelum ada peringkat

- Dasar Flip FlopDokumen56 halamanDasar Flip FlopArizona AlvarestBelum ada peringkat

- Laporan Prak. Tek. Digital D Flip Flop-Kevin Perangin-Angin TK2BDokumen25 halamanLaporan Prak. Tek. Digital D Flip Flop-Kevin Perangin-Angin TK2BDwiky Khairi FahmiBelum ada peringkat

- Flip FlopDokumen14 halamanFlip FlopFahmi Prasetyo DelCadiz100% (1)

- Latihan Bismillah Io PLCDokumen3 halamanLatihan Bismillah Io PLCWendi MustafaBelum ada peringkat

- JobSheet 7 Gate EX - NORDokumen3 halamanJobSheet 7 Gate EX - NORCinta SetiawanBelum ada peringkat

- Dasar - Dasar Flip FlopDokumen59 halamanDasar - Dasar Flip Flopkharisma73Belum ada peringkat

- Modul 1 DigitalDokumen7 halamanModul 1 DigitalKamil MudabbirBelum ada peringkat

- Jobsheet Praktek Rangkaian Flip-Flop 4 LEDDokumen6 halamanJobsheet Praktek Rangkaian Flip-Flop 4 LEDEriansyah Raihan100% (1)

- Petunjuk Praktikum Rangkaian DigitalDokumen31 halamanPetunjuk Praktikum Rangkaian DigitalAinul YaqinBelum ada peringkat

- (TD) (NS) (7) Irfan FadliansyahDokumen20 halaman(TD) (NS) (7) Irfan FadliansyahIrsyad IrawanBelum ada peringkat

- Modul Perancangan Sinyal DigitalDokumen57 halamanModul Perancangan Sinyal Digitalyoga putraBelum ada peringkat

- Pak JK FFDokumen6 halamanPak JK FFFarr LastnightBelum ada peringkat

- Job Sheet PLC Forward ReverseDokumen3 halamanJob Sheet PLC Forward Reversehervina kiruna100% (1)

- Laporan Flip-FlopDokumen8 halamanLaporan Flip-FlopArdyzBelum ada peringkat

- SOALDokumen1 halamanSOALAhmad MusyafaBelum ada peringkat

- Muhammad Algi Algifari - Laporan Praktikum JK-FF - Elektronika Digital LanjutDokumen14 halamanMuhammad Algi Algifari - Laporan Praktikum JK-FF - Elektronika Digital LanjutMuhammad Algi AlgifariBelum ada peringkat

- SR FFDokumen4 halamanSR FFfaizroverBelum ada peringkat

- Modul Ajar RPP Rangkaian Flip FlopDokumen4 halamanModul Ajar RPP Rangkaian Flip FlopMufti Qoulan SyadidaBelum ada peringkat

- Modul Ajar RPP Rangkaian Flip FlopDokumen2 halamanModul Ajar RPP Rangkaian Flip FlopMufti Qoulan SyadidaBelum ada peringkat

- Devita Syifa 2A TTE - Laporan Praktikum D Flip Flop Dan ToggleDokumen24 halamanDevita Syifa 2A TTE - Laporan Praktikum D Flip Flop Dan Toggledevita.syifa.tkom22Belum ada peringkat

- Laporan Tina JK-FFDokumen19 halamanLaporan Tina JK-FFyesi sakina nababanBelum ada peringkat

- Laporan Register JK FFDokumen7 halamanLaporan Register JK FFPratiwi PutriyanBelum ada peringkat

- Counter UpDokumen6 halamanCounter UphadhiutomoBelum ada peringkat

- Counter UpDokumen6 halamanCounter UphadhiutomoBelum ada peringkat

- Counter UpDokumen6 halamanCounter UphadhiutomoBelum ada peringkat

- Counter DownDokumen6 halamanCounter DownhadhiutomoBelum ada peringkat

- JK FFDokumen5 halamanJK FFhadhiutomoBelum ada peringkat

- JK FFDokumen5 halamanJK FFhadhiutomoBelum ada peringkat

- Job Sheet 7 Gate Ex - NorDokumen3 halamanJob Sheet 7 Gate Ex - NorhadhiutomoBelum ada peringkat

- D FFDokumen5 halamanD FFhadhiutomoBelum ada peringkat

- Job Sheet 8 AdderDokumen6 halamanJob Sheet 8 AdderhadhiutomoBelum ada peringkat

- 6th Central Pay Commission Salary CalculatorDokumen15 halaman6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- 6th Central Pay Commission Salary CalculatorDokumen15 halaman6th Central Pay Commission Salary Calculatorrakhonde100% (436)

- Job Sheet 5 Gate Nor (Ic 7402)Dokumen8 halamanJob Sheet 5 Gate Nor (Ic 7402)hadhiutomoBelum ada peringkat

- Job Sheet 4 Gate Not (Ic 7404)Dokumen3 halamanJob Sheet 4 Gate Not (Ic 7404)hadhiutomoBelum ada peringkat

- Job Sheet 3 Gate Nand (Ic 7400)Dokumen7 halamanJob Sheet 3 Gate Nand (Ic 7400)hadhiutomoBelum ada peringkat

- Job Sheet 1 Gate and (Ic 7408)Dokumen9 halamanJob Sheet 1 Gate and (Ic 7408)hadhiutomoBelum ada peringkat

- Job Sheet 2 Gate or (Ic 7432)Dokumen10 halamanJob Sheet 2 Gate or (Ic 7432)hadhiutomoBelum ada peringkat