07 Cache Memory

Diunggah oleh

Syabani HarisHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

07 Cache Memory

Diunggah oleh

Syabani HarisHak Cipta:

Format Tersedia

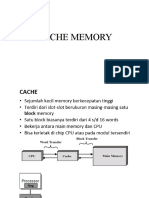

CACHE CACHE CACHE CACHE

MEMORY MEMORY

Tim Lab. SKJK

1

Hirarki Memori

Biaya per bit

ki h

Registers

makin murah

Kapasitas makin

besar

L1 Cache

besar

Waktu akses

makin lama

L2 Cache

Main memory (RAM)

makin lama

Frekuensi

diakses oleh

y ( )

Disk cache (pure S/W)

Disk (Harddisk)

d akses oleh

prosesor makin

jarang

Disk (Harddisk)

Optical (CD, DVD)

Magnetic tape

2

Magnetic tape

Cache Memory - Fungsi

Adalah fast memory yang berkapasitas kecil

Tujuan:

d k Memberikan memori yang mempunyai kecepatan mendekati

memori tercepat yang tersedia (register)

Memberikan memori semikonduktor dengan harga lebih murah

Untuk mengcopy sebagian isi main memory yang sering diakses

Terletak antara CPU dan main memori

l k di d l hi C di d l d l

3

Dapat terletak di dalam chip CPU atau di dalam modul

tersendiri

Cache Memory - Struktur

--Satu blok terdiri dari beberapa word

--Tag: Tag:

- Sbg identitas blok yang sedang

disimpan di cache memory

- Mrpk bagian dari alamat main memory

4

Cache Memory Operasi Baca data (1)

5

Cache Memory Operasi Baca data (2)

CPU mengeluarkan alamat data RA (Relative

Address) yang akan dibaca Address) yang akan dibaca

Periksa data di cache memory

Jik d t d di h di bil Jika data ada di cache memory diambil

(cache hit) cepat

Jika data tidak ada (cache miss) cari data

di main memory

Copy satu blok data ke cache memory

Berikan data yang diperlukan ke CPU

6

Berikan data yang diperlukan ke CPU

Cache Memory Operasi Baca data (3)

7

--Cache hit buffer di-disable, tdk perlu akses ke system bus

Elemen Perancangan Cache

Ukuran (Size) cache

Mapping Cache-Main memory

Direct

Associative

Set associative

Algoritma Penggantian (Replacement) Algoritma Penggantian (Replacement)

Least Recently Used (LRU)

First In First Out (FIFO)

Least Frequency Used (LFU)

R d Random

Cara penulisan (Write Policy)

Write through

Write back Write back

Ukuran blok (Block Size)

Jenis cache

Off-chip, On-chip

8

Single level, Multilevel

Unified, Split

Ukuran (size) cache

Mengapa ukuran cache kecil ?

Biaya: makin besar makin mahal Biaya: makin besar makin mahal

Makin besar makin banyak jumlah gerbang yang

digunakan untuk pengalamatan butuh waktu akses

f lebih lama performansi menurun

Area chip/board yang tersedia terbatas

M k h b b d b d ? Mengapa ukuran cache berbeda-beda ?

Untuk menyesuaikan dengan beban kerja komputer

Performansi cache sangat terpengaruh oleh beban kerja Performansi cache sangat terpengaruh oleh beban kerja

sistem (misal: beban Personal Computer berbeda

dengan beban mainframe)

9

Elemen Perancangan Cache

Ukuran (Size) cache

Mapping Cache-Main memory pp g y

Direct

Associative

Set associative

Algoritma Penggantian (Replacement) Algoritma Penggantian (Replacement)

Least Recently Used (LRU)

First In First Out (FIFO)

Least Frequency Used (LFU)

Random

Cara penulisan (Write Policy)

Write through

Write back Write back

Ukuran blok (Block Size)

Jenis cache

Off-chip, On-chip

10

Off chip, On chip

Single level, Multilevel

Unified, Split

Mapping Cache-Main memory

Mengapa perlu di-mapping ?

Kapasitas cache jauh lebih kecil daripada kapasitas j

main memory

(a) Direct Mapping

k bl k k d l t li Memetakan setiap blok memori ke dalam satu line

cache secara tetap (sesuai dengan nomor line)

(b) Associative Mapping (b) Associative Mapping

Memetakan setiap blok memori ke sembarang baris

cache (tidak terikat pada nomor line)

(c) Set Associative Mapping

Memetakan setiap blok memori ke dalam satu set

tertentu yang di dalamnya terdiri dari beberapa line

11

tertentu yang di dalamnya terdiri dari beberapa line

yang dapat digunakan secara bebas

Direct Mapping

Tiap blok di main memory dipetakan hanya ke satu baris/line

pada cache

Jika sebuah blok ada di cache, maka blok berada di satu tempat

yang spesifik

Panjang Alamat main memory dibagi menjadi 2 bagian j g y g j g

Least Significant Bit (w) mengidentifikasi suatu word yang unik

Most Significant Bit (s) mengidentifikasi sebuah blok memory.

Bit MSB dibagi menjadi Bit MSB dibagi menjadi

+ cache line field (r) : bit pengidentifikasi baris/line

+ tag (s-r) : bit pengidentifikasi blok pada memory

Tag (s-r) Line or Slot (r)

Word

(w)

12

(w)

Direct Mapping (1)

Rumus: i = j modulo m

i = nomor baris cache

j = nomor blok main memory j = nomor blok main memory

m = jumlah total baris di dalam cache

s = jumlah bit tag

Cache line Main Memory blocks

0 0, m, 2m, 3m2

s

-m

1 1 +1 2 +1 2

s

+1 1 1, m+1, 2m+12

s

-m+1

. .

. .

. .

m 1 m 1 2m 1 3m 1 2

s

1 m-1 m-1, 2m-1, 3m-12

s

-1

13

Direct Mapping - Baca data (1)

Memory Address

Length

1

2

4

1

2

3

exist

not exist

14

not exist

Direct Mapping - Baca data (2)

Cek apakah baris di cache valid (ada isinya)

Jika valid CPU membandingkan nomor tag

1

2

Jika valid CPU membandingkan nomor tag

yang akan dibaca dengan nomor tag yang

ada di cache

Bila nomor tag tsb sama (cache hit) pilih

word yang diinginkan yang terletak pada

3

word yang diinginkan yang terletak pada

nomor baris (line) yang diinginkan

Bila nomor tag tsb berbeda (cache mis)

4

Bila nomor tag tsb berbeda (cache mis)

ambil (fetch) satu blok data sesuai dengan

nomor tag dan line yang diinginkan

15

g y g g

Direct Mapping - Contoh (1)

Diketahui:

Main memory berukuran 16 MByte

C h b k 64 kB t Cache berukuran 64 kByte

1 byte = 1 alamat memory size

1x transfer data = 1 blok memori = 1 line cache = 4 byte = 4 alamat

S b k j l h bi k ( ) li ( ) d d ( ) ! a. Sebutkan jumlah bit untuk tag (s-r), line (r), dan word (w) !

b. Gambarkan mappingnya !

c. Berikan contohnya !

Maka:

Jumlah alamat total = 16 MByte/1 Byte = 16 M alamat

Memory 16 M alamat = 2

4

. 2

20

= 2

24

Jumlah bit alamat yang y y g

diperlukan = 24 bit (panjang alamat = s+w)

1 blok memori = 4 byte = 2

2

Jumlah bit identitas word (w) = 2 bit

Jumlah line cache = 64 kbyte/4 byte = 16 k line

16

Jumlah line cache = 64 kbyte/4 byte = 16 k line

16 k = 2

4

. 2

10

= 2

14

Jumlah bit line (r) = 14 bit

Jumlah bit tag (s-r) = 24 14 2 = 8 bit

Direct Mapping - Contoh (2)

Format alamat memori: (dari sisi cache)

Tag (s-r)

Line or Slot (r)

Word (w)

Jumlah blok memori = 16 Mbyte/4 byte = 4 M blok

g ( )

8-bit

L ( )

14-bit

Word (w)

2-bit

1 blok memori 1 line cache, maka:

line : blok = 16 K : 4 M = 2

4

2

10

: 2

2

2

20

= 1 : 2

8

=1 : 256

1 line cache kemungkinan ditempati oleh 256 data yang berbeda 1 line cache kemungkinan ditempati oleh 256 data yang berbeda

(nomor tag berbeda)

Jumlah tag = 2

8

= 256 tag

Setiap nomor blok memori hanya akan menempati satu

nomor line cache tertentu saja (tidak berpindah-pindah)

17

Direct Mapping - Contoh (3)

Cara mapping:

Line + word (16 bit): 3 3 9 C

(bl k i) 0011 0011 1001 1100 (blok memori) 0011 0011 1001 1100

Nomor line (14 bit): 00 1100 1110 0111

0 C E 7

Blok memori (16 bit): F F F 8

1111 1111 1111 1000

18

Nomor line (14 bit): 11 1111 1111 1110

3 F F E

Direct Mapping - Kelebihan/kekurangan

(+) Sederhana

(+) Mudah diimplementasikan (+) Mudah diimplementasikan

(+) Tidak mahal

(-) Lokasi mapping setiap blok sudah tertentu

(tidak fleksibel)

(-) Dapat terjadi thrashing bila program

mengakses 2 blok yang terletak pada line g y g p

cache yang sama secara berulang-ulang

terjadi proses swap memori berkali-kali

19

j p p

hit ratio menjadi rendah

Associative Mapping

Format alamat memori: (dari sisi cache)

T

Word

Tag

Word

(w)

Alamat memori diinterpretasikan sebagai tag dan

word

Tag merupakan identitas blok memori

Setiap satu baris cache mempunyai satu tag

Tag menjadi kata kunci dalam setiap pencarian data

20

Associative Mapping - Baca data (1)

1

2

3

1

3

exist

21

not exist

Associative Mapping - Baca data (2)

CPU membandingkan nomor tag yang akan

dibaca dengan semua nomor tag yang ada

1

dibaca dengan semua nomor tag yang ada

di cache secara bersamaan

h hi Bila nomor tag tsb ada di cache (cache hit)

pilih word yang diinginkan yang terletak

2

pada nomor tag yang diinginkan

Bila nomor tag tsb tidak ada di cache (cache

3

a o o tag tsb t da ada d cac e (cac e

miss) ambil (fetch) satu blok data sesuai

dengan nomor tag yang diinginkan

22

dengan nomor tag yang diinginkan

Associative Mapping - Contoh (1)

Diketahui:

Main memory berukuran 16 MByte

Cache berukuran 64 kByte

1 alamat = 1 byte

1x transfer data 1 blok memori 1 line cache 4 byte 1x transfer data = 1 blok memori = 1 line cache = 4 byte

Maka:

Memori 16 Mbyte = 2

4

2

20

= 2

24

Jumlah bit alamat yang Memori 16 Mbyte = 2

4

. 2

20

= 2

24

Jumlah bit alamat yang

diperlukan = 24 bit

Jumlah bit identitas word (w) = 2 bit (1 blok = 4 byte = 2

2

) ( ) ( y )

Jumlah bit tag = 24 2 = 22 bit

23

Associative Mapping - Contoh (2)

Format alamat memori: (dari sisi cache)

T (22 bi )

Word

22

Tag (22 bit)

Word

(2 bit)

Jumlah blok memori = 16 Mbyte/4 byte = 4 M blok = jumlah tag (2

22

)

1 line cache 1 blok memori (tag), maka:

1 line cache memiliki kemungkinan ditempati oleh 4 M data yang 1 line cache memiliki kemungkinan ditempati oleh 4 M data yang

berbeda

Setiap tag dapat menempati nomor line yang mana saja (tidak

berhubungan dengan nomor baris) be ubu ga de ga o o ba s)

Setiap blok memori mempunyai satu pasangan nomor tag

24

Associative Mapping - Contoh (3)

Cara mapping:

Alamat (24 bit): 1 6 3 3 9 C

0001 0110 0011 0011 1001 1100

Nomor tag (22 bit): 00 0101 1000 1100 1110 0111

0 5 8 C E 7

Berapa blok data yang dapat ditampung

di cache secara bersamaan ?

25

di cache secara bersamaan ?

Berapa kilo byte ?

Associative Mapping - Kelebihan/kekurangan

(+) Mapping setiap blok dapat dilakukan secara

fleksibel (tidak terikat pada nomor line fleksibel (tidak terikat pada nomor line

tertentu)

(+) Dapat mengatasi masalah thrashing (+) Dapat mengatasi masalah thrashing

(-) Diperlukan rangkaian yang lebih rumit

t k b di k t untuk membandingkan semua tag secara

paralel, karena jumlah tag sangat banyak

26

Set Associative Mapping (1)

Cache dibagi menjadi sejumlah set

Setiap set terdiri dari sejumlah baris Setiap set terdiri dari sejumlah baris

Setiap blok memori dipasangkan ke nomor

set tertentu tetapi boleh menempati baris set tertentu, tetapi boleh menempati baris

mana saja dalam satu set

Misal: jika tiap set terdiri dari 2 baris maka: Misal: jika tiap set terdiri dari 2 baris, maka:

Model pemetaannya disebut: 2-way associative

mapping pp g

Setiap blok memori boleh menempati satu dari

dua baris yang tersedia asalkan masih dalam

t t

27

satu set

Set Associative Mapping (2)

Format alamat memori: (dari sisi cache)

Untuk keperluan akses cache setiap alamat

Tag (s-v)

Set (v) Word (w)

Untuk keperluan akses cache setiap alamat

memori dibagi menjadi 2 bagian:

w = bit-bit identitas word atau byte di dalam blok memori y

s = bit-bit identitas blok memori

set field (v): bit-bit nomor set

tag (s-v): bit-bit identitas blok data yang ada di memori tag (s-v): bit-bit identitas blok data yang ada di memori

28

Set Associative Mapping - Baca data (1)

1

3

2

3

exist

29

not exist

Set Associative Mapping - Baca data (2)

CPU membandingkan nomor tag yang akan

dibaca dengan semua nomor tag di cache.

1

g g

Tag dalam satu set dibandingkan bersama-

sama

Bila nomor tag tsb ada di cache (cache hit)

pilih word yang diinginkan yang terletak

2

pada nomor set yang diinginkan

Bila nomor tag tsb tidak ada di cache (cache

3

g (

miss) ambil (fetch) satu blok data sesuai

dengan nomor tag dan nomor set yang

30

g g y g

diinginkan

Set Associative Mapping - Contoh (1)

Diketahui:

Main memory berukuran 16 MByte

Cache berukuran 64 kByte Cache berukuran 64 kByte

1 alamat = 1 byte

1x transfer data = 1 blok memori = 4 byte

2 way assosiative 2-way assosiative

Maka:

Memory 16 Mbyte = 2

4

. 2

20

= 2

24

Jumlah bit alamat = 24 bit

Jumlah bit identitas word (w) = 2 bit (1 blok = 4 byte = 2

2

)

Jumlah line cache = 64 kbyte/4 byte = 16 k line

1 set = 2 line jumlah set = 16k/2 = 8 k set 1 set 2 line jumlah set 16k/2 8 k set

8 k = 2

3

. 2

10

= 2

13

Jumlah bit set = 13 bit (0000 - 1FFF)

Jumlah bit tag = 24 13 2 = 9 bit (range: 000 1FF)

31

Jumlah tag = 2

9

= 512 tag

Set Associative Mapping - Contoh (2)

Format alamat memori: (dari sisi cache)

Tag (s-v)

Set (v)

Word (w)

Jumlah alamat memori/tag = 2

13+2

= 2

5

. 2

10

= 32 k

(9 bit)

(13 bit) (2 bit)

/ g

Range alamat memori/tag (24 bit) = 000000 007FFF

alamat memori : 000000, 008000, 010000, , FF8000

selalu terletak pada set nomor yang sama (0000) selalu terletak pada set nomor yang sama (0000)

Setiap alamat memori di atas bebas menempati salah satu

line pada nomor set tersebut

Setiap satu nomor blok memori hanya dapat menempati satu

nomor set

Satu nomor set dapat dapat ditempati oleh:

32

Satu nomor set dapat dapat ditempati oleh:

512 nomor tag berbeda tetapi nomor blok-nya sama

Set Associative Mapping - Contoh (3)

Cara mapping:

Set+word (15 bit): 3 3 9 C

011 0011 1001 1100

Nomor set (13 bit): 0 1100 1110 0111

0 C E 7

33

Set Associative Mapping - Kelebihan

(+) Setiap blok memori dapat menempati lebih

dari satu kemungkinan nomor line (dapat dari satu kemungkinan nomor line (dapat

menggunakan line yang kosong), sehingga

thrashing dapat diperkecil thrashing dapat diperkecil

(+) Jumlah tag lebih sedikit (dibanding model

i ti ) hi jalur t k associative), sehingga jalur untuk

melakukan perbandingan tag lebih

sederhana

34

Elemen Perancangan Cache

Ukuran (Size) cache

Mapping Cache-Main memory

Direct

Associative

Set associative

Algoritma Penggantian (Replacement)

Least Recently Used (LRU)

First In First Out (FIFO)

Least Frequency Used (LFU)

R d

g gg ( p )

Random

Cara penulisan (Write Policy)

Write through

Write back Write back

Ukuran blok (Block Size)

Jumlah cache

Off-chip, On-chip

35

Single level, Multilevel

Unified, Split

Replacement Algorithms (1)

Adalah algoritma yang digunakan untuk memilih

blok data mana yang ada di cache yang dapat y g y g p

diganti dengan blok data baru

Direct mapping

Tidak perlu algoritma

Mapping pasti (tidak ada alternatif lain)

Associative & Set Associative

Algoritma diimplementasi dengan H/W (supaya cepat)

J i l i Jenis algoritma:

Least Recently used (LRU)

First in first out (FIFO)

36

( )

Least frequently used (LFU)

Random

Replacement Algorithms (2)

Least Recently Used (LRU)

Blok yang diganti adalah blok yang paling lama di cache dan tidak

digunakan

Kelebihan:

Paling efektif

Mempunyai hit ratio tinggi data yang sering digunakan saja yang

ditaruh di cache ditaruh di cache

Paling mudah diimplementasikan pada two-way set associative

mapping

Contoh:

K it h h 4 b i d k j l h bl k d t j h l bih Kapasitas cache hanya 4 baris sedangkan jumlah blok data jauh lebih

banyak. Jika urutan pengaksesan data adalah:

a b c d c b a b c kemudian datang data e maka data yang

diganti adalah ??? diganti adalah ???

Jawaban: d

Kalau data yang diakses sebelum data e adalah d, maka data yang

diganti adalah ???

37

Jawaban: a (a lebih lama tidak diakses dibanding d)

Replacement Algorithms (3)

First In First Out (FIFO)

Blok yang diganti adalah blok yang paling awal berada di

h cache

Contoh:

Kapasitas cache hanya 4 baris sedangkan jumlah blok Kapasitas cache hanya 4 baris sedangkan jumlah blok

data jauh lebih banyak. Jika urutan pengaksesan data

adalah:

a b c d c b a b c k di d t d t e k a b c d c b a b c kemudian datang data e maka

data yang diganti adalah ???

Jawaban: a (a paling lama/awal berada di cache) Jawaban: a (a paling lama/awal berada di cache)

Kalau data yang diakses sebelum data e adalah d,

maka data yang diganti adalah ???

38

y g g

Jawaban: a (a paling lama/awal berada di cache)

Replacement Algorithms (4)

Least Frequently Used (LFU)

Blok yang paling jarang digunakan yang diganti

Setiap baris mempunyai counter p p y

Contoh:

Kapasitas cache hanya 4 baris sedangkan jumlah blok data jauh lebih

banyak. Jika urutan pengaksesan data adalah:

b d b b d a b c d c b a b c a d kemudian datang data e maka data yang diganti

adalah ???

Jawaban: d (d paling jarang diakses)

Kalau urutan data yang diakses sebelum data e adalah a b c d c b a b c

a d d, maka data yang diganti adalah ???

Jawaban: a (nilai counter a sama dengan yang lain, tetapi karena a

datang paling awal maka a berada pada baris paling awal) FIFO

b (paling lama tidak diakses) LRU

Random

39

Penggantian blok dilakukan secara acak

Elemen Perancangan Cache

Ukuran (Size) cache

Mapping Cache-Main memory

Direct

Associative

Set associative

Algoritma Penggantian (Replacement)

Least Recently Used (LRU) Least Recently Used (LRU)

First In First Out (FIFO)

Least Frequency Used (LFU)

Random

Write through

Write back

Cara penulisan (Write Policy)

Write back

Ukuran blok (Block Size)

Jenis cache

Off-chip, On-chip

40

Single level, Multilevel

Unified, Split

Write Policy (1)

Bertujuan untuk memastikan apakah blok di

cache yang akan diganti telah di-copy di cache yang akan diganti telah di copy di

memori

Problem 1: bagaimana jika main memory Problem 1: bagaimana jika main memory

dapat diakses oleh lebih dari satu device

tanpa melalui cache (misal dengan DMA) tanpa melalui cache (misal dengan DMA)

Solusi:

( ) h h (a) Write through

(b) Write back

41

Write Policy (2)

(a) Write through

Setiap ada perubahan data di cache selalu di-copy di

i d iki l b lik memori, demikian pula sebaliknya

Kelebihan/kekurangan:

(+) Teknik paling sederhana

( ) M b bk t ffi ti i ( h i ) () Menyebabkan memory traffic tinggi (cache main memory)

() Dapat terjadi bottleneck (bus data penuh)

(b) Write back

Update data hanya dilakukan di cache

Jika baris di cache akan ditempati data lain data lama di-

copy ke memori hanya jika data tsb mengalami perubahan

Kelebihan/kekurangan:

(+) Memory traffic berkurang

() Data di memori tidak valid akses I/O ke memori harus melalui

cache

42

cache

() Circuitry lebih kompleks

() Dapat terjadi bottleneck

Write Policy (3)

Problem 2: bagaimana jika terdapat lebih dari

satu prosesor dan masing-masing mempunyai satu prosesor dan masing masing mempunyai

cache tersediri ?

Solusi: Solusi:

Cache saling berhubungan (cache coherency)

Macam cache coherency: Macam cache coherency:

(a) Bus watching with write through

(b) H/W transparency ( ) / p y

(c) Non cacheable memory

43

Write Policy (4)

(a) Bus watching with write through

Setiap cache controller memonitor baris alamat untuk p

mengetahui apakah ada device lain yang menulis ke

memori

(b) H/W t (b) H/W transparency

Digunakan H/W tambahan untuk menjamin perubahan

data di memori selalu melalui cache dan di-copy-kan ke data di memori selalu melalui cache dan di copy kan ke

cache-cache yang lain

(c) Non cacheable memory ( ) y

Sebagian dari main memory di-sharing oleh beberapa

prosesor

D t d h d tid k di k k h

44

Data pada shared memory tidak di-copy-kan ke cache

selalu terjadi cache miss

Elemen Perancangan Cache

Ukuran (Size) cache

Mapping Cache-Main memory

Direct

Associative

Set associative

Algoritma Penggantian (Replacement)

Least Recently Used (LRU) Least Recently Used (LRU)

First In First Out (FIFO)

Least Frequency Used (LFU)

Random

Cara penulisan (Write Policy)

Write through

Write back

Uk bl k (Bl k Si )

Jenis cache

Off-chip, On-chip

Ukuran blok (Block Size)

45

Single level, Multilevel

Unified, Split

Ukuran Blok Memori

Ukuran blok memori:

Makin besar cache hit makin besar Makin besar cache hit makin besar

(efek locality : bila suatu word ada di suatu

blok, maka ada kemungkinan word-word lain

yang terdapat di dalam blok tersebut juga akan

digunakan)

Terlalu besar cache hit menurun Terlalu besar cache hit menurun

(jumlah blok yang dapat di-copy ke cache

makin sedikit) makin sedikit)

Ukuran optimum: 8 32 byte

46

Elemen Perancangan Cache

Ukuran (Size) cache

Mapping Cache-Main memory

Direct

Associative

Set associative

Algoritma Penggantian (Replacement)

Least Recently Used (LRU) Least Recently Used (LRU)

First In First Out (FIFO)

Least Frequency Used (LFU)

Random

Cara penulisan (Write Policy)

Write through

Write back

Ukuran blok (Block Size) Ukuran blok (Block Size)

Off-chip, On-chip

Jenis cache

47

Off chip, On chip

Single level, Multilevel

Unified, Split

Jenis cache (1)

Jenis cache memory:

Berdasarkan letaknya:

off-chip cache (eksternal)

on-chip cache (internal)

Berdasarkan levelnya: y

one level cache

multilevel cache (L1, L2, L3)

Berdasarkan jenis data yang disimpan: Berdasarkan jenis data yang disimpan:

unified cache

split cache

(a) Off-chip cache (eksternal)

Terpisah dari chip prosesor

48

Terpisah dari chip prosesor

Komunikasi melalui bus eksternal atau bus khusus

Jenis cache (2)

(b) On-chip cache (internal)

Menjadi satu dengan chip prosesor Menjadi satu dengan chip prosesor

(+) Waktu eksekusi lebih cepat performansi

sistem meningkat sistem meningkat

(+) Aktifitas bus eksternal berkurang dapat

digunakan untuk keperluan lain digunakan untuk keperluan lain

(c) One-level cache

d l l h ( d h Hanya ada satu level cache (sudah

ditinggalkan)

(d) M l il l h

49

(d) Multilevel cache

Terdiri dari 2 level cache atau lebih

Jenis cache (3)

Mengapa perlu 2 level atau lebih ???

Cache miss CPU akses ke memori, kecepatan , p

memori <<< kecepatan CPU performansi turun

Dengan L2 (SRAM) mempercepat tersedianya

data yang dibutuhkan CPU

Design L2 cache:

Cache eksternal (dengan bus khusus)

Cache internal (satu chip dengan prosesor)

K l bih /k k ltil l h Kelebihan/kekurangan multilevel cache:

(+) Memperbaiki performansi

( ) Perancangan cache lebih rumit (ukuran algoritma

50

(-) Perancangan cache lebih rumit (ukuran, algoritma,

write policy, dll)

Jenis cache (5)

(e) Split cache (Pentium, Power PC)

Cache dibagi 2 sehingga data dan instruksi Cache dibagi 2 sehingga data dan instruksi

disimpan pada tempat terpisah

Kelebihan: Kelebihan:

(+) Mendukung eksekusi instruksi secara paralel

(+) Mencegah contention cache antara fetch/decode ( ) g

instruksi dan eksekusi instruksi performansi lebih

baik

51

Jenis cache (4)

(f) Unified cache

Data dan instruksi disimpan pada tempat yang Data dan instruksi disimpan pada tempat yang

sama (dalam satu cache)

Kelebihan/kekurangan: Kelebihan/kekurangan:

(+) Hit rate lebih tinggi daripada split cache

(+) Perancangan dan implementasi terfokus pada satu ( ) g p p

cache

(-) Tidak mendukung pipeline

( ) D j di i ( b ) h (-) Dapat terjadi contention (rebutan) cache

52

Cache Intel

80386 tanpa cache

80486:

Single on-chip Single on chip

Ukuran 8 Kbyte

Ukuran line 16 byte

Four way set associative Four way set associative

Pentium (semua versi) 2 buah on chip cache L1

Untuk data dan instruksi

Pentium 4 Pentium 4

L1 caches:

Ukuran 8 Kbyte

Ukuran line 64 byte

Four way set associative

L2 cache

Feeding both L1 caches

Ukuran 256 Kbyte

53

Ukuran 256 Kbyte

Ukuran line 128 byte

8 way set associative

Blok Diagram Pentium 4 (Simplified)

54

Bagian Utama Prosesor Pentium 4 (1)

Fetch/Decode Unit

Mengambil instruksi dari cache L2

Men-decode instruksi menjadi mikro operasi

Menyimpan hasilnya (mikro operasi) di cache instruksi L1

Out of order execution logic Out of order execution logic

Membuat jadual eksekusi mikro operasi sesuai dengan

data dan resource yang tersedia

Membuat jadual eksekusi mikro yang mungkin akan

digunakan (spekulasi)

Execution units Execution units

Mengeksekusi mikro operasi

Mengambil data yang diperlukan dari cache L1

55

g y g p

Menyimpan hasil pemrosesan ke register

Bagian Utama Prosesor Pentium 4 (2)

Memory subsystem

Terdiri dari cache L2 dan sistem bus Terdiri dari cache L2 dan sistem bus

Untuk mengakses main memory jika terjadi

cache miss cache miss

Untuk mengakses resource I/O

56

Organisasi Cache Power PC

601 single 32 Kbyte, 8 way set associative

603 16 Kb (2 x 8 Kb) two way set associative 603 16 Kb (2 x 8 Kb) two way set associative

604 32 Kbyte

610 64 Kbyte 610 64 Kbyte

G3 & G4

L1 cache: L1 cache:

64 Kbyte

8 way set associative 8 way set associative

L2 cache

256 Kbyte, 512k atau 1M

57

two way set associative

Blok Diagram Power PC G4

58

Perbandingan Ukuran Cache

59

Anda mungkin juga menyukai

- COA 15 Cache MemoryDokumen59 halamanCOA 15 Cache MemoryArif RamadhaniBelum ada peringkat

- COA 15 Cache MemoryDokumen59 halamanCOA 15 Cache MemorysyamsulbachriBelum ada peringkat

- COA 2019 Pertemuan 6 Memory Pemetaan CacheDokumen33 halamanCOA 2019 Pertemuan 6 Memory Pemetaan CacheNabila SumarnoBelum ada peringkat

- Chapter 5 - Cache MemoryDokumen55 halamanChapter 5 - Cache MemoryErdina Lumban GaolBelum ada peringkat

- Cache MemoryDokumen17 halamanCache MemoryFahrul MokoagowBelum ada peringkat

- Pertemuan 5 Memory-InternalDokumen48 halamanPertemuan 5 Memory-InternalRosyid RidloBelum ada peringkat

- Pert 05 Ch02 Seputar Perangkat Keras Komputer Performansi Dev Khusus Vonnewmann 20100928Dokumen87 halamanPert 05 Ch02 Seputar Perangkat Keras Komputer Performansi Dev Khusus Vonnewmann 20100928Lukman HadiyatullohBelum ada peringkat

- Materi Pertemuan 5 - Cache Memory Part 2Dokumen9 halamanMateri Pertemuan 5 - Cache Memory Part 2Dewi LestariBelum ada peringkat

- Mapping ArkomDokumen32 halamanMapping ArkomFuad SuyudiBelum ada peringkat

- Kelompok 2 ArkomDokumen18 halamanKelompok 2 Arkomwahyu suhendriBelum ada peringkat

- Jawaban Soal 2008, 2009, 2010 Cache MemoryDokumen15 halamanJawaban Soal 2008, 2009, 2010 Cache Memoryyufa.yulia.fatmaBelum ada peringkat

- Materi Pertemuan 7Dokumen27 halamanMateri Pertemuan 7Alinda SahraniBelum ada peringkat

- Cache MemoryDokumen29 halamanCache Memorysimilekete100% (1)

- Week 4 PDFDokumen46 halamanWeek 4 PDFSyahdan NugrohoBelum ada peringkat

- 4 Memori CacheDokumen50 halaman4 Memori CachezhachestBelum ada peringkat

- Andhika Mapparewa - F1D019005 - Tugas Orarkom A - Chace MemoryDokumen15 halamanAndhika Mapparewa - F1D019005 - Tugas Orarkom A - Chace MemoryAndhikaBelum ada peringkat

- Cache MemoryDokumen29 halamanCache MemoryAnita RahmawatiBelum ada peringkat

- Penghitungan Cache MemoryDokumen42 halamanPenghitungan Cache MemoryIsnant B Faried0% (1)

- J3D117089 - Kevin Wellisz Simngunsong (Tek A1)Dokumen12 halamanJ3D117089 - Kevin Wellisz Simngunsong (Tek A1)KevinWellisSimangunsongBelum ada peringkat

- 05-3 Cache - MemoryDokumen32 halaman05-3 Cache - MemoryWahyu Syarif100% (1)

- Chapter 8 Sistem KomputerDokumen39 halamanChapter 8 Sistem KomputerCynthia Suci RachmanBelum ada peringkat

- Tugas Arkom - PipelineDokumen41 halamanTugas Arkom - PipelineNofitri HeriyaniBelum ada peringkat

- Contoh Soal UTSDokumen3 halamanContoh Soal UTSM FauzzanzBelum ada peringkat

- Tugas 5 OrkomDokumen8 halamanTugas 5 OrkomKelvinBelum ada peringkat

- Bila CPU Mengakses Memori UtamaDokumen8 halamanBila CPU Mengakses Memori Utamastiafdial malikBelum ada peringkat

- 10.pengalamatan LangsungDokumen19 halaman10.pengalamatan LangsungpeterBelum ada peringkat

- Memori 1Dokumen19 halamanMemori 1Hacking_DefaceBelum ada peringkat

- Dasar MikroprosesorDokumen16 halamanDasar MikroprosesorJoseph AnthonyBelum ada peringkat

- Soal Bab 12Dokumen9 halamanSoal Bab 12UisBelum ada peringkat

- Cache MemoryDokumen40 halamanCache MemoryYeshee SBelum ada peringkat

- Tugas COA Week 6Dokumen5 halamanTugas COA Week 6Luhung FdBelum ada peringkat

- Makalah Kelompok Orkom Cache MemoryDokumen11 halamanMakalah Kelompok Orkom Cache MemoryRivon KurniawanBelum ada peringkat

- Kuliah 9 Organisasi Dan Arsitektur KomputerDokumen4 halamanKuliah 9 Organisasi Dan Arsitektur KomputerSurahman SalehBelum ada peringkat

- Organisasi Komputer Minggu 6Dokumen49 halamanOrganisasi Komputer Minggu 6Sulistyawan Abdilah RosyidBelum ada peringkat

- Solusi Quiz 2 COA 20120522 PDFDokumen6 halamanSolusi Quiz 2 COA 20120522 PDFYunita YesiBelum ada peringkat

- Tugas Elka Digital - MEMORY - 1D3 - Elin-B - 2021Dokumen27 halamanTugas Elka Digital - MEMORY - 1D3 - Elin-B - 2021Nurul Aini ApriliyantiBelum ada peringkat

- Pertemuan Ke - 9 Memori: Politeknik Elektronika Negeri SurabayaDokumen45 halamanPertemuan Ke - 9 Memori: Politeknik Elektronika Negeri SurabayaNanius MuribBelum ada peringkat

- Tugas 4 Roihanuddin (Direct Mapping)Dokumen5 halamanTugas 4 Roihanuddin (Direct Mapping)M Barku M BarkuBelum ada peringkat

- Pertemuan 11Dokumen30 halamanPertemuan 11Tenma YatoBelum ada peringkat

- Bab7 MemoryDokumen32 halamanBab7 MemoryNanang SofiyullahBelum ada peringkat

- Perbedaan Processor 32 Bit Dan 64-Bit (TUGAS 1)Dokumen5 halamanPerbedaan Processor 32 Bit Dan 64-Bit (TUGAS 1)Ahmad X-plorerBelum ada peringkat

- Algoritma ReplacementDokumen2 halamanAlgoritma ReplacementchristianBelum ada peringkat

- MINGGU 9 Memori InternalDokumen49 halamanMINGGU 9 Memori InternalSoliq WahyuBelum ada peringkat

- 04 Memori CacheDokumen58 halaman04 Memori CacheRendra NeutronBelum ada peringkat

- Tugas Kuliah Organisasi Komputer: Presentasi Associative MappingDokumen14 halamanTugas Kuliah Organisasi Komputer: Presentasi Associative MappingFX. Eko Budi Kristanto50% (2)

- Antarmuka MemoriDokumen59 halamanAntarmuka MemoriArifFadilahBelum ada peringkat

- Kapasitas PenyimpananDokumen9 halamanKapasitas PenyimpananHasanBelum ada peringkat

- Bab XDokumen10 halamanBab XNovra Edi PratamaBelum ada peringkat

- Bus Alamat: MikroprosesorDokumen42 halamanBus Alamat: MikroprosesorBuana Suhurdin PutraBelum ada peringkat

- Memory InternalDokumen59 halamanMemory InternalInggrid Ayu PutriBelum ada peringkat

- Perc8 MemoryDokumen7 halamanPerc8 MemoryDwi SetiantoBelum ada peringkat

- Coa 5Dokumen62 halamanCoa 5kevinBelum ada peringkat

- Pakta IntegritasDokumen4 halamanPakta IntegritasZukhruf Faridho100% (1)

- Syarat KuliahDokumen2 halamanSyarat KuliahDinoBelum ada peringkat

- Chapter 12 Teknik KompresiDokumen30 halamanChapter 12 Teknik KompresiUnii ChaerunisaiBelum ada peringkat

- Pertemuan 1-6 MikroDokumen8 halamanPertemuan 1-6 Mikroqmouse89Belum ada peringkat

- Translate Orakom Halaman 163-166Dokumen5 halamanTranslate Orakom Halaman 163-166Johnny RpdtlBelum ada peringkat

- Rangkaian MemoryDokumen3 halamanRangkaian MemorymajidBelum ada peringkat

- Memory: MateriDokumen32 halamanMemory: MateriArfstywnBelum ada peringkat

- KhutbahDokumen3 halamanKhutbahSyabani HarisBelum ada peringkat

- TekmekDokumen231 halamanTekmekSyabani HarisBelum ada peringkat

- Payback Period Dan Teman - Temannya.Dokumen10 halamanPayback Period Dan Teman - Temannya.chintyawidyaBelum ada peringkat

- XSWDFDSFDokumen12 halamanXSWDFDSFSyabani HarisBelum ada peringkat

- Candi BorobudurDokumen8 halamanCandi BorobudurSyabani HarisBelum ada peringkat

- TTL1 1Dokumen47 halamanTTL1 1Hafid FajriBelum ada peringkat

- Motor PenggerakDokumen32 halamanMotor PenggerakSyabani HarisBelum ada peringkat

- 03 Transmisi TNG Jilid 1 Bab 2 Pengukuran ListrikDokumen48 halaman03 Transmisi TNG Jilid 1 Bab 2 Pengukuran ListrikEdi Hariyanto100% (1)

- UTS Sistem Kendali Adaktif 2014Dokumen1 halamanUTS Sistem Kendali Adaktif 2014Syabani HarisBelum ada peringkat

- Design of Model Reference Adaptive Control For Non Linear PlantDokumen12 halamanDesign of Model Reference Adaptive Control For Non Linear PlantAris JanuarBelum ada peringkat

- DC MachinesDokumen51 halamanDC MachinesSyabani HarisBelum ada peringkat

- Pengukuran Besaran Listrik Jembatan Arus Bolak Balik2Dokumen18 halamanPengukuran Besaran Listrik Jembatan Arus Bolak Balik2Orivha Sitohang100% (1)

- 20 Sukarman225 229Dokumen6 halaman20 Sukarman225 229cintekBelum ada peringkat

- Pengukuran Besaran Listrik Jembatan Arus Bolak Balik2Dokumen18 halamanPengukuran Besaran Listrik Jembatan Arus Bolak Balik2Orivha Sitohang100% (1)

- Sistem Kendali Servo Posisi Dan Kecepatan Dengan ProgrammablDokumen86 halamanSistem Kendali Servo Posisi Dan Kecepatan Dengan ProgrammablSyamsumardi Gusti0% (1)

- MIMODokumen10 halamanMIMOaqcindhiBelum ada peringkat

- TE 12 BackproDokumen7 halamanTE 12 BackproSyabani HarisBelum ada peringkat

- 2 Resonansi ListrikDokumen26 halaman2 Resonansi ListrikKhoirul FahmiBelum ada peringkat

- Bab I Dasar Sinyal AudioDokumen48 halamanBab I Dasar Sinyal Audio3riBelum ada peringkat

- Chapter IIDokumen28 halamanChapter IISyabani HarisBelum ada peringkat

- Konsep Dasar1Dokumen13 halamanKonsep Dasar1Syabani HarisBelum ada peringkat

- Lowongan AsistenDokumen1 halamanLowongan AsistenSyabani HarisBelum ada peringkat

- F Permenlh 03 2010 Baku Mutu Air Limbah Kawasan IndustriDokumen7 halamanF Permenlh 03 2010 Baku Mutu Air Limbah Kawasan Industriapi-243366401Belum ada peringkat

- Fullpaper42 Silvia RamadhinaDokumen5 halamanFullpaper42 Silvia RamadhinaSyabani HarisBelum ada peringkat

- MDokumen5 halamanMSyabani HarisBelum ada peringkat

- Rangkaian Dasar TransistorDokumen13 halamanRangkaian Dasar TransistorNiluhAyu OktavianiBelum ada peringkat

- Felix Handoko TrigonometriDokumen10 halamanFelix Handoko TrigonometriSyabani HarisBelum ada peringkat

- MDokumen5 halamanMSyabani HarisBelum ada peringkat

- Bab I (Digital 4)Dokumen7 halamanBab I (Digital 4)Syabani HarisBelum ada peringkat