Pengenalan Programing Menggunakan Xilink

Diunggah oleh

Rifqi AnshariJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Pengenalan Programing Menggunakan Xilink

Diunggah oleh

Rifqi AnshariHak Cipta:

Format Tersedia

Page |1

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

PENGENALAN

PEMROGRAMAN FPGA:

XILINX SPARTAN-3E

(VHDL)

Oleh: Dahnial Syauqy

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

Page |2

1. Pendahuluan

Dalam tutorial ini akan diperkenalkan pemrograman FPGA untuk Xilinx Spartan-3E. Secara

garis besar isi tutorial ini meliputi:

- Mendesain sistem digital sederhana dan menuliskan program VHDL

- Mengkonfigurasikan board FPGA dan mengkoneksikan input output yang diperlukan

- Mendownload program ke board FPGA dengan iMPACT

- Melakukan simulasi program melalui simulator Isim

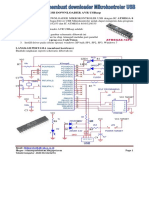

1.1 Perlengkapan Hardware

Spartan-3E Kit yang berisi development board, kabel power dan kabel koneksi USB dengan

PC.

1.2 Perlengkapan Software

Software yang digunakan adalah XILINX ISE project Navigator versi 13.4.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Page |3

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

2. Desain sistem

Desain yang digunakan pada tutorial ini adalah berupa logika kombinasional antara beberapa

input dan output. Output berupa 2 buah LED akan menyala tergantung kepada kondisi

beberapa switch dan push button pada board FPGA.

Kondisi 1:

LED 0 ON ketika Switch0 ON DAN Switch1 OFF, yang dapat dituliskan:

(1)

Tabel kebenaran LED0:

Switch0

0

0

1

1

Switch1

0

1

0

1

LED0

0

0

1

0

Dan kondisi 2:

LED 1 ON ketika (Switch2 ATAU Switch3 ON) DAN PushButton ON, yang dapat

dituliskan:

.. (2)

Tabel kebenaran LED1:

Switch2

0

0

0

0

1

1

1

1

Switch3

0

0

1

1

0

0

1

1

Push Button

0

1

0

1

0

1

0

1

LED1

0

0

0

1

0

1

0

1

3. Prosedur

3.1 Implementasi desain

3.1.1 Membuat project baru

1. Buka software ISE project manager

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

Page |4

2. Buat project baru melalui File>>New project. Dari sini, akan muncul New project wizard

3. Di kolom Name, isi dengan nama project (bebas). Pada contoh di bawah ini, nama project

adalah tutorial. Pilih Location dan Working Directory untuk menyimpan project. Terakhir,

pastikan top-level source type terpilih HDL, lalu klik next.

4. Pada evaluation development board, pilih Spartan-3E Starter Board. Pilih preferred

language menjadi VHDL serta pastikan semua opsi seperti dalam Gambar di bawah ini dan

klik next.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

Page |5

5. Berikutnya akan muncul Project Summary dengan tampilan sebagai berikut untuk

melakukan verifikasi konfigurasi yang telah dibuat sebelumnya. Setelah memastikan semua

benar, klik finish dan project akan dibuat.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

Page |6

3.1.2 Menambahkan kode VHDL

1. Setelah project kosong dibuat, selanjutnya perlu ditambahkan Source untuk menuliskan

kode VHDL. Pilih Project>>New source

2. Pilih source type VHDL module, isi file name (bebas, usahakan berbeda dengan nama

project), pilih lokasi penyimpanan, pastikan add to project tercentang, lalu klik next.

3. Berikutnya, dilakukan pendefinisian port input dan output desain yang akan dibuat.

Pertama beri nama entity pada kolom entity name (bebas). Selanjutnya:

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

Page |7

- Definisikan empat buah switch dengan nama berbeda (tanpa spasi), dan

mengkonfigurasikannya menjadi input. Masing-masing definisi switch diartikan sebagai port

input 1 bit.

- Definisikan satu buah push button dengan nama tanpa spasi dan konfigurasikan sebagai

input 1 bit.

- Definisikan dua buah LEDs yang dipasang secara bus (identik seperti array) dan bertindak

sebagai output. Centang bus dan isi MSB = 1, LSB = 0. Hal ini berarti sebuah port LEDs

adalah berupa port output 2 bit yang dapat diakses dengan LEDs(0) dan LEDs(1).

NOTE: Jika misalkan MSB (Most Significant Bit) bernilai 7, maka akan ada multiple output

dengan nama LEDs yang dapat diakses mulai LEDs(0) sampai LEDs(7) dengan total 8 bit (1

byte)

4. Setelah klik next, akan ditunjukkan Summary page.

Selanjutnya, klik finish dan source akan di-generate.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

Page |8

5. Pada Hierarchy, dobel klik top-behavioral (top.vhd) maka source code akan dibuka di tab

top.vhd. perhatikan bahwa pada entity top telah didefinisikan beberapa port input dan

output. Bagian entity mendefinisikan seluruh input dan output pada blok hardware. Pada

tahap selanjutnya perilaku input-output akan didefinisikan di architecture behavioral.

Bagian architecture mendefinisikan kode yang akan diimplementasikan ke dalam hardware.

Pada saat inisialisasi bagian tersebut kosong sehingga kode program perlu ditambahkan di

antara begin dan end di bagian architecture.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

Page |9

3.1.3 Mengedit source code VHDL

1. Masukkan kode VHDL desain yang akan dibuat pada blok architecture di bagian antara

begin dan end. Kode ini merepresentasi fungsi sistem yang didesain pada langkah awal.

2. Save file melalui File>>Save

3. Berikutnya adalah melakukan checking sytax VHDL yang telah dibuat. Pertama, pastikan

tab implementation terpilih. Klik tanda + pada Synthesize-XST. Terakhir, lakukan dobel klik

pada Check Syntax dan tunggu proses checking berlangsung.

Jika pada checking tidak ditemukan kesalahan maka akan muncul tanda centang berwarna

hijau di sebelah check syntax. Sebaliknya, jika ada kesalahan akan muncul pesan error di

console window yang akan membantu menemukan letak kesalahan program.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

P a g e | 10

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

3.1.4 Pin assignment

Pada kode program sebelumnya telah didefinisikan beberapa port input dan output. Namun,

pada tahap tersebut belum didefinisikan alamat port saat nantinya program didownload ke

hardware. Dengan kata lain, untuk mengimplementasikan program pada harware FPGA,

setiap port yang didefinisikan dalam kode harus diberi alamat sesuai alamat sesungguhnya

pada hardware. Jika semua port sudah diberi alamat pada hardware, maka selanjutnya tinggal

menyambungkan hardware FPGA dengan dunia luar seperti saklar, lampu dan lain-lain.

Untuk kali ini, dunia luar yang dimaksudkan diwakili sementara oleh beberapa switch, push

button dan lampu led yang sudah disediakan pada board. Oleh karena itu, perlu diketahui

alamat switch, push button dan led pada board Spartan-3E. Informasi alamat simulator input

dan output tersebut dapat dilihat pada Spartan-3E FPGA Starter Kit Board User Guide. Cara

lainnya adalah dengan mengamati langsung petunjuk tulisan di board. Pada setiap simulator

input dan output di board selalu dituliskan alamat pemanggilan pin yang bersangkutan.

Misalkan pada slider switch dituliskan (L13) yang berarti bahwa alamat pemanggilan slider

switch tersebut pada L13.

Nama port pada kode

Switch0

Switch1

Switch2

Switch3

Pushbutton

LEDs(0)

LEDs(1)

Deskripsi

Slider switch (input)

Slider switch (input)

Slider switch (input)

Slider switch (input)

Push button (input)

Indikator LED (output)

Indikator LED (output)

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

Alamat Pin FPGA

L13

L14

H18

N17

V4

F12

E12

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 11

Langkah untuk menghubungkan port yang telah didefinisikan dengan switch, push button dan

led pada board adalah sebagai berikut:

1. Klik tanda + pada user constraints. Di dalamnya, lakukan dobel klik pada I/O Pin

Planning (PlanAhead) Pre-Synthesis. Jika muncul tanda peringatan create UCF file, klik

YES

2. Setelah proses selesai, maka akan muncul jendela program lain, yakni PlanAhead.

3. Pada I/O ports, klik tanda + pada LEDs dan Scalar port untuk menjabarkan seluruh input

output

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 12

4. Lakukan editing pada Site, drive strength dan pull type untuk seluruh port input dan

output yang terdefinisi dan pastikan hasil akhirnya seperti gambar di bawah.

Note:

site adalah alamat pin pada hardware FPGA

drive strength adalah set minimum arus yang disediakan (mA)

pull type adalah penambahan pull-up atau pull-down pada pin FPGA. Untuk switch,

Pull-up sebenarnya bersifat opsional, namun disarankan agar input tetap terdefinisi

ketika switch berada di tengah transisi antara on dan off. Ketika switch berada di

ON, FPGA pin terkoneksi ke logic high sedangkan ketika posisi OFF, FPGA pin

terkoneksi ke ground. Untuk push button, pull-down resistor diperlukan untuk

memberikan logic low (ground) ketika tombol tidak ditekan [Spartan 3E User Guide]

Secara default, I/O std adalah LVCMOS25 dengan SLOW slewrate dan output drive

12 mA

5. Klik Save pada PlanAhead untuk menyimpan konfigurasi port

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 13

3.1.5 Implement design dan Summary

Terdapat 4 proses utama dalam implement design:

Synthesize

Translate

Map

Place & Route

: men-generate netlist untuk setiap source file

: menggabungkan beberapa netlist menjadi single netlist

: pemetaan desain pada slice dan i/o blocks

: penempatan desain pada chip dan hubungan antar komponennya

1. Kembali pada program ISE project manager, klik tanda + pada implement design. Lakukan

dobel klik pada implement design dan secara otomatis program akan melakukan synthesizeXST, translate, map, serta place and routing. Setelah keempat prosedur selesai, akan muncul

tanda centang hijau untuk setiap proses.

2. Pada jendela processes, dobel klik Design summary/reports

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 14

3. Pada Design summary dapat dilihat bahwa impelentation state telah placed and routed

dengan no errors. Di bagian bawah, dapat dilihat penggunaan resource device. Seperti yang

tampak, penggunaan desain masih 1% sampai 3% saja.

3.2 Download ke board

Pada prosedur selanjutnya akan dilakukan generate programming file yang kemudian

didownload ke board Spartan-3E melalui Impact.

1. Pada program ISE project manager, lakukan dobel klik pada generate programming file.

Setelah proses selesai akan muncul tanda centang berwarna hijau.

2. Klik tanda + pada configure target device dan dobel klik pada manage configuration

project (impact)

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 15

3. Jendela program impact akan muncul. Pada tahap ini, pastikan board terhubung dengan

power dan kabel USB telah tersambung dengan PC. Setelah semua tersambung, nyalakan

switch board agar ON.

Note: saat pertama kali board terhubung PC, tunggu beberapa saat untuk instalasi driver

kabel USB

4. Setelah memastikan device terhubung, dobel klik boundary scan pada impact flows. Dari

langkah tersebut, akan muncul right click to add device or initialize JTAG chain pada

jendela bagian kanan.

5. Klik kanan dan pilih initialize chain

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 16

6. Setelah proses identifikasi chain selesai, akan muncul notifikasi identify succeded dan

muncul jendela Do you want to continue and assign configuration file(s)? pilih yes.

Perhatikan gambar chain chip yang muncul. Chip yang pertama yakni xc3s500e adalah chip

FPGA yang akan diprogram pada board. Kedua chip lain adalah chip pada board yang akan

di bypass.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 17

7. Pada assign new configuration file, pilih file *.bit hasil generate programming file yang

telah dibuat pada langkah sebelumnya. File ini akan diasosiasikan dengan chip yang pertama

yakni xc3s500e.

8. Berikutnya akan muncul pesan lain berisi This device supports attached flash PROMs. Do

you want to attach an SPI or BPI PROM to this device? Pilih NO.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 18

9. Jendela assign new configuration file akan muncul lagi untuk asosiasi dengan xcf04s. Kali

ini pilih bypass.

10. Terakhir, jendela assign new configuration files untuk xc2c64a akan muncul. Sekali lagi

pilih bypass.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 19

11. Terakhir akan muncul device programming properties. Klik OK.

12. Jendela impact akan tampak seperti gambar berikut. Klik akanan pada chip xc3e500e dan

pilih program.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 20

13. Program yang telah dibuat akan didownload ke board Spartan-3E dan setelah proses

selesai akan muncul notifikasi Program succeeded

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 21

14. Setelah selesai, lakukan simulasi langsung pada board dengan merubah kondisi switch

dan push button sesuai beberapa kondisi desain dan perhatikan perubahan kondisi LED.

Perhatikan, saat board dimatikan lalu dinyalakan lagi maka program akan hilang karena tidak

tersimpan ke dalam PROM.

3.3 Simulasi

Simulasi perilaku desain program dapat dilakukan melalui program Isim simulator. Disini,

akan dibuat test bench yang berupa pemberian stimulus pada setiap port input sehingga

kondisi output dapat dimonitor dan dibandingkan dengan desain yang diharapkan.

1. Langkah pertama, tambahkan test bench dengan cara klik Project>>New source pada ISE

project manager. Pilih VHDL test bench, beri nama top_test dan klik next

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 22

2. Test bench yang dibuat akan diasosiasikan dengan source top yang telah dibuat. Klik

next

3. Terakhir, akan ditunjukkan Summary pembuatan new source. Klik finish

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 23

4. Ganti tampilan implementation menjadi simulation. Perhatikan bahwa di process window

sekarang berisi item Isim simulator. Abaikan error yang muncul di message window untuk

sementara.

5. Lakukan dobel klik pada top_test.vhd jika belum terbuka. Perhatikan struktur konten dari

file tersebut yang terdiri dari entity dan architecture seperti halnya kode source program. Di

bagian architecture seluruh input diinisialisasi dengan nilai awal 0.

Di bagian ini juga terdapat beberapa konstanta <clock> yang berguna untuk desain berbasis

clock. Penamaan <clock> harus diganti dengan input aktual yang bertugas sebagai clock.

Namun untuk desain tutorial ini tidak memerlukan clock sehingga kode yang berisikan

clock akan dihapus.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 24

6. Cari seluruh konten kode test bench yang berkaitan dengan <clock> dan buang dari kode

dengan cara memberikan comment pada line tersebut. Comment dapat dibuat dengan

menambahkan -- pada awal setiap baris kode. Untuk beberapa baris kode, comment dapat

dibuat dengan melakukan blok seluruh baris kode yang akan di-comment dan kemudian klik

kanan>>comment>>selection. Perhatikan bahwa setelah semua kode <clock> di-comment,

maka pesan error di message window akan hilang setelah program di save. Jika pesan error

belum hilang, cek kembali seluruh kode <clock> dan pastikan semua telah terbuang dengan

cara menjadikannya comment.

7. Masukkan kode test bench setelah -- insert stimulus here dan sebelum wait

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

P a g e | 25

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

Kode test bench yang digunakan adalah (merujuk pada timing diagram port input):

-- insert stimulus here

Switch1 <='1';

Pushbutton <='1';

wait for 10 ns;

Switch0 <='1';

Switch1 <='0';

Switch3 <='1';

Pushbutton <='0';

wait for 10 ns;

Switch1 <='1';

Pushbutton <='1';

wait for 10 ns;

Switch2 <='1';

Switch3 <='0';

Pushbutton <='0';

wait for 10 ns;

Pushbutton <='1';

wait for 10 ns;

Switch3 <='1';

Pushbutton <='0';

wait for 10 ns;

Pushbutton <='1';

wait for 10 ns;

8. Setelah kode test bench dimasukkan, klik tanda + pada Isim simulator dan dobel klik pada

Behavioral check syntax sehingga muncul tanda centang hijau. Klik kanan pada simulate

behavioral model dan pilih process properties.

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

P a g e | 26

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

9. Pada simulation run time, isi dengan 200 ns. Ini adalah durasi waktu simulasi akan

dijalankan. Klik OK

10. Dobel klik simulate behavioral model, dan jendela program ISim akan terbuka

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 27

11. Agar tampilan sinyal simulasi mudah dibaca, lakukan pengaturan tampilan dengan

melalui View>>Zoom>>To full view.

12. Klik tanda + disamping LEDs untuk memonitor tampilan output led secara individual.

Cek hasil simulasi secara timing diagram dengan kesesuaian pada desain sistem

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Pengenalan Pemrograman FPGA: Spartan 3e (VHDL)

P a g e | 28

4. Referensi

[1] Spartan-3E FPGA Starter Kit Board User Guide, Online:

http://www.xilinx.com/support/documentation/boards_and_kits/ug230.pdf

[2] Spartan-3E FPGA Starter Kit Board Design Examples, Online:

http://www.xilinx.com/products/boards/s3estarter/reference_designs.htm

[3] FPGA Prototyping By VHDL Examples. Pong P. Chu. A John Wiley & Sons, Inc.,

Publication: 2008

[4] The Spartan-3E Tutorial 1: Introduction to FPGA Programming. Jasmine Banks.

Queensland University of Technology: 2014

XILINX SPARTAN-3E (PROJECT NAVIGATOR VER. 13.4)

FILKOM | UB

Anda mungkin juga menyukai

- Panduan Menginstall Windows Vista Sp2 Edisi Bahasa InggrisDari EverandPanduan Menginstall Windows Vista Sp2 Edisi Bahasa InggrisPenilaian: 5 dari 5 bintang5/5 (1)

- Introduction To Fpga ProgrammingDokumen27 halamanIntroduction To Fpga ProgrammingHeri J SitumorangBelum ada peringkat

- Introduction To Fpga Programming PDFDokumen28 halamanIntroduction To Fpga Programming PDFCakra BhirawaBelum ada peringkat

- Made Wira Narendra Wirsuyana - P5Dokumen39 halamanMade Wira Narendra Wirsuyana - P5wira narendraBelum ada peringkat

- FPGA PengenalanDokumen39 halamanFPGA Pengenalanwira narendraBelum ada peringkat

- Made Wira Narendra Wirsuyana - P6Dokumen37 halamanMade Wira Narendra Wirsuyana - P6wira narendraBelum ada peringkat

- Count Up Down FpgaDokumen49 halamanCount Up Down Fpgawira narendraBelum ada peringkat

- PENGENALAN FPGA Instalasi Software QuartusDokumen7 halamanPENGENALAN FPGA Instalasi Software QuartusRijaldi NaqsyabandiBelum ada peringkat

- EL2102 Modul4 13212047Dokumen3 halamanEL2102 Modul4 13212047Artha RajasaBelum ada peringkat

- PLDDokumen8 halamanPLDDarius KyrieBelum ada peringkat

- Rangkaian KombinasionalDokumen10 halamanRangkaian KombinasionalDuta FickyBelum ada peringkat

- Pertemuan 05 - Materi 04 - ESP 8266Dokumen16 halamanPertemuan 05 - Materi 04 - ESP 8266Azukni Elshyrazie100% (1)

- Programmable Logic DeviceDokumen30 halamanProgrammable Logic DeviceAgung SetiawanBelum ada peringkat

- Kel 2 KD 2Dokumen10 halamanKel 2 KD 2Mokhamad Rakhmat AfandhiBelum ada peringkat

- Perancangan Sistem DigitalDokumen9 halamanPerancangan Sistem DigitalAgung HaryantoBelum ada peringkat

- Pengenalan Desain Menggunakan FpgaDokumen7 halamanPengenalan Desain Menggunakan FpgaAbdul Hafizh FirdausBelum ada peringkat

- Laporan Simulasi Tahap 2 - Menghubungkan Arduino Uno Dengan Ethernet Shield Ke PC DanDokumen16 halamanLaporan Simulasi Tahap 2 - Menghubungkan Arduino Uno Dengan Ethernet Shield Ke PC DanIsa MahfudiBelum ada peringkat

- Modul Membuat Downloader Model USB Dan Sistem MinimumDokumen13 halamanModul Membuat Downloader Model USB Dan Sistem MinimumFuan AdiBelum ada peringkat

- VLSI Dan Perancangan Logika - Panduan Pemrogaman FPGADokumen13 halamanVLSI Dan Perancangan Logika - Panduan Pemrogaman FPGAmara dianaBelum ada peringkat

- El - 10. FpgaDokumen31 halamanEl - 10. Fpgaaji pamungkas tri nurcahyoBelum ada peringkat

- Tugas Akhir m4 Samsul Alam IotDokumen8 halamanTugas Akhir m4 Samsul Alam IotigaBelum ada peringkat

- Ebook Basic IoTDokumen18 halamanEbook Basic IoTkendali alfiBelum ada peringkat

- M Saeful P3A RangkumanDokumen14 halamanM Saeful P3A RangkumanSaefulBelum ada peringkat

- BluetoothArduinoDokumen20 halamanBluetoothArduinoSatriani RahmayantiBelum ada peringkat

- Programmable Logic Device (PLD)Dokumen26 halamanProgrammable Logic Device (PLD)yuli0% (1)

- LUT Berciri Khas Mempunyai 4 Buah InputanDokumen2 halamanLUT Berciri Khas Mempunyai 4 Buah InputanAku Ya AkuBelum ada peringkat

- Laporan Praktikum 5 Sistem DigitalDokumen11 halamanLaporan Praktikum 5 Sistem DigitalkyrgiosBelum ada peringkat

- Field Programmable Gate ArrayDokumen4 halamanField Programmable Gate Arrayyuwan_ajaBelum ada peringkat

- Firewall TrafficShapingDokumen51 halamanFirewall TrafficShapingKurniawan Setyo NugrohoBelum ada peringkat

- Modul 1Dokumen12 halamanModul 1RahmadiBelum ada peringkat

- Modul 6 SisdigDokumen15 halamanModul 6 SisdigSonya TooruBelum ada peringkat

- Akses BluetoothDokumen20 halamanAkses BluetoothIntan Ayu KurniaBelum ada peringkat

- ESP32 Syifa Nurul Afni 181331030Dokumen9 halamanESP32 Syifa Nurul Afni 181331030SYIFA NURUL AFNI -Belum ada peringkat

- KJD Ajinomoto RevisiDokumen19 halamanKJD Ajinomoto RevisiZerachielBelum ada peringkat

- Laporan MikrokontrolerDokumen27 halamanLaporan Mikrokontrolercici ferawatiBelum ada peringkat

- IoT - 10 - Mikrokontroler 1Dokumen41 halamanIoT - 10 - Mikrokontroler 1adnan AdnanBelum ada peringkat

- Modul Prakt DSK Revised 2018Dokumen3 halamanModul Prakt DSK Revised 2018Nasrun IshakBelum ada peringkat

- Laporan Jaringan Sensor Nirkabel 1Dokumen54 halamanLaporan Jaringan Sensor Nirkabel 1dienul haryantoBelum ada peringkat

- Node MCUDokumen50 halamanNode MCUHannaBelum ada peringkat

- Laporan Firewall Dan IptablesDokumen11 halamanLaporan Firewall Dan IptablesAditya Rizeky SuwarsonoBelum ada peringkat

- Modul Sistem Terbenam Rev. 02Dokumen66 halamanModul Sistem Terbenam Rev. 02Bagusti MuspratamaBelum ada peringkat

- FPGADokumen3 halamanFPGAabd_fikrie2316Belum ada peringkat

- Artikel Programmable Logic Devices KLL HHHHHHHHHHDokumen5 halamanArtikel Programmable Logic Devices KLL HHHHHHHHHHBagoest KurniawanBelum ada peringkat

- Laporan Mikroprosesor - Wireless Interface WiFi - Melisa 42220011Dokumen14 halamanLaporan Mikroprosesor - Wireless Interface WiFi - Melisa 42220011MeliBelum ada peringkat

- Modul 4 - EL2142 Prak. SisdigMikDokumen29 halamanModul 4 - EL2142 Prak. SisdigMikMachianoMachiBelum ada peringkat

- AsmArduino#01 Blink SerialDokumen12 halamanAsmArduino#01 Blink SerialAdhistira Fajar LesmanaBelum ada peringkat

- Perangkat Masukan Dan Keluaran ArduinoDokumen56 halamanPerangkat Masukan Dan Keluaran ArduinoIndahAzizahBelum ada peringkat

- Manual DST AVRDokumen16 halamanManual DST AVRGhian HufaidillahBelum ada peringkat

- Laporan Resmi Praktikum 1Dokumen12 halamanLaporan Resmi Praktikum 1tlazuardiBelum ada peringkat

- Joob Sheet V Pemrograman Mikrokontroler Arduino Untuk Running LEDDokumen22 halamanJoob Sheet V Pemrograman Mikrokontroler Arduino Untuk Running LEDAl MtdrsBelum ada peringkat

- Interfacing Port Paralel KomputerDokumen32 halamanInterfacing Port Paralel KomputerUlan PradaniBelum ada peringkat

- 12 - 3DD4 - Mery Octavia Ningrum - ArtikelDokumen12 halaman12 - 3DD4 - Mery Octavia Ningrum - ArtikelMery OctaviaBelum ada peringkat

- PSo CDokumen10 halamanPSo CMaghfirah PajuBelum ada peringkat

- Tugas Simulasi Gerbang Logika - Robby Okta ChandraDokumen15 halamanTugas Simulasi Gerbang Logika - Robby Okta ChandraRobiy creative idBelum ada peringkat

- Modul Praktikum Ten 1 KomdatDokumen17 halamanModul Praktikum Ten 1 Komdatfaiz fauzanBelum ada peringkat

- El2102 02 13217032Dokumen9 halamanEl2102 02 13217032Adrian SembiringBelum ada peringkat

- Petunjuk Praktikum AVR-CodeVisionDokumen181 halamanPetunjuk Praktikum AVR-CodeVisionFaela Ma'ana Shufa100% (1)

- Perangkat Logika Terprogram (PLD)Dokumen14 halamanPerangkat Logika Terprogram (PLD)maldinlubisBelum ada peringkat

- Project Iot Kontrol LED Dengan WiFiDokumen11 halamanProject Iot Kontrol LED Dengan WiFiPutraBelum ada peringkat

- Manajemen Operasi Bab 3 - Pengelolaan KuDokumen23 halamanManajemen Operasi Bab 3 - Pengelolaan KuRifqi AnshariBelum ada peringkat

- MAKALAH Instrumen Keuangan DerivatifDokumen27 halamanMAKALAH Instrumen Keuangan DerivatifRifqi AnshariBelum ada peringkat

- 2 PPT Masalah Ketenagakerjaan Di IndonesiaDokumen10 halaman2 PPT Masalah Ketenagakerjaan Di IndonesiaRifqi AnshariBelum ada peringkat

- MAKALAH Instrumen Keuangan DerivatifDokumen27 halamanMAKALAH Instrumen Keuangan DerivatifRifqi AnshariBelum ada peringkat

- Biaya Berdasarkan AktivitasDokumen24 halamanBiaya Berdasarkan AktivitasRifqi AnshariBelum ada peringkat

- RifqiAnshari 135150300111012Dokumen9 halamanRifqiAnshari 135150300111012Rifqi AnshariBelum ada peringkat

- Remaster Dengan RemastersysDokumen15 halamanRemaster Dengan RemastersysRifqi AnshariBelum ada peringkat

- Remaster Dengan RemastersysDokumen15 halamanRemaster Dengan RemastersysRifqi AnshariBelum ada peringkat

- Penerapan Metode Zieger Nichols PIDDokumen4 halamanPenerapan Metode Zieger Nichols PIDRifqi AnshariBelum ada peringkat