Pert.5 - Internal Memory

Diunggah oleh

Vian Meus0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

8 tayangan22 halamanJudul Asli

Pert.5 - Internal Memory - Copy

Hak Cipta

© © All Rights Reserved

Format Tersedia

PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

8 tayangan22 halamanPert.5 - Internal Memory

Diunggah oleh

Vian MeusHak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 22

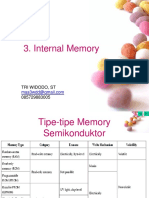

Penyimpanan permanen non-volatile

Diprogram secara microprogramming (pemrogram

mikroprosesor)

Biasanya untuk menyimpan :

Library subroutines untuk fungsi-fungsi sistem yang

sering dipanggil

System Programs (BIOS)

Tabel Set Instruksi

Program ditulis pada saat pembuatan (manufaktur)

masks tidak bisa diubah/dihapus

Programmable (once)

PROM (PROgrammable Memory) (OTP-ROM)

Diprogram dengan alat khusus

Programmable – Program bisa ditulis ulang

Untuk menulis membutuhkan waktu lebih lama dari

membaca

Erasable Programmable (EPROM)

Dihapus dengan UV – semua isi memory

Electrically Erasable (EEPROM)

Dihapus secara elektrik dg field emission (Fowler-

Nordheim tunneling) – bisa per byte

Flash memory

Dihapus secara elektrik dg field emission – bisa semua

isi memory, bisa per blok

Operasi: Baca & Tulis (Read & Write)

Volatile (membutuhkan daya untuk menyimpan data)

Sarana penyimpanan temporer

Bersifat static atau dynamic

Secara fisik terdiri atas sel-sel memory, satu sel dapat

menyimpan satu bit

Menggunakan KAPASITOR Bit data disimpan sebagai

tegangan (charge) di dalam kapasitor

Tegangan cenderung bocor (berkurang)

Membutuhkan refreshing, meskipun dalam kondisi ada

daya (power on)

Membutuhkan adanya sirkuit untuk refresh

Lebih lambat

Konstruksi lebih sederhana, lebih murah

Tempat yang dipakai per bitnya lebih kecil

Metode penyimpanan analog

Besar kecilnya tegangan menentukan nilai

Paling umum dipakai sebagai main memory

Refresh circuit terintegrasi dalam chip, melakukan

refresh tiap interval tertentu sebelum waktu simpan

kapasitor habis (biasanya tiap waktu paruh)

Cara kerja:

1. Disable chip (chip dibuat tidak bisa diakses untuk sementara)

2. Count through rows (dilakukan per baris sel-sel memory):

Read & Write back (Baca dan tulis lagi ke alamat yang sama)

Hal ini membutuhkan waktu dan memperlambat

kinerja

DIGITAL (Menggunakan rangkaian flip-flop)

Bits disimpan sebagai switch on/off (secara logika)

Tidak memakai tegangan yang dapat bocor

Tidak membutuhkan refreshing selama ada daya

(powered)

Tidak membutuhkan sirkuit untuk refresh

Lebih cepat

Konstruksi lebih rumit

Tempat yang dipakai menyimpan per bit lebih besar

Lebih mahal

Biasanya untuk cache

Keduanya volatile

Membutuhkan daya untuk menyimpan data

Dynamic cell

Lebih gampang dibuat dan lebih kecil

Lebih padat (lebih banyak bit bisa disimpan)

Memungkinkan dibuat keping memory bersatuan besar

Murah

Tapi butuh refresh

Static cell

Lebih cepat, tidak butuh refresh, tapi mahal

Hanya untuk cache

Akses disinkronisasikan dengan external clock

(biasanya system clock – clock CPU)

Pada proses pembacaan data dari RAM:

1. RAM dikirim alamat yg akan dibaca

2. RAM mencari data

Pada DRAM konvensional, CPU akan menunggu

Pada SDRAM, karena proses perpindahan data sudah

dijadwalkan, CPU tahu kapan data siap, sehingga CPU

tidak harus menunggu, bisa mengerjakan hal lain

Burst mode (kalau ada) membuat SDRAM dapat

stream data dan mengirimnya dalam bentuk blok

DDR-SDRAM mengirim data dua kali per siklus clock

Double Data Rate

Dalam melaksanakan fungsi penyimpanan, memori

semikonduktor dimungkinkan mengalami kesalahan.

Jenis Error: Hard Failure

Bersifat permanen, fisik, disebabkan penggunaan yang

tidak semestinya, cacat

pabrik atau usia

Jenis Error: Soft Error

Random, non-destructive

Tidak permanen, disebabkan masalah power Supply,

berhubungan data yang disimpan.

Kesalahan ringan dapat dikoreksi kembali.

Koreksi kesalahan data yang disimpan diperlukan dua

mekanisme

Mekanisme pendeteksian kesalahan

Mekanisme perbaikan kesalahan

Diciptakan Richard Hamming di Bell Lab 1950

Mekanisme pendeteksian kesalahan dengan menambahkan

data word (D) dengan suatu kode, biasanya bit cek paritas

(C).

Data yang disimpan memiliki panjang D + C.

Kesalahan diketahui dengan menganalisa data dan bit paritas

tersebut untuk memeriksa apakah ada data yang berubah

Pemikiran dasar: dari serentetan bit data pasti bisa

didapatkan sebuah ciri yang menunjukkan keterhubungan

antar data. Ciri tersebut disimpan sebagai check bit

# Data Bits # Bit Paritas

SEC

8 4

16 5

32 6

64 7

128 8

512 9

Penambahan bit cek paritas untuk koreksi kode Hamming

Aturan untuk menentukan C :

dengan exclusive-OR dijumlahkan:

C1 = D1 D2 D4 D5 D7

C2 = D1 D3 D4 D6 D7

C4 = D2 D3 D4 D8

C8 = D5 D6 D7 D8

Kemudian check bits yang didapat saat data disimpan di

-kan dengan check bits saat pembacaan.

Bilangan biner yang didapat menunjukkan letak bit data

yang salah, kemudian bit yang salah di NOT-kan

masukkan data : 00111001 kemudian ganti bit data ke 3

dari 0 menjadi 1 sebagai error-nya.

Bagaimanakah cara mendapatkan bit data ke 3 sebagai

bit yang terdapat error?

Jawab :

Masukkan data pada perumusan cek bit paritas :

C1 = 1 0 1 1 0 = 1

C2 = 1 0 1 1 0 = 1

C4 = 0 0 1 0 =1

C8 = 1 1 0 0 =0

Sekarang bit 3 mengalami kesalahan data menjadi:

00111101

C1 = 1 0 1 1 0 = 1

C2 = 1 1 1 1 0 = 0

C4 = 0 1 1 0 =0

C8 = 1 1 0 0 =0

Apabila bit – bit cek dibandingkan antara yang lama

dan baru maka terbentuk syndrom word :

C8 C4 C2 C1

0 1 1 1

0 0 0 1

0 1 1 0 =6

Sekarang kita lihat posisi bit ke-6 adalah data ke-3.

Mekanisme koreksi kesalahan akan meningkatkan

realibitas bagi memori

Menambah kompleksitas pengolahan data.

Menambah kapasitas memori karena adanya

penambahan bit – bit cek paritas.

Memori akan lebih besar beberapa persen atau dengan

kata lain kapasitas penyimpanan akan berkurang

karena beberapa lokasi digunakan untuk mekanisme

koreksi kesalahan

Diadopsi Intel untuk seri Pentium keatas

(Tadinya) Kompetitor SDRAM & DDR gagal karena

skandal

Adalah DDR dengan Bus khusus DRAM, pertukaran

data lewat 28 kabel dengan panjang < 12 cm. CPU

request data ke controller RDRAM

Bus mengalamati sampai 320 RDRAM chips dengan

kecepatan 1.6Gbps (480ns access time)

Anda mungkin juga menyukai

- IoT - 14 - IoT Device (Node) 1Dokumen29 halamanIoT - 14 - IoT Device (Node) 1Irfan Maulana IIBelum ada peringkat

- AorkomDokumen43 halamanAorkomDmitri PetrenkoBelum ada peringkat

- Pertemuan Ke - 9 Memori: Politeknik Elektronika Negeri SurabayaDokumen45 halamanPertemuan Ke - 9 Memori: Politeknik Elektronika Negeri SurabayaNanius MuribBelum ada peringkat

- 05-Memori Internal PDFDokumen37 halaman05-Memori Internal PDFsatryazegbiBelum ada peringkat

- 10-Memori InternalDokumen37 halaman10-Memori Internalbaguswibowo700Belum ada peringkat

- Organisasi Komputer Minggu 6Dokumen49 halamanOrganisasi Komputer Minggu 6Sulistyawan Abdilah RosyidBelum ada peringkat

- Perluasan MemoriDokumen11 halamanPerluasan MemoriAmeeda Ummu FauzyBelum ada peringkat

- Bab 8 - 13Dokumen79 halamanBab 8 - 13Fahat PusamaniaBelum ada peringkat

- Kuliah 6 Org - Kom - Memory InternalDokumen38 halamanKuliah 6 Org - Kom - Memory InternalJason SanjayaBelum ada peringkat

- Tugas Daring Cache Dan Memory Berlian Ishma Zhafira Sujana - 225150207111008Dokumen4 halamanTugas Daring Cache Dan Memory Berlian Ishma Zhafira Sujana - 225150207111008BERLIAN ISHMA ZHAFIRA SUJANABelum ada peringkat

- Dasar Sistem KomputerDokumen6 halamanDasar Sistem KomputerCitra lestariBelum ada peringkat

- Evolusi KomputerDokumen28 halamanEvolusi KomputerGonBelum ada peringkat

- Penghitungan Cache MemoryDokumen42 halamanPenghitungan Cache MemoryIsnant B Faried0% (1)

- Soal Sistem Operasi-JwbanDokumen14 halamanSoal Sistem Operasi-JwbanHeri Sri PurnomoBelum ada peringkat

- MikrokontrolerDokumen9 halamanMikrokontrolerAndi Muh Rifqy MuskarBelum ada peringkat

- Materi Perangkat Keras KomputerDokumen46 halamanMateri Perangkat Keras KomputerSATRIA BUANABelum ada peringkat

- Soal It Support TestDokumen6 halamanSoal It Support TestZaheer DeniesBelum ada peringkat

- Set Instruksi 88Dokumen42 halamanSet Instruksi 88Kizaragi ragnaBelum ada peringkat

- Tugas COA Week 6Dokumen5 halamanTugas COA Week 6Luhung FdBelum ada peringkat

- Perbedaan Processor 32 Bit Dan 64-Bit (TUGAS 1)Dokumen5 halamanPerbedaan Processor 32 Bit Dan 64-Bit (TUGAS 1)Ahmad X-plorerBelum ada peringkat

- Pertemuan 2 Sistem OperasiDokumen17 halamanPertemuan 2 Sistem Operasiusmanaliit77Belum ada peringkat

- SlideDokumen33 halamanSlideSeto Isak MulyantoBelum ada peringkat

- At89s51 Vs Atmega 8535Dokumen4 halamanAt89s51 Vs Atmega 8535Yaqub SudiroBelum ada peringkat

- Tugas Materi Ke 2Dokumen3 halamanTugas Materi Ke 2D shadowBelum ada peringkat

- Bab7 MemoryDokumen32 halamanBab7 MemoryNanang SofiyullahBelum ada peringkat

- Prosessor 8088Dokumen20 halamanProsessor 8088Yusuf WeeBelum ada peringkat

- Prosessor 8088Dokumen16 halamanProsessor 8088Yusuf WeeBelum ada peringkat

- Arsitektur MikrokontrolerDokumen66 halamanArsitektur MikrokontrolerAlfi SyahrinBelum ada peringkat

- Mikroprosesor 8085Dokumen93 halamanMikroprosesor 8085Syukron WBelum ada peringkat

- Kursus Komputer LengkapDokumen42 halamanKursus Komputer LengkapWelly Klinik DataBelum ada peringkat

- Lapaw 1Dokumen24 halamanLapaw 1Ma'rufah DalimuntheBelum ada peringkat

- Laporan Troubleshooting 1-2Dokumen16 halamanLaporan Troubleshooting 1-2Hani Ikhsantoso100% (1)

- Translate Orakom Halaman 163-166Dokumen5 halamanTranslate Orakom Halaman 163-166Johnny RpdtlBelum ada peringkat

- Slide MikroprosesorDokumen266 halamanSlide MikroprosesorAch RefiandriBelum ada peringkat

- Running Text Dengan Mikrokontroler At89s51Dokumen11 halamanRunning Text Dengan Mikrokontroler At89s51Siscaa Ithu Moerdie100% (1)

- Interupsi Dan DMADokumen25 halamanInterupsi Dan DMAarystayeniBelum ada peringkat

- Modul Pelatihan Mikrokontroler AT89S51Dokumen50 halamanModul Pelatihan Mikrokontroler AT89S51Han Arif100% (1)

- Programmer SPI FLASHROM Untuk Port ParalelDokumen8 halamanProgrammer SPI FLASHROM Untuk Port ParalelKepompong WangwungBelum ada peringkat

- QUIZ (1) Arkom SA02 (1322051,1322052,1322053,1322054,1322055)Dokumen6 halamanQUIZ (1) Arkom SA02 (1322051,1322052,1322053,1322054,1322055)Zahra AnggrainiBelum ada peringkat

- Antarmuka MemoriDokumen59 halamanAntarmuka MemoriArifFadilahBelum ada peringkat

- Fungsi Sistem KomputerDokumen15 halamanFungsi Sistem KomputerNur HasBelum ada peringkat

- Z 80Dokumen7 halamanZ 80الأولياء إلهامBelum ada peringkat

- Soal Mid InterfaceDokumen11 halamanSoal Mid InterfaceIta BychubbyBelum ada peringkat

- Tugas 3 - Claudia Lintang H.RDokumen5 halamanTugas 3 - Claudia Lintang H.RClaudia Lintang Hayuning RatriBelum ada peringkat

- Soal Kelas 11 TKJDokumen2 halamanSoal Kelas 11 TKJImron RosadiBelum ada peringkat

- 20200801361-Maulana Fajar Lazuardi-Tugas Sesi 2 Sistem OperasiDokumen8 halaman20200801361-Maulana Fajar Lazuardi-Tugas Sesi 2 Sistem OperasiCindy Ariani PashaBelum ada peringkat

- Mikroprosesor 8085 Des 2023pptxDokumen95 halamanMikroprosesor 8085 Des 2023pptxPro Hdr GesBelum ada peringkat

- Pemeliharan Perangkat KomputerDokumen12 halamanPemeliharan Perangkat KomputerMutiara ZulqoidahBelum ada peringkat

- Resume Materi 5 - Internal MemoryDokumen6 halamanResume Materi 5 - Internal MemoryHaris MuhajirBelum ada peringkat

- Sinopsis BukuDokumen8 halamanSinopsis BukuHegaline Ferdi EndamBelum ada peringkat

- Materi MikroprosessorDokumen73 halamanMateri Mikroprosessorguruh wijayaBelum ada peringkat

- Raw 3Dokumen32 halamanRaw 3syafruddinr_68006517Belum ada peringkat

- Sismik Tgs 2Dokumen5 halamanSismik Tgs 2Tia Rahma100% (1)

- Makalah MikroprosesorDokumen13 halamanMakalah MikroprosesorSiboru Hombing Bere SitanggangBelum ada peringkat

- (The Real) Perbedaan Scanf Dengan GetsDokumen4 halaman(The Real) Perbedaan Scanf Dengan GetsVian MeusBelum ada peringkat

- Hasil Studi 18102151 - S6Dokumen3 halamanHasil Studi 18102151 - S6Vian MeusBelum ada peringkat

- Ujian Tengah Semester Agama KristenDokumen2 halamanUjian Tengah Semester Agama KristenVian MeusBelum ada peringkat

- 1398 2338 1 SMDokumen9 halaman1398 2338 1 SMVian MeusBelum ada peringkat

- LAPORANDokumen3 halamanLAPORANVian MeusBelum ada peringkat

- Uas Robotika Lanjut - 18102151Dokumen3 halamanUas Robotika Lanjut - 18102151Vian MeusBelum ada peringkat

- Organisasi KomputerDokumen21 halamanOrganisasi KomputerVian MeusBelum ada peringkat

- 78 243 1 PBDokumen6 halaman78 243 1 PBkuraku nimeBelum ada peringkat

- Makalah Ekonomi-2Dokumen9 halamanMakalah Ekonomi-2Vian MeusBelum ada peringkat

- Tsunami BADokumen13 halamanTsunami BAVian MeusBelum ada peringkat

- Pengenceran JoDokumen18 halamanPengenceran JoVian MeusBelum ada peringkat

- Makalah Tim Base Project Kelompok 2Dokumen5 halamanMakalah Tim Base Project Kelompok 2Vian MeusBelum ada peringkat

- Kumpulan Peraturan & Pedoman Penanganan Covid-19 PDFDokumen549 halamanKumpulan Peraturan & Pedoman Penanganan Covid-19 PDFcondet city100% (3)

- Dealer List - PT Piaggio Indonesia: Area: JabodetabekDokumen1 halamanDealer List - PT Piaggio Indonesia: Area: JabodetabekLabdaily LabdailyBelum ada peringkat

- Surat Keterangan Kelas XLLDokumen1 halamanSurat Keterangan Kelas XLLVian MeusBelum ada peringkat

- Arif Sinaga Archimedes-1Dokumen18 halamanArif Sinaga Archimedes-1Vian MeusBelum ada peringkat

- Arif LangrangeDokumen27 halamanArif LangrangeVian MeusBelum ada peringkat

- PHP Dasar Tutorial PDFDokumen181 halamanPHP Dasar Tutorial PDFالحواس سيتياوانBelum ada peringkat

- Cover PengenceranDokumen1 halamanCover PengenceranVian MeusBelum ada peringkat

- Pengenceran JoDokumen18 halamanPengenceran JoVian MeusBelum ada peringkat

- Arif LangrangeDokumen27 halamanArif LangrangeVian MeusBelum ada peringkat

- Pengenceran JoDokumen18 halamanPengenceran JoVian MeusBelum ada peringkat

- Sekolah Tinggi Manajemen Informatika & Komputer IndonesiaDokumen1 halamanSekolah Tinggi Manajemen Informatika & Komputer IndonesiaVian MeusBelum ada peringkat

- Soal UTS Sistem Informasi S1 Pengantar Organisasi &arsitektur KomputerDokumen5 halamanSoal UTS Sistem Informasi S1 Pengantar Organisasi &arsitektur KomputerVian MeusBelum ada peringkat

- Bab4 Hukumohmdayadanenergi-1Dokumen41 halamanBab4 Hukumohmdayadanenergi-1Vian MeusBelum ada peringkat

- Krispinus - Arif - Sinaga - Mali Gerak HArmonik Acc 1 Denis-1Dokumen39 halamanKrispinus - Arif - Sinaga - Mali Gerak HArmonik Acc 1 Denis-1Vian MeusBelum ada peringkat

- Krispinus - Arif - Sinaga - Mali Gerak HArmonik Acc 1 Denis-1Dokumen19 halamanKrispinus - Arif - Sinaga - Mali Gerak HArmonik Acc 1 Denis-1Vian MeusBelum ada peringkat

- Memory Eksternal PersentaseDokumen17 halamanMemory Eksternal PersentaseVian MeusBelum ada peringkat

- Baca AkuDokumen1 halamanBaca AkuVian MeusBelum ada peringkat