Chapter 2-Field-Effect Transistor (FET)

Diunggah oleh

Silviharyani0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

36 tayangan37 halamantugas

Judul Asli

Chapter 2-Field-effect Transistor (FET)

Hak Cipta

© © All Rights Reserved

Format Tersedia

PPT, PDF, TXT atau baca online dari Scribd

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen Initugas

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PPT, PDF, TXT atau baca online dari Scribd

0 penilaian0% menganggap dokumen ini bermanfaat (0 suara)

36 tayangan37 halamanChapter 2-Field-Effect Transistor (FET)

Diunggah oleh

Silviharyanitugas

Hak Cipta:

© All Rights Reserved

Format Tersedia

Unduh sebagai PPT, PDF, TXT atau baca online dari Scribd

Anda di halaman 1dari 37

Medan Efek

Transistors (FETs)

EBB424E

Dr. Sabar D. H

School of Materials & Mineral Resources Engineering,

Universiti Sains Malaysia

Medan Efek Transistor (FET)

Pada tahun 1945, Shockley punya ide untuk membuat

perangkat padat dari semikonduktor.

Dia berfikir bahwa medan listrik yang kuat dapat menyebabka

n aliran listrik dalam semikonduktor terdekat.

Dia mencoba untuk membuat satu, tapi itu tidak berhasil.

Tiga tahun kemudian, Brattain & Bardeen membuat kerja

transistor pertama, transisto rtitik kontak germanium, yang

dirancang sebagai transistor pertemuan (sandwich).

Pada tahun 1960 lmuwan dari Bell, John Atalla

mengembangkan desain baru berdasarkanteori-teori efekmedan yang asli Shockley's.

Akhir tahun 1960-an, produsen dikonversi dari persimpangan

jenis sirkuit terpadu kebidang efek perangkat.

medan Efek Transistor (FET)

Medan efek perangkat adalah mereka yang saat

ini dikendalikan oleh tindakan medan elektron, daripada

injeksi pembawa.

Medan Efek Transistor dinamakan demikian karena lemah

sinyal listrik yang masuk melalui satu elektroda menciptakan

Medan elektrik melalui sisa transistor.

FET dikenal sebagai transistor unipolar".

Istilah mengacu pada kenyataan bahwa saat ini

diangkut oleh pembawa satu polaritas(mayoritas), sedangkan

dalam transistor bipolar konvensional pembawa kedua

polaritas (mayoritas dan minoritas) terlibat.

medan Efek Transistor (FET)

Perangkat FET dapat dibagi menjadi:

Persimpangan

FET

Penipisan Mo MOSFET

Peningkatan Mode MOSFET

Junction FETs (JFETs)

TJFETs terdiri dari sepotong bahan semikonduktor resisti

vitas tinggi (biasanya Si) yangmerupakan saluran untuk

aliran pembawa mayoritas.

Melakukan kanal semikonduktor di antara dua kontak oh

mik-sumber & drain

Junction FETs (JFETs)

Besarnya saat ini dikendalikan oleh tegangan yang

diterapkan ke gerbang, yaitu bias terbalik.

Perbedaan mendasar antara perangkat JFET dan BJT: ketika

JFET dipanjar terbalik gerbang saat ini adalah hampir nol,

sedangkan arus basis transistor selalu lebih besar dari nol.

Junction FETs

JFET adalah perangkat resistensi tinggi-masukan, sementara

BJT relatif rendah.

Jika saluran dikotori dengan kotoran donor, bahan tipe-n

dibentuk dan saluran saat ini akan terdiri dari elektron.

Jika saluran dikotori dengan kotoran Penerima, bahan tipe-p

akan terbentuk dan saluran saat ini akan terdiri dari lubang.

Peragkat Kanal-N memiliki konduktivitas yang lebih besar

daripada jenis kanal-p, karena elektron memiliki mobilitas

yang lebih tinggi daripada lubang; dengan demikiankanaln JFETs adalah sekitar dua kali konduktor efisien

dibandingkan dengan rekan-rekan kanal-p mereka

Basic structure of JFETs

Selain

saluran, JFET berisi

dua kontak ohmik: sumber

dan cerat.

JFET akan melakukan arus

baik sama arah dan sumbe

r dan cerat memimpin

biasanya dipertukarkan.

B a s ic s tru c tu re

G a te

G

G

C irc u it s y m b o l

fo r n -c h a n n e l F E T

S o u rc e

D ra in

n -ch a n n e l

S

G

D

p+

p+

p+

C ro s s s e c tio n

n -c h a n n e l

In s u la tio n

(S iO 2 )

n

p

S

C hannel

th ic k n e s s

D e p le tio n

re g io n s

D e p le tio n

re g io n

M e ta l e le c tro d e

n -c h a n n e l

(b )

p+

(a )

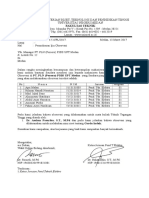

(a) Sruktur dasar dari junction Medan Efek Transistor

(JFET) dengan kanal-n, dua wilayah p+ tersambung elektrik

dan terbentuk gerbang. (b) sketsa sederhana dari

penampang dari kanal-n JFET yang lebih praktis

Kanal-N JFET

Transistor ini dibuat oleh pe

mbentukan bahan saluran

dari tipe-N di substrat tipeP.

Tiga kabel kemudian dihub

ungkan ke perangkat.

Satu di setiap akhir kanal.

Salah satu terhubung ke

substrat.

Dalam arti, perangkat ini se

perti dioda PN-junction,

kecuali bahwa ada dua

kabel terhubung ke sisi

tipe-N.

Bagaimana JFET Berfungsi

Gerbang terhubung ke sumber.

Karena pn dipanjar

terbalik-, arus kecil akan menga

lir di gerbang sambungan.

Gradien potensi yang didirikan

akan membentuk lapisan pemis

kinan, dimana hampir semua

elektron yang hadir di Selat tipe

-n akan lenyap.

Bagian paling habis di bidang ti

nggi antara G dan D, dan daera

h habis setidaknyaantara G dan

S.

Bagaimana JFET Berfungsi

Karena aliran arus sepanjang

kanal dari (+ ve) mengalir ke (ve) sumber benar-benar

sebuahaliran elektron bebas d

ari S d di Si tipe-n, besarnya

saat ini akan jatuh seperti Si

lebih menjadi habis elektron

bebas.

Ada batas arus cerat (ID) yang

meningkat VDS bisa melewati

saluran.

Ini membatasi saat dikenal seb

agai IDSS (arus cerat-kesumberdengan gerbang

korsleting ke sumber

Output karakteristik JFET kanal-n dengan gerbang

hubung pendek ke sumber.

Kenaikan awal ID terkait dengan penumpukan lapisa

n pemiskinan sebagai VDSmeningkat.

Kurva pendekatan tingkat IDSS saat ini membatasi

ketika ID mulai mencubit.

Arti fisik dari istilah ini mengarah ke salah satu

definisi sejumput tegangan, VP, yangmerupakan nilai

VDS di mana IDSS maksimum mengalir.

Dengan kemantapan gerbang-sumber

tegangan 1 V adalah selalu 1 V di

seluruh dindingsaluran di ujung sumber

Tegangan cerat-sumber 1 V berarti

bahwa akan ada 2 V di dinding di ujung

cerat.

(Saluran adalah 'up' 1V dari sumber po

tensial dan gerbang ini 1V 'turun', kare

naperbedaan total adalah 2V)

Perbedaan tegangan tinggi di ujung cer

at berarti bahwa saluran elektron diper

as ke bawah sedikit lebih di akhir ini.

Ketika tegangan cerat-sumber

ditingkatkan menjadi 10V tegang

an dinding saluranyang di ujung

cerat meningkat untuk 11V, tapi t

etap hanya 1V di ujung sumber.

Bidang di seluruh dinding dekat

ujung cerat kini jauh lebih

besar dari pada akhir sumber.

Akibatnya saluran dekat saluran

diperas turun cukup banyak.

Menguras sumber tegangan 20V turun

ke Channel.

Kami meningkatkan tegangan

dan meningkatkan medan listrik yang m

endorong elektron

sepanjang membuka bagian dari salura

n.

Namun, juga memaksa turun saluran d

ekat ujung cerat.

Pengurangan ini dalam saluran terbuka

lebar membuat elektron lebih

sulit untuk keluar.

Akibatnya arus cerat-sumber

cenderung tetap konstan ketika kita me

ningkatkan tegangan cerat-sumber

Meningkatkan VDS lebar dari lapisan pemiskinan, yang me

nembus lebih ke dalam saluran dan oleh karena itu

menghasilkan lebih banyak saluran penyempita nterhadap

saluran.

Resistansi kanal-n, RAB karenanya meningkatkan dengan

VDS.

Arus cerat: id = VDS RAB

ID versus VDS pameran perilaku sublinear, lihat gambar un

tuk VDS < 5V.

Tegangan jepit-off, VP adalah besarnya reverse bias di p +

n junction yang diperlukanuntuk membuat mereka hanya m

enyentuh pada ujung cerat.

Karena sebenarnya tegangan bias di p + n junction di

pembuangan akhir VGD,mencubit-off terjadi setiap

kali: VGD = -VP.

VDS luar = VP, ada saluran

pendek kurus panjang, po.

VDS meningkat, sebagian be

sar tegangan tambahan hany

a di po, wilayah ini

kehabisanoperator dan

karenanya sangat resistif.

Tegangan di seluruh panjang

saluran, Lch tetap sebagai V

P.

Luar pinch-off ID = VP

RAP (VDS > VP).

Apa yang terjadi ketika

tegangan negatif,

dikatakan bahwa

VGS= -2V, diterapkan

ke gerbang sehubungan

dengan sumber (dengan

VDS = 0).

P + n persimpangan

sekarang di reverse bias

dari awal, saluran ini se

mpit, dan resistansi

kanal sekarang lebih

besar daripada di VGS =

0 kasus.

Drain arus yang mengalir ketika VDS kecil diterapkan

(Gambar b) sekarang lebih kecil daripada di VGS = 0

kasus.

Terapan VDS = 3 V untuk pinch-off saluran (Gambar c).

Ketika VDS = 3V, VGD di p + n persimpangan di saluran

akhir adalah 5V, yang -vp, sehingga saluran menjadi

pinch-off.

Luar pinch-off, ID hampir jenuh seperti di VGS = 0

kasus.

Pinch-off terjadi pada VDS = VDS (duduk), VDS (duduk)

= VP + VGS, di mana VGS adalah tegangan ve

(mengurangi VP).

Untuk VDS> VDS (duduk), ID menjadi hampir jenuh

pada nilai sebagai IDS

Luar pinch-off, dengan ve VGS, IDS adalah

Dimana RAP (VGS) adalah resistansi efektif dari

budidaya n-channel dari A ke P, yang tergantung

pada ketebalan saluran dan karenanya VGS.

Ketika VGS = -vp = 5V dengan VDS = 0, dua

lapisan deplesi menyentuh atas seluruh panjang

saluran dan seluruh saluran ditutup.

Saluran ini dikatakan off.

Ada hubungan yang baik antara IDS dan VGS.

Luar pinch-off

I DS I DSS 1

VGS

VGS ( off )

Dimana IDSS adalah mengalirkan arus ketika VGS

= 0 dan VGS (off) didefinisikan sebagai -vp, yaitu

tegangan gerbang-sumber yang hanya pinch-off

saluran.

Pinch off tegangan VP sini adalah ve kuantitas

karena diperkenalkan melalui VDS (duduk).

VGS (off) namun negatif, -vp.

I-V characteristics

I-V characteristics

JFET: I-V characteristics

Proses untuk merencanakan kurva

transkonduktansi untuk JFET

diberikan :

Plot titik yang sesuai dengan nilai VGS

( off ) .

Plot poit yang sesuai dengan nilai IDSS

.

Pilih 3 atau lebih nilai VGS antara 0 V

dan VGS ( off ) .

Untuk nilai VGS , menentukan nilai dari

ID dari Plot titik dari ( 3 ) dan

menghubungkan semua titik diplot

dengan kurva mulus .

JFET Biasing Sirkuit

Contoh : Plot garis Bias dc untuk tegangan

- driver sirkuit biasing

Anda mungkin juga menyukai

- Uji Validitas Dan Reliabilitas TesDokumen10 halamanUji Validitas Dan Reliabilitas TesSilviharyaniBelum ada peringkat

- JFETDokumen9 halamanJFETFrima Setyawan Nur RohmanBelum ada peringkat

- Makalah JFETDokumen15 halamanMakalah JFETHenrikus12Belum ada peringkat

- Pertemuan Ke-14 Transistor FETDokumen19 halamanPertemuan Ke-14 Transistor FETSasisusu Tarmin MamenBelum ada peringkat

- Quis 3 Dasar ElektonikaDokumen7 halamanQuis 3 Dasar ElektonikaariBelum ada peringkat

- Transistor FETDokumen14 halamanTransistor FETYusrandi Jabbar AwingBelum ada peringkat

- JFETDokumen9 halamanJFETJuniSiburianBelum ada peringkat

- FetDokumen20 halamanFetDindi H. MahfieBelum ada peringkat

- Transistor Efek MedanDokumen20 halamanTransistor Efek MedanMaulan24 Syarif100% (1)

- Tugas Power SupplyDokumen11 halamanTugas Power SupplyevhyajahBelum ada peringkat

- Fisika DivaisDokumen5 halamanFisika DivaisKharina AnjaniBelum ada peringkat

- Jfet, Mosfet, UjtDokumen6 halamanJfet, Mosfet, UjtIrfan Wahyu RamadhanBelum ada peringkat

- Pertemuan KesembilanDokumen30 halamanPertemuan Kesembilanpeggy pratamaBelum ada peringkat

- Field Effect Transistor (FET)Dokumen11 halamanField Effect Transistor (FET)Galih AjiBelum ada peringkat

- Elektronika 2Dokumen39 halamanElektronika 2Friska WilfiandaBelum ada peringkat

- Macam - Macam TransistorDokumen10 halamanMacam - Macam TransistorbagindutBelum ada peringkat

- Transistor FETDokumen16 halamanTransistor FETMoonchild HanaBelum ada peringkat

- Dioda SemikonduktorDokumen31 halamanDioda SemikonduktorMazju KrosixBelum ada peringkat

- Microsoft PowerPoint - 7 - JFET PDFDokumen112 halamanMicrosoft PowerPoint - 7 - JFET PDFAde GamingBelum ada peringkat

- TransistorDokumen15 halamanTransistorNanda Ainal YakinBelum ada peringkat

- Pengertian FetDokumen6 halamanPengertian Fetmiss_fifiBelum ada peringkat

- Dioda SemikonduktorDokumen18 halamanDioda SemikonduktorWinarni SariBelum ada peringkat

- Fet & MosfetDokumen9 halamanFet & MosfetAngga Nur Rahmat0% (1)

- Bab IDokumen34 halamanBab IAnwar NasihinBelum ada peringkat

- Karakteristik JFET Dan MOSFETDokumen61 halamanKarakteristik JFET Dan MOSFETSwintro Bushido SinurayaBelum ada peringkat

- 2 PN JunctionDokumen25 halaman2 PN Junctionnormal11 sayabisaBelum ada peringkat

- 2 PN JunctionDokumen25 halaman2 PN JunctionDimas Fahrezi HartonoBelum ada peringkat

- Semikonduktor Diode & TransistorDokumen18 halamanSemikonduktor Diode & TransistorTiara HandeBelum ada peringkat

- Makalah MOSFET, BJT Dan IGBTDokumen24 halamanMakalah MOSFET, BJT Dan IGBTBelayaSalsabilaBelum ada peringkat

- DiodeDokumen25 halamanDiodeMuhammad HikmalBelum ada peringkat

- Transistor JfetDokumen6 halamanTransistor JfetRetno AnjasariBelum ada peringkat

- Pertemuan - 15 - PNPN DevicesDokumen22 halamanPertemuan - 15 - PNPN DevicesMangkubumi AppBelum ada peringkat

- Jawaban Latihan Kelompok 4 Elektronika DasarDokumen3 halamanJawaban Latihan Kelompok 4 Elektronika DasarJessikaBelum ada peringkat

- Resistor BipolarDokumen43 halamanResistor BipolarmirdaBelum ada peringkat

- MosfetDokumen12 halamanMosfetImam Fakhrurrozi HidayatBelum ada peringkat

- Transistor BJTDokumen6 halamanTransistor BJTNovita PatriciaBelum ada peringkat

- FetDokumen19 halamanFetAnggie Putty TrianiBelum ada peringkat

- Pengertian Field Effect TransistorDokumen7 halamanPengertian Field Effect TransistorFauzan FhBelum ada peringkat

- Makalah Arus DCDokumen16 halamanMakalah Arus DCmusdalifah100% (3)

- Field Effect TransistorDokumen20 halamanField Effect Transistorwahyu adiBelum ada peringkat

- Dioda ZenerDokumen21 halamanDioda Zenersheren diustiBelum ada peringkat

- Contoh Soal PhotovoltaikDokumen6 halamanContoh Soal PhotovoltaikJuliawan PutuBelum ada peringkat

- Microsoft PowerPoint - 6 - Transistor PDFDokumen103 halamanMicrosoft PowerPoint - 6 - Transistor PDFAde GamingBelum ada peringkat

- Pertemuan 02Dokumen20 halamanPertemuan 02anon_502252296Belum ada peringkat

- Penyearah Gelombang Pembalik FasaDokumen23 halamanPenyearah Gelombang Pembalik FasaMora DellanaBelum ada peringkat

- Afief Rahman Hakim - TE01 - Tugas Elektronika Pertemuan 12Dokumen8 halamanAfief Rahman Hakim - TE01 - Tugas Elektronika Pertemuan 12Afief Rahman HakimBelum ada peringkat

- 132963-Junction Field Effect Transistor (Ardiansyah, Dwi Apriliansyah, Nur Ilmi H.)Dokumen12 halaman132963-Junction Field Effect Transistor (Ardiansyah, Dwi Apriliansyah, Nur Ilmi H.)Nur IlmiBelum ada peringkat

- Modul 4 FETDokumen14 halamanModul 4 FETromi hendrixBelum ada peringkat

- Laporan BJT & JFET Sebagai DC SwitchDokumen12 halamanLaporan BJT & JFET Sebagai DC Switchmuhammad ali fikriBelum ada peringkat

- Dasar - Dasar TransistorDokumen20 halamanDasar - Dasar TransistorAgil Dwy CahyoBelum ada peringkat

- Bab 1 KArakteristik DiodaDokumen15 halamanBab 1 KArakteristik DiodaYoga AdiBelum ada peringkat

- Percobaan Karakteristik DiodaDokumen15 halamanPercobaan Karakteristik DiodaRahmat Juniar DwiansyahBelum ada peringkat

- Makalah Elektronika FET BAB 1 Dan 2Dokumen18 halamanMakalah Elektronika FET BAB 1 Dan 2bimadrdBelum ada peringkat

- Perangkat Elektronika JfetDokumen9 halamanPerangkat Elektronika JfetAuliya RahmatBelum ada peringkat

- Pada Semikonduktor Junction Membahas Mengenai Kesetimbangan Termal Sudah Membahas Mengenai Difusi Dan Drift Pada Zona Deplesi Sudah StabilDokumen6 halamanPada Semikonduktor Junction Membahas Mengenai Kesetimbangan Termal Sudah Membahas Mengenai Difusi Dan Drift Pada Zona Deplesi Sudah StabilindaBelum ada peringkat

- Soal LatihanDokumen3 halamanSoal LatihanAG Gumelar MuktiBelum ada peringkat

- Transistor Efek Medan Kel. 7Dokumen19 halamanTransistor Efek Medan Kel. 7St MaisarahBelum ada peringkat

- Makalah JfetDokumen10 halamanMakalah Jfetnhoe nurjannaBelum ada peringkat

- Pertemuan 6 Penguat Sinyal Kecil (Fet)Dokumen29 halamanPertemuan 6 Penguat Sinyal Kecil (Fet)Pandi Indra KurniaBelum ada peringkat

- Materi JfetDokumen21 halamanMateri Jfetaurora azaleaBelum ada peringkat

- Adjustablehand ReamerDokumen10 halamanAdjustablehand ReamerSilviharyaniBelum ada peringkat

- Cara Menghitung Uji Reliabilitas Secara ManualDokumen2 halamanCara Menghitung Uji Reliabilitas Secara ManualSilviharyani0% (1)

- TransmisiDokumen26 halamanTransmisiSilviharyani100% (1)

- CoverDokumen2 halamanCoverSilviharyaniBelum ada peringkat

- Penilaian Kinerja 14Dokumen17 halamanPenilaian Kinerja 14SilviharyaniBelum ada peringkat

- 144 242 1 SMDokumen10 halaman144 242 1 SMSilviharyaniBelum ada peringkat

- Kumpulan SoalDokumen9 halamanKumpulan SoalSilviharyaniBelum ada peringkat

- Hakekat PerkembanganDokumen12 halamanHakekat PerkembanganSilviharyaniBelum ada peringkat

- E BookDokumen83 halamanE BookSilviharyani100% (1)

- Format CJRDokumen21 halamanFormat CJRSilviharyaniBelum ada peringkat

- 21 778 Maina PDFDokumen119 halaman21 778 Maina PDFSilviharyaniBelum ada peringkat

- Rule of Law Dan Hak Asasi Manusia (KEL 6)Dokumen29 halamanRule of Law Dan Hak Asasi Manusia (KEL 6)SilviharyaniBelum ada peringkat

- Critical BookDokumen68 halamanCritical BookSilviharyaniBelum ada peringkat

- Soal UtsDokumen5 halamanSoal UtsSilviharyaniBelum ada peringkat

- Gardu Induk Paya PasirDokumen23 halamanGardu Induk Paya PasirSilviharyaniBelum ada peringkat

- Lembar Kerja Pertemuan IIIDokumen2 halamanLembar Kerja Pertemuan IIISilviharyaniBelum ada peringkat

- Surat Observasi PT PLNDokumen1 halamanSurat Observasi PT PLNSilviharyaniBelum ada peringkat

- Ulasan Dear NathanDokumen5 halamanUlasan Dear NathanSilviharyani100% (1)