Struktur Dan Prinsip Kerja Transistor Metal Oxide Semiconductor

Diunggah oleh

Angga Wijaya KusumaHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Struktur Dan Prinsip Kerja Transistor Metal Oxide Semiconductor

Diunggah oleh

Angga Wijaya KusumaHak Cipta:

Format Tersedia

Struktur dan Prinsip Kerja Transistor Metal Oxide Semiconductor (MOS)

Analisis dan perancangan IC sangat tergantung pada pemilihan model yang cocok sebagai komponen IC.

Untuk analisis secara manual, cukup digunakan model-model yang sederhana. Untuk analisis dengan

komputer, digunakan model-model yang lebih rumit.

Karena untuk analisis, atau perancangan, hanya seakurat seperti model-model yang digunakan, maka

pemahaman model-model yang mendalam dan derajat pendekanan yang diambil adalah penting.

Karena itu, struktur internal dan proses konduksi di dalam transistor dan dioda perlu dikaji dengan

baik. Dalam analisis dan perancangan IC digital perlu mengetahui model yang digunakan sebagai

pendekatan divais.

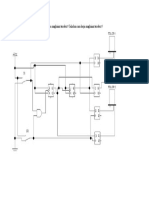

Di atas ini adalah gambar perspektip dan simbol skematis dari transistor MOS kanal-n dengan gate

silikon.

Penampang transistor MOS di atas ini digambar dengan jelas dan secara rinci untuk

menerangkan prinsip kerja transistor nMOS. Bila suatu tegangan dikenakan pada elektroda gate maka

timbul suatu medan elektrik untuk mengatur konduksi di antara bagian source dan bagian drain

yang heavily doping (n

+

). Karena menggunakan medan elektrik, divais ini adalah salah satu bentuk

dari field-effect transistor (FET).

Karena gate tersekat sama sekali dari elektroda-elektroda yang lain, divais ini disebut juga insulated

gate field-effect transistor (IGFET). Masih ada nama lain, yaitu transisor unipolar. Disebut transistor

unipolar, karena hanya ada satu macam pembawa muatan (elektron di dalam nMOS) yang diperlukan

untuk operasi divais ini. Hole yang 'bergerak' dalam substrat jenis-p pada transistor nMOS tidak terlibat

dalam operasi yang normal. Berlainan dengan sebuah nMOS atau transistor unipolar lain, sebuah

transistor bipolar npn atau pnp harus melibatkan baik elektron maupun hole dalam operasinya.

Belum ada terminologi yang baku yang diterima secara luas, sehingga istilah MOST, MOSFET, FET, dan

IGFET masih banyak digunakan untuk menyebut divais MOS ini.

Struktur divais transistor nMOS ini untuk menjadi IC dengan urutan langkah-langkah: oksidasi, pattern

definition (penentuan pola), difusi, implantasi ion, dan proses-prose deposisi, serta pembuangan

material.

Pada divais transistor pMOS, polaritas tegangan simetris tapi berlawanan dengan polaritas tegangan

divais transistor nMOS. Pembahasan divais nMOS di atas tadi juga berlaku untuk pembahasan divais

pMOS. Mengenai penentuan polaritas positip, negatip dan jenis-n, jenis-p saling dipertukarkan bila

keduanya muncul bersamaan.

Poses Fabrikasi Transistor nMOS Dengan Teknologi MOS

Untuk memahami aspek-aspek perancangan berbasis proses, maka pertama-tama perlu dpelajari yang

dinamakan polysilicon gate self-aligning nMOS process. Disini akan dibahas pembuatan enhancement

mode transistor dalam bentuk IC di dalam substrat silikon.

Tahap 1 Sebuah wafer tipis silikon murni dengan diameter 75 sampai 100 mm dan tebal 0,4 mm

mengalami doping dengan impuriti atom boron dengan konsentrasi 10

15

sampai 10

16

atom/cm

3

dan

wafer dengan resistivitas 25 sampai 26 ohm.cm.

Tahap 2 Seluruh permukaan wafer kemudian dibuat lapisan silikon dioksida (SiO2) setebal 1 mikro m

sebagai lapisan pelindung terhadap dopant (bahan doping) selama dilakukan proses.

Tahap 3 Sekarang, di atas seluruh permukaan dilapisi denganphotoresist dan diputar untuk

menndapatkan lapisan yang rata dengan ketebalan tertentu.

Tahap 4 Selanjut lapisan photoresist disinari dengan ultraviolet melewati masker untuk menentukan

tempat-tempat yang akan dillakukan difusi. Pada tempat yang terkena radiasi sinar ultraviolet terjadi

polimerisasi (mengeras), tapi pada tempat yang tidak tembus sinar ultraviolet tidak terjadi

polimerisasi.

Tahap 5 Kemudian dilakukan proses development (pengembangan) untuk

membersihkan photoresist yang tidak mengalami polimerisasi. Selanjutnya dilakukan

proses etching untuk mengikis silikon dioksida yang tidak dilindingi photoresist. Sekarang ada

permukaan wafer yang terbuka, tidak ditutupi oleh silikon oksida.

Tahap 6 Sisa photoresist dibersihkan/dihapus dan selanjutnya di seluruh permukaan wafer

ditumbuhkan lapisan silikon tipis setebal 0,1 mikro m dan di atas silikon dioksida tipis dituang

polisilikon untuk membuat gate.

Tahap 7 Sekali lagi dilakukan pelapisan photoresist dan dengan menggunakan masker untuk membuat

pola polisilikon dan lapisan silikon di bawahnya dikikis untuk membuka tempat-tempat dilakukan difusi

impuriti jenis-n untuk membuat source dan drain. Difusi ini dikerjakan dengan jalan memanasi wafer

pada suhu tinggi dan di atas permukaan waafer diliwatkan gas pembawa impuriti fosfor. Selama difusi

polisilikon, silikon dioksida menjadi pelindung, proses itu disebut self-aligning.

Tahap 8 Penumbuhan lapisan silikon dioksida tebal di seluruh permukaan lagi, dan di atasnya dilapisi

dengan photoresist untuk membuka tempat-tempat di gate polisilikon, di source dan drain untuk

membuat sambungan.

Tahap 9 Kemudian di atas seluruh permukaan wafer dituangkan lapisan aluminium setebal 1 mikro m.

Selanjutnya lapisan aluminium dilapisi photoresist dan di atasnya diberi masker untuk membentuk pola

interkoneksi yang dinginkan.

Jadi, proses fabrikasi IC dengan teknologi MOS merupakan pengulangan-pengulangan di seputar

pembentukan atau penuangan (deposition), membuat pola (patterning) tiga lapisan, dipisahkan dengan

penyekat (insulation) silikon dioksida. Lapisan-lapisan itu terdiri dari lapisan difusi dalam substrat,

polisilikon di atas silikon dioksida pada substrat, dan lapisan metal yang tersekat terhadap silikon

dioksida.

Urutan proses fabrikasi IC transistor nMOS digambarkan dengan penampang tegaknya sebagai berikut.

Pada gambar top view (tampak atas), lapisan kaca dan passivationtidak digambarkan, meskipun bentuk

bukaan kontak terlihat melalui lapisan kaca. Gambar top view menunjukkan posisi gate.

Garis terputus-putus menunjukkan bidang penampang tegak.

Anda mungkin juga menyukai

- ChipDokumen6 halamanChipRais gordonBelum ada peringkat

- Fabrikasi IC Dan Teknologi IC CMOS N-WellDokumen9 halamanFabrikasi IC Dan Teknologi IC CMOS N-WellanwarBelum ada peringkat

- Struktur IC Adalah Sangat Kompleks Baik Dari Sisi Topografi Permukaan Maupun Komposisi InternalnyaDokumen10 halamanStruktur IC Adalah Sangat Kompleks Baik Dari Sisi Topografi Permukaan Maupun Komposisi InternalnyaNavis Al-RizkyBelum ada peringkat

- Kelompok 5 Fabrikasi Mosfet StsDokumen15 halamanKelompok 5 Fabrikasi Mosfet StsSalsabila Dhiya P.SBelum ada peringkat

- Teknologi Rangkaian TerpaduDokumen3 halamanTeknologi Rangkaian TerpaduWowon PriatnaBelum ada peringkat

- EDIT Nanoteknologi Bidang Elektronik SUCIDokumen31 halamanEDIT Nanoteknologi Bidang Elektronik SUCISuci WinarsihBelum ada peringkat

- Tugas 6Dokumen9 halamanTugas 6Mauudin BRgBelum ada peringkat

- SiapDokumen23 halamanSiapwaroeng angkerBelum ada peringkat

- SiapDokumen22 halamanSiapwaroenkangkerBelum ada peringkat

- Tugas Makalah VlsiDokumen11 halamanTugas Makalah VlsijjBelum ada peringkat

- Pertemuan Ke-11 Litografi Dan EtsaDokumen6 halamanPertemuan Ke-11 Litografi Dan EtsaRizki KurniawanBelum ada peringkat

- Photolithography Dan DiodeDokumen4 halamanPhotolithography Dan Dioderinandityo2508Belum ada peringkat

- Ringkasan CMOS DigitalDokumen4 halamanRingkasan CMOS DigitalMuhammad RidwanBelum ada peringkat

- Tugas Teknik Rangkaian TerintegrasiDokumen9 halamanTugas Teknik Rangkaian TerintegrasiIrwin HardianBelum ada peringkat

- Transistor Dalam Ic MonolitikDokumen6 halamanTransistor Dalam Ic MonolitiknurhafniBelum ada peringkat

- Percobaan 2Dokumen6 halamanPercobaan 2St. Nawal JayaBelum ada peringkat

- Tentang Nanowire Atau Kawat Nano Dari NanoscienceDokumen6 halamanTentang Nanowire Atau Kawat Nano Dari NanoscienceCharnela MardaniBelum ada peringkat

- Proses Produksi IcDokumen10 halamanProses Produksi Icrizal tri susilo100% (1)

- Teks Presentasi Kelompok 2Dokumen37 halamanTeks Presentasi Kelompok 2Nurul ChasanahBelum ada peringkat

- Resistor Transistor LogicDokumen40 halamanResistor Transistor LogicHalim Adi SaputraBelum ada peringkat

- Karakteristik MosfetDokumen9 halamanKarakteristik MosfetAgustianVanHollanElroyBelum ada peringkat

- CmosDokumen7 halamanCmosRatihRizkiDahliaBelum ada peringkat

- Makalah SemikonduktorDokumen20 halamanMakalah SemikonduktorEnda Y. TanjungBelum ada peringkat

- Buku Ic UlfahDokumen99 halamanBuku Ic UlfahSuko Ariaswanto100% (1)

- Raika Ramadhani - Tugas 2 Metode PenelitianDokumen6 halamanRaika Ramadhani - Tugas 2 Metode PenelitianWanda MartinaBelum ada peringkat

- 2 - Fabrikasi SemikonduktorDokumen18 halaman2 - Fabrikasi SemikonduktorLuqi Rf BoltzmannBelum ada peringkat

- Jawaban SoalDokumen3 halamanJawaban SoalKhima AlbiBelum ada peringkat

- BJT Dan FabrikasiDokumen10 halamanBJT Dan FabrikasiFerry WeellBelum ada peringkat

- Tugas Rangkuman Pembuatan Chip Komputer Muhamad FebriansyahDokumen2 halamanTugas Rangkuman Pembuatan Chip Komputer Muhamad FebriansyahKomang AdeBelum ada peringkat

- Review Materi - Indah Khairun Nisa - F1C321039Dokumen4 halamanReview Materi - Indah Khairun Nisa - F1C321039Bambang JohariBelum ada peringkat

- Skripsi Awaluddin SaputraDokumen23 halamanSkripsi Awaluddin SaputraRaden Suryadi Surya NingratBelum ada peringkat

- DiscussionDokumen3 halamanDiscussionWan Abdul LatifBelum ada peringkat

- Teknologi Semikonduktor Dan PemanfaatannyaDokumen19 halamanTeknologi Semikonduktor Dan PemanfaatannyaKanzun FikriBelum ada peringkat

- Makalah Proses Fabrikasi ICDokumen16 halamanMakalah Proses Fabrikasi ICHamidan Keke0% (1)

- Makalah CMOSDokumen6 halamanMakalah CMOSAnq SolahBelum ada peringkat

- Rangkaian TerintegrasiDokumen19 halamanRangkaian TerintegrasiAbdul El HaqBelum ada peringkat

- 4565Dokumen9 halaman4565Ferdian Ariesta Adhi ChandraBelum ada peringkat

- Paper DdeDokumen43 halamanPaper DdeHabieb Alchemy AlayeersBelum ada peringkat

- Fabrikasi Elemen Sensor Gas Co Berbasis Media AktifDokumen8 halamanFabrikasi Elemen Sensor Gas Co Berbasis Media AktifIriantoBelum ada peringkat

- EMELIA KARNILA (Self-Assembly of Nano Particles)Dokumen15 halamanEMELIA KARNILA (Self-Assembly of Nano Particles)Emelia KarnilaBelum ada peringkat

- ID Pelapisan Tio2 Di Atas Fto Dengan TeknikDokumen4 halamanID Pelapisan Tio2 Di Atas Fto Dengan TeknikHasna NurulBelum ada peringkat

- Semikonduktor Tipe NDokumen34 halamanSemikonduktor Tipe NZya Jamaluddin Al-Rasyid ARBelum ada peringkat

- Tugas 1 - 2TEDokumen5 halamanTugas 1 - 2TEdaffaBelum ada peringkat

- MosfetDokumen36 halamanMosfetnisaBelum ada peringkat

- Proses Fabrikasi Bahan Semikonduktor Fotolitografi Sebagai Proses Perancangan Devais Transistor SemikonduktorDokumen5 halamanProses Fabrikasi Bahan Semikonduktor Fotolitografi Sebagai Proses Perancangan Devais Transistor SemikonduktorNur AfiyatBelum ada peringkat

- NanostrukturDokumen7 halamanNanostrukturNinnah NuhBelum ada peringkat

- Teknologi ICDokumen11 halamanTeknologi ICtardiaja100% (1)

- Mikroteknologi Adalah Teknologi Dengan Ciri Mendekati Ukuran Skala Satu MikrometerDokumen2 halamanMikroteknologi Adalah Teknologi Dengan Ciri Mendekati Ukuran Skala Satu MikrometerAndika SubagiaBelum ada peringkat

- Fabrikasi IC (Integrated Circuit)Dokumen32 halamanFabrikasi IC (Integrated Circuit)Kang Fathur100% (1)

- AnZlovar, SUB MICROMETER DAN NANO ZnO SEBAGAI FILLER DALAM BAHAN PMMADokumen5 halamanAnZlovar, SUB MICROMETER DAN NANO ZnO SEBAGAI FILLER DALAM BAHAN PMMAIntan IslamiatiBelum ada peringkat

- Karakterisasi MaterialDokumen9 halamanKarakterisasi MaterialIndah DarapuspaBelum ada peringkat

- DSSCDokumen3 halamanDSSCReza Ayu FebrianaBelum ada peringkat

- Karakterisasi MembranDokumen25 halamanKarakterisasi MembranputrimaharantiBelum ada peringkat

- Teori Dasar METALLOGRAFIDokumen9 halamanTeori Dasar METALLOGRAFIKhairul WaeBelum ada peringkat

- Perkembangan Teknologi Mikroelektronika #01Dokumen6 halamanPerkembangan Teknologi Mikroelektronika #01Tarjo SutarjoBelum ada peringkat

- Resume Catatan KuliahDokumen5 halamanResume Catatan KuliahWilliam LuffyBelum ada peringkat

- The First NanochipDokumen2 halamanThe First NanochipIgnatius Henry0% (1)

- Proses SegmentasiDokumen2 halamanProses SegmentasiAngga Wijaya KusumaBelum ada peringkat

- Proses SegmentasiDokumen1 halamanProses SegmentasiAngga Wijaya KusumaBelum ada peringkat

- Modul 1 Rectifier HalfwaveDokumen2 halamanModul 1 Rectifier HalfwaveAngga Wijaya KusumaBelum ada peringkat

- Modul Sistem-BilanganDokumen41 halamanModul Sistem-BilanganMokhamad Agusta AdikaraBelum ada peringkat

- Modul 2 Rectifier Halfwave FreewhelingDokumen1 halamanModul 2 Rectifier Halfwave FreewhelingAngga Wijaya KusumaBelum ada peringkat

- Proses Segmentasi PDFDokumen1 halamanProses Segmentasi PDFAngga Wijaya KusumaBelum ada peringkat

- Label FotoDokumen3 halamanLabel FotoAngga Wijaya KusumaBelum ada peringkat

- Modul 121Dokumen12 halamanModul 121Angga Wijaya KusumaBelum ada peringkat

- Modul 2 Rectifier Halfwave FreewhelingDokumen1 halamanModul 2 Rectifier Halfwave FreewhelingAngga Wijaya KusumaBelum ada peringkat

- Konsep Sistem RobotDokumen28 halamanKonsep Sistem RobotgillangrizkyBelum ada peringkat

- BankcounterDokumen1 halamanBankcounterAngga Wijaya KusumaBelum ada peringkat

- Modul 1 Rectifier HalfwaveDokumen2 halamanModul 1 Rectifier HalfwaveAngga Wijaya KusumaBelum ada peringkat

- Modul 3 Rectifier FullwaveDokumen1 halamanModul 3 Rectifier FullwaveAngga Wijaya KusumaBelum ada peringkat

- Perc4 CountersinkronDokumen4 halamanPerc4 CountersinkronRomdhon PrabowoBelum ada peringkat

- Elektronika IndustriDokumen90 halamanElektronika IndustriAngga Wijaya KusumaBelum ada peringkat

- Ilmu BahanDokumen9 halamanIlmu BahanAngga Wijaya KusumaBelum ada peringkat

- Perc1 Sekuensial1Dokumen4 halamanPerc1 Sekuensial1Muzaki KurniawanBelum ada peringkat

- Fungsi Fungsi IC Digital KombinasionalDokumen12 halamanFungsi Fungsi IC Digital KombinasionalAngga Wijaya KusumaBelum ada peringkat

- Kaca Dan PorselinDokumen14 halamanKaca Dan PorselinAngga Wijaya KusumaBelum ada peringkat

- Perc8 MemoryDokumen7 halamanPerc8 MemoryDwi SetiantoBelum ada peringkat

- Materi Elektronika DayaDokumen9 halamanMateri Elektronika DayaOva Imam AdityaBelum ada peringkat

- Modul 1 Rectifier HalfwaveDokumen2 halamanModul 1 Rectifier HalfwaveAngga Wijaya Kusuma100% (1)

- Materi Elektronika Daya InverterDokumen7 halamanMateri Elektronika Daya InverterPandey d'GunnerzBelum ada peringkat

- Upacara Suddhiwadani Dalam Pelaksanaan Perkawinan Di Desa Adat Ujung HyangDokumen50 halamanUpacara Suddhiwadani Dalam Pelaksanaan Perkawinan Di Desa Adat Ujung HyangAngga Wijaya KusumaBelum ada peringkat

- Biokimia (Bik)Dokumen8 halamanBiokimia (Bik)Shinta LeonitaBelum ada peringkat

- Repair SetrikaDokumen3 halamanRepair SetrikaAngga Wijaya KusumaBelum ada peringkat

- SoalDokumen15 halamanSoalnotden97Belum ada peringkat

- Teknologi Nano SensorDokumen16 halamanTeknologi Nano SensorAngga Wijaya KusumaBelum ada peringkat

- RPP Matematika 5Dokumen126 halamanRPP Matematika 5Eric WilkersonBelum ada peringkat

- Bank CounterDokumen1 halamanBank CounterAngga Wijaya KusumaBelum ada peringkat