Modul Vi Counter

Modul Vi Counter

Diunggah oleh

humayriJudul Asli

Hak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Modul Vi Counter

Modul Vi Counter

Diunggah oleh

humayriHak Cipta:

Format Tersedia

Modul Praktikum Teknik Digital

MODUL VI

BINARY COUNTER

1. Tujuan

Setelah melakukan percobaan ini, mahasiswa dapat :

a. Memahami koneksi yang diperlukan untuk D dan J-K berdasarkan UP counter.

b. State gate koneksi diperlukan untuk mengurangi jumlah binary UP counter.

c. State gate koneksi diperlukan untuk mengurangi jumlah binary DOWN counter.

2. Peralatan yang digunakan

a. CIRCUIT #2, #3 , #4 dan dan Logic Monitor of D3000 4.3 Sequential Logic-1 Module.

b. Multimeter.

c. Shorting links dan connecting leads.

3. Dasar Teori

Counter

Counter merupakan rangkaian logika pengurut, karena counter membutuhkan karakteristik

memori, dan pewaktu memegang peranan yang penting. Counter digital mempunyai

karakteristik penting yaitu sebagai berikut :

1. Jumlah hitungan maksimum (modulus N-counter)

2. Menghitung ke-atas atau ke-bawah (up atau down - counter)

3. Operasi asinkron atau sinkron

4. Bergerak bebas atau berhenti sendiri

Sebagaimana dengan rangkaian sekuensial yang lain, untuk menyusun counter digunakan flipflop. Counter dapat digunakan untuk menghitung banyaknya clock-pulsa dalam waktu yang

tersedia (pengukuran frekuensi), Counter dapat juga digunakan untuk membagi frekuensi dan

menyimpan data.

Counter Sinkron

Counter merupakan aplikasi dari Flip-flop yang mempunyai fungsi menghitung. Proses

penghitungan yang dilakukan Counter secara sekuensial, baik menghitung naik (Up Counting)

maupun turun (Down Counting).

COUNTER

VI - 1

Modul Praktikum Teknik Digital

Berdasarkan pemberian trigger di masing-masing flip-flop penyusun rangkaian Counter, dikenal

2 macam Counter : Counter Sinkron (Synchronous Counter) dan Counter Asinkron

(Asynchronous Counter).

Pada Counter Sinkron, sumber clock diberikan pada masing-masing input Clock dari Flip-flop

penyusunnya, sehingga apabila ada perubahan pulsa dari sumber, maka perubahan tersebut

akan men-trigger seluruh Flip-flop secara bersama-sama.

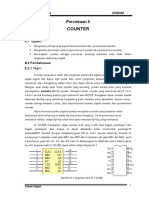

Gambar 6.1 Contoh Up Counter Sinkron 3 bit

Up Dan Down Counter

Sebuah Counter disebut sebagai Up Counter jika dapat menghitung secara berurutan mulai dari

bilangan terkecil sampai bilangan terbesar. Contoh : 0-1-2-3-4-5-6-7-0-1-2-.

Sedangkan Down Counter adalah Counter yang dapat menghitung secara berurutan dari

bilangan terbesar ke bilangan terkecil. Tabel PS/NS untuk Up dan Down Counter 3 bit seperti

ditunjukan pada Tabel 6.1.

Tabel 6.1 Tabel PS/NS untuk Up dan Down Counter 3 bit.

COUNTER

VI - 2

Modul Praktikum Teknik Digital

Untuk membuat sebuah rangkaian Up Counter, lakukan langkah-langkah sintesa rangkaian

yang telah dijelaskan sebelumnya. Dari hasil persamaan logika berdasarkan Tabel PS/NS di

atas didapatkan rangkaian seperti di bawah ini :

Gambar 6.2 Rangkaian Up Counter Sinkron 3 bit

Berdasarkan Tabel 6.1, dapat dilihat bahwa Down Counting merupakan kebalikan dari Up

Counting, sehingga rangkaiannya masih tetap menggunakan rangkaian Up Counter, hanya

outputnya diambilkan dari Q masing-masing Flip-flop. Bentuk rangkaian Down Counter adalah

seperti gambar 6.3.

Gambar 6.3 Rangkaian Down Counter Sinkron 3 bit

COUNTER

VI - 3

Modul Praktikum Teknik Digital

Rangkaian Up/Down Counter

Rangkaian Up/Down Counter merupakan gabungan dari Up Counter dan Down Counter.

Rangkaian ini dapat menghitung bergantian antara Up dan Down karena adanya input eksternal

sebagai control yang menentukan saat menghitung Up atau Down. Pada gambar 6.4

ditunjukkan rangkaian Up/Down Counter Sinkron 3 bit. Jika input CNTRL bernilai 1 maka

Counter akan menghitung naik (UP), sedangkan jika input CNTRL bernilai 0, Counter akan

menghitung turun (DOWN).

Gambar 6.4 Rangkaian Up/Down Counter Sinkron 3 bit.

Counter Asinkron

Pada Counter Asinkron, sumber clock hanya diletakkan pada input Clock di Flip-flop terdepan

(bagian Least Significant Bit / LSB), sedangkan input-input clock Flip-flop yang lain

mendapatkan catu dari output Flip-flop sebelumnya. Konfigurasi ini didapatkan dari gambar

timing diagram Counter 3-bit seperti ditunjukkan pada gambar 6.5. Dengan konfigurasi ini,

masing-masing flip-flop di-trigger tidak dalam waktu yang bersamaan. Model asinkron semacam

ini dikenal juga dengan nama Ripple Counter.

Gambar 6.5 Timing Diagram Up Counter Asinkron 3-bit

Tabel 6.2 Tabel Kebenaran dari Up Counter Asinkron 3-bit

COUNTER

VI - 4

Modul Praktikum Teknik Digital

Berdasarkan bentuk timing diagram di atas, output dari flip-flop C menjadi clock dari flip-flop B,

sedangkan output dari flip-flop B menjadi clock dari flip-flop A. Perubahan pada negatif edge di

masing-masing clock flip-flop sebelumnya menyebabkan flip-flop sesudahnya berganti kondisi

(toggle), sehingga input-input J dan K di masing-masing flip-flop diberi nilai 1 (sifat toggle dari

JK flip-flop). Bentuk dasar dari Counter Asinkron 3-bit ditunjukkan pada gambar 6.6.

Gambar 6.6 Up Counter Asinkron 3 bit.

Conter Asinkron Mod-N

Counter Mod-N adalah Counter yang tidak 2n. Misalkan Counter Mod-6, menghitung : 0, 1, 2, 3,

4, 5. Sehingga Up Counter Mod-N akan menghitung 0 s/d N-1, sedangkan Down Counter MODN akan menghitung dari bilangan tertinggi sebanyak N kali ke bawah. Misalkan Down Counter

MOD-9, akan menghitung : 15, 14, 13, 12, 11, 10, 9, 8, 7, 15, 14, 13,..

Sebuah Up Counter Asinkron Mod-6, akan menghitung : 0,1,2,3,4,5,0,1,2,... Maka nilai yang

tidak pernah dikeluarkan adalah 6. Jika hitungan menginjak ke-6, maka counter akan reset

kembali ke 0. Untuk itu masing-masing Flip-flop perlu di-reset ke nilai 0 dengan memanfaatkan

input-input Asinkron-nya (1=SPdan 0=CP). Nilai 0 yang akan dimasukkan di PC didapatkan

COUNTER

VI - 5

Modul Praktikum Teknik Digital

dengan me-NAND kan input A dan B (ABC = 110 untuk desimal 6). Jika input A dan B keduanya

bernilai 1, maka seluruh flip-flop akan di-reset.

4. Prosedur Percobaan

Karakteristik D-Type 2-bit Binary Counter

Gambar 6.7 Karakteristik D-Type 2-bit Binary Counter

1. Masukkan shorting link dan koneksikan rangkaian seperti gambar 6.7.

2. Switch modul power supply pada posisi On dan set switch C ke level logika 1.

3. Gunakan clock pulse satu, amati output state QA dan QB kemudian catat hasil datanya

di baris kedua pada tabel 6.3.

4. Gunakan clock pulsa kedua. Amati output state QA dan QB kemudian catat hasil

datanya pada tabel 6.3.

5. Ulangi prosedur, gunakan clock pulsa selanjutnya dan catat hasilnya untuk melengkapi

tabel 6.3 dibawah ini.

Tabel 6.3.

Clock Pulse

QB

0

QA

0

Initial state

COUNTER

VI - 6

Modul Praktikum Teknik Digital

2

3

4

Catatan :

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

6. Amati 2-bit output state dari QB dan QA. Kamu akan melihat binary output meningkat

oleh satu pada tiap clock pulsa. Ini adalah 2-bit asynchronous UP counter.

7. Putuskan link antara socket 2.9 & 2.12 dan hubungkan lead antara socket 2.7 & 2.12

sehingga D-type flip-flop B adalah clock dari output QA. Ulangi prosedur dan lengkapi

tabel 6.4 dibawah ini.

Tabel 6.4.

Clock Pulse

QB

0

QA

0

Initial state

1

2

3

4

8. Amati 2-bit output state dari QB dan QA. Kamu akan melihat binary output menurun oleh

satu pada tiap clock pulsa. Ini adalah 2-bit asynchronous DOWN counter.

Catatan :

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

COUNTER

VI - 7

Modul Praktikum Teknik Digital

Karakteristik J-K 4-bit Binary Counter

Gambar 6.8 Karakteristik J-K 4-bit Binary Counter

1.

2.

3.

4.

Masukkan shorting link dan koneksikan rangkaian seperti pada gambar 6.8.

Switch modul power supply pada posisi ON dan set switch A, C dan D ke level logika 1.

Set rangkaian untuk inisialisasi state yang ditunjukkan di tabel 6.5.

Gunakan clock pulse satu, amati output state QA, QB, QC & QD kemudian catat hasil

datanya di baris kedu pada tabel 6.5.

5. Ulangi prosedur, gunakan clock pulse selanjutnya, amati output state untuk setiap pulse

dan catat hasil datanya di tabel 6.5.

Tabel 6.5.

Clock

QB

QA

QC

QD

Pulse

Initial state

1

2

3

4

5

6

7

8

9

10

11

12

13

COUNTER

VI - 8

Modul Praktikum Teknik Digital

14

15

Catatan :

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

6. Amati 4-bit binary output dari QD, QC, QB dan QA. Pada setiap clock pulsa jumlah

meningkat oleh satu. Ini adalah 4-bit asynchronous UP counter.

7. Putuskan shorting link antara socket 4.11 & 4.12, 4.22 & 4.23 dan 4.31 & 4.32.

8. Hubungkan leads antara socket 4.13 & 4.17, 4.24 & 4.27 dan 4.33 & 4.37 sehingga flipflop diclock dari

output dari flip-flop sebelumnya.

9. Ulangi prosedur dan lengkapi tabel 6.6.

Tabel 6.6.

Clock

QD

QC

QB

QA

Pulse

Initial state

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

10. Amati 4-bit binary output dari QD, QC, QB dan QA. Pada setiap clock pulsa jumlah

menurun oleh satu. Ini adalah 4-bit asynchronous DOWN counter.

COUNTER

VI - 9

Modul Praktikum Teknik Digital

Catatan :

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

Karakteristik Binary Up Counter with Reduce Count

Gambar 6.4.

1. Masukkan shorting links dan koneksikan rangkaian seperti gambar 6.4.

2. Switch modul power supply pada posisi ON dan set switch A dan D ke level logika 1.

Menentukan tabel kebenaran untuk rangkaian diatas dan melengkapi tabel 6.5.

Tabel 6.5.

Clock

QD

0

QC

0

QB

0

QA

0

Initial state

1

2

3

4

5

COUNTER

VI 10

Modul Praktikum Teknik Digital

6

7

8

9

10

11

12

13

14

15

Kamu harus menemukan count reset yaitu nol pada clock pulsa sembilan. Rangkaian

gerbang NAND yang dikoneksikan ke output QB dan QD. Ketika output menghasilkan

HIGH, output gerbang NAND menghasilkan LOW dan menghapus semua filp-flop secara

simultan, reset counter menjadi nol.

Catatan :

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

Karakteristik Binary Down Counter with Reduce Count

COUNTER

VI 11

Modul Praktikum Teknik Digital

Gambar 6.5.

1. Masukkan shorting links dan koneksikan rangkaian seperti gambar 6.5.

2. Switch modul power supply pada posisi ON dan set switch A dan D ke level logika 1.

Menentukan tabel kebenaran untuk rangkaian diatas dan melengkapi tabel 6.6.

Tabel 6.6.

Clock

QD

QC

QB

QA

Pulse

Initial state

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

Rangkaian ini bekerja dengan cara yang sama seperti rangkaian sebelumnya kecuali

bahwa count yang di reset oleh pulsa clock yang ke tiga belas. Rangkaian gerbang NAND

COUNTER

VI 12

Modul Praktikum Teknik Digital

tiga-masukan yang digunakan untuk memantau QA, QC dan QD. Ketika tiga output

menghasilkan HIGH bersama-sama output gerbang NAND menghasilkan LOW dan

menolak semua flip-flop JK secara bersamaan. Counter direset ke nol dan mulai

menghitung lagi.

Catatan :

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

.................................................................................................................................................

COUNTER

VI 13

Anda mungkin juga menyukai

- Counter Up DownDokumen10 halamanCounter Up DownSinggih AdhiyatmaBelum ada peringkat

- Perc5 counterASinkronDokumen4 halamanPerc5 counterASinkronAkhmad YaniBelum ada peringkat

- Makalah Elka Counter Dan RegisterDokumen15 halamanMakalah Elka Counter Dan RegisterHafisyah Rahmat PutraBelum ada peringkat

- Teknik DigitalDokumen10 halamanTeknik DigitalArief IndrasBelum ada peringkat

- Materi Flip FlopDokumen11 halamanMateri Flip FlopnafaliaBelum ada peringkat

- Galih Muhammad Ghufron - 1306619059 - Laporan Awal (RANGKAIAN COUNTER)Dokumen9 halamanGalih Muhammad Ghufron - 1306619059 - Laporan Awal (RANGKAIAN COUNTER)ghufron galihBelum ada peringkat

- SSK Rangkaian CounterDokumen9 halamanSSK Rangkaian Countersapin wijayakusuma990Belum ada peringkat

- Bab 1 Rangkaian SequentialDokumen16 halamanBab 1 Rangkaian SequentialTioRamadhanBelum ada peringkat

- Rangkaian Counter Adalah Rangkaian Elektronika Yang Befungsi Untuk Melakukan Penghitungan Angka Secara Berurutan Baik Itu Perhitungan Maju Ataupun Perhitungan MundurDokumen14 halamanRangkaian Counter Adalah Rangkaian Elektronika Yang Befungsi Untuk Melakukan Penghitungan Angka Secara Berurutan Baik Itu Perhitungan Maju Ataupun Perhitungan MundurShinyo Handjie Shio 'exinus'100% (1)

- Rangkaian PencacahDokumen9 halamanRangkaian PencacahandriantoBelum ada peringkat

- Sistem Komputer X CounterDokumen9 halamanSistem Komputer X CounterpuriBelum ada peringkat

- Modul 8 CounterDokumen17 halamanModul 8 CounterAdi Widya Sekar KinantiBelum ada peringkat

- Adisti Nastiti 2NK Laporan Praktikum 11Dokumen11 halamanAdisti Nastiti 2NK Laporan Praktikum 11ADISTI NASTITIBelum ada peringkat

- SS Materi CounterDokumen7 halamanSS Materi CounterRoffyBelum ada peringkat

- Laprak SLD Modul 6Dokumen32 halamanLaprak SLD Modul 6Elma FebrianaBelum ada peringkat

- 5 Counter SinkronDokumen5 halaman5 Counter SinkronMuhKhoirulBelum ada peringkat

- Makalah Counter Dan Register Genta-DikonversiDokumen16 halamanMakalah Counter Dan Register Genta-DikonversiGenta Tri KurniawanBelum ada peringkat

- Galih Muhammad Ghufron - 1306619059 - Laporan Akhir (RANGKAIAN COUNTER)Dokumen17 halamanGalih Muhammad Ghufron - 1306619059 - Laporan Akhir (RANGKAIAN COUNTER)ghufron galihBelum ada peringkat

- Apa Itu CounterDokumen21 halamanApa Itu CounterMiboyBelum ada peringkat

- Laporan Rencana Praktikum Sistem DigitalDokumen7 halamanLaporan Rencana Praktikum Sistem DigitalAuriel Diya Ulhaque M.WBelum ada peringkat

- Pencacah (Counter)Dokumen31 halamanPencacah (Counter)Andi Salsabilahf100% (1)

- CounterDokumen5 halamanCounterMariesta AriantiBelum ada peringkat

- Bab V - PPLCDokumen16 halamanBab V - PPLCBintang Putra SaylendraBelum ada peringkat

- 3 PencacahDokumen11 halaman3 PencacahSutisnaBelum ada peringkat

- Iqbal Azmi Harisnaini Praktikum5Dokumen7 halamanIqbal Azmi Harisnaini Praktikum5Azmi Iqbal0% (1)

- CounterDokumen18 halamanCounterAdira Salsabila100% (1)

- Percobaan 8 COUNTERDokumen10 halamanPercobaan 8 COUNTERCocote DiwalekBelum ada peringkat

- Laporan (AutosaDokumen24 halamanLaporan (AutosaKemasAlsyaAfrilianBelum ada peringkat

- Tugas Instalasi ListrikDokumen11 halamanTugas Instalasi ListrikucayBelum ada peringkat

- Praktikum Elektronika DigitalDokumen5 halamanPraktikum Elektronika DigitalY GIFTBelum ada peringkat

- Praktikum Elektronika DigitalDokumen5 halamanPraktikum Elektronika DigitalY GIFTBelum ada peringkat

- Bab4 CounterDokumen65 halamanBab4 Counteranis nadhifah100% (2)

- Laporan5 IkangRahmatullah 09030581923036Dokumen22 halamanLaporan5 IkangRahmatullah 09030581923036Ikang RahmatullahBelum ada peringkat

- Adisti Nastiti - 2NK - Laporan Praktikum Counter AsinkronDokumen13 halamanAdisti Nastiti - 2NK - Laporan Praktikum Counter AsinkronADISTI NASTITIBelum ada peringkat

- Rangkuman CounterDokumen7 halamanRangkuman CounterAldo Sultan MannakenBelum ada peringkat

- P6 CounterDokumen7 halamanP6 CounterSyahrizal FirdausBelum ada peringkat

- 30 - Yunita Claudia - TG 4 - Pre - Xii Tav 2 - 11Dokumen7 halaman30 - Yunita Claudia - TG 4 - Pre - Xii Tav 2 - 11Yunita ClaudiaBelum ada peringkat

- Register Dan Counter 2Dokumen11 halamanRegister Dan Counter 2HafidzSatyaNugrahaBelum ada peringkat

- 16 - Kel.10 - Tt3c - Ic CounterDokumen14 halaman16 - Kel.10 - Tt3c - Ic CounterfaisalBelum ada peringkat

- Counter Kelompok 1Dokumen20 halamanCounter Kelompok 1MayaAyuAulyaSariBelum ada peringkat

- Kerangka 8Dokumen15 halamanKerangka 8Abdul BashitBelum ada peringkat

- Rangkaian Counter UpDokumen9 halamanRangkaian Counter UpNur KhotibBelum ada peringkat

- Counter SinkronDokumen9 halamanCounter SinkronRochman SoewarnoBelum ada peringkat

- Universal Shift RegisterDokumen17 halamanUniversal Shift RegisterSobar WilmanBelum ada peringkat

- CounterDokumen12 halamanCounterAbdul BasriBelum ada peringkat

- COUNTER (Pencacah)Dokumen3 halamanCOUNTER (Pencacah)Ari GusroBelum ada peringkat

- Laporan Praktikum 3 CounterDokumen10 halamanLaporan Praktikum 3 Counterahmadsubakhir.asBelum ada peringkat

- Modul 3Dokumen9 halamanModul 3Nuzulul RahmahBelum ada peringkat

- Literatur Riview Rangkaian Digital CountDokumen4 halamanLiteratur Riview Rangkaian Digital CountRaka PratindyBelum ada peringkat

- Lapres06 - 2220610007 - Shafira Zelinda Ainiyatur Rohmah (Eldig2)Dokumen17 halamanLapres06 - 2220610007 - Shafira Zelinda Ainiyatur Rohmah (Eldig2)shafira zeindaBelum ada peringkat

- Modul ElektronikaDokumen11 halamanModul Elektronikapunisher213Belum ada peringkat

- CounterDokumen45 halamanCounterOpik QurrahmanBelum ada peringkat

- Rangkaian Logika SekuensialDokumen7 halamanRangkaian Logika SekuensialRizkaBelum ada peringkat

- Bab 1Dokumen44 halamanBab 1Lusi ArsenalBelum ada peringkat

- KKW Andi PalambaDokumen47 halamanKKW Andi PalambaLusi ArsenalBelum ada peringkat

- Bab 3Dokumen61 halamanBab 3Lusi ArsenalBelum ada peringkat

- Bab 10Dokumen81 halamanBab 10Lusi Arsenal100% (1)

- Bab 1Dokumen44 halamanBab 1Lusi ArsenalBelum ada peringkat

- Counter - Mundur Tak SerempakDokumen8 halamanCounter - Mundur Tak SerempakMonic AprilliaBelum ada peringkat

- DSP Tutorial 6Dokumen27 halamanDSP Tutorial 6Lusi ArsenalBelum ada peringkat