0% menganggap dokumen ini bermanfaat (0 suara)

131 tayangan8 halamanRangkaian Osilator Hartley dalam Telekomunikasi

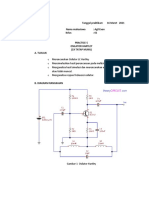

1. Laporan praktikum ini membahas desain dan simulasi osilator Hartley dengan menggunakan software Multisim.

2. Osilator Hartley menggunakan dua gulungan induktif secara seri dengan kapasitor paralel untuk membentuk rangkaian resonansi dan menghasilkan osilasi sinusoidal.

3. Hasil simulasi menunjukkan bahwa frekuensi resonansi osilator Hartley ditentukan oleh nilai induktor seri dan kapasitor yang digunakan.

Diunggah oleh

Icha TarahaHak Cipta

© © All Rights Reserved

Kami menangani hak cipta konten dengan serius. Jika Anda merasa konten ini milik Anda, ajukan klaim di sini.

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online di Scribd

0% menganggap dokumen ini bermanfaat (0 suara)

131 tayangan8 halamanRangkaian Osilator Hartley dalam Telekomunikasi

1. Laporan praktikum ini membahas desain dan simulasi osilator Hartley dengan menggunakan software Multisim.

2. Osilator Hartley menggunakan dua gulungan induktif secara seri dengan kapasitor paralel untuk membentuk rangkaian resonansi dan menghasilkan osilasi sinusoidal.

3. Hasil simulasi menunjukkan bahwa frekuensi resonansi osilator Hartley ditentukan oleh nilai induktor seri dan kapasitor yang digunakan.

Diunggah oleh

Icha TarahaHak Cipta

© © All Rights Reserved

Kami menangani hak cipta konten dengan serius. Jika Anda merasa konten ini milik Anda, ajukan klaim di sini.

Format Tersedia

Unduh sebagai DOCX, PDF, TXT atau baca online di Scribd