Adder

Diunggah oleh

Kharisma Juwita NurigaHak Cipta

Format Tersedia

Bagikan dokumen Ini

Apakah menurut Anda dokumen ini bermanfaat?

Apakah konten ini tidak pantas?

Laporkan Dokumen IniHak Cipta:

Format Tersedia

Adder

Diunggah oleh

Kharisma Juwita NurigaHak Cipta:

Format Tersedia

Selamat datang di Wikipedia bahasa Indonesia!

[tutup]

Penjumlah biner

Dari Wikipedia bahasa Indonesia, ensiklopedia bebas

(Dialihkan dari Adder)

Belum Diperiksa

Penjumlah atau Adder adalah komponen elektronika digital yang dipakai untuk menjumlahkan dua buah angka dalam sistem bilangan biner. Dalam komputer dan mikroprosesor, Adder biasanya berada di bagian ALU (Arithmetic Logic Unit). Sistem bilangan yang dipakai dalam proses penjumlahan, selain bilangan biner, juga 2's complement untuk bilangan negatif, bilangan BCD (binary-coded decimal), dan excess-3. Jika sistem bilangan yang dipakai adalah 2's complement, maka proses operasi penjumlahan dan operasi pengurangan akan sangat mudah dilakukan.

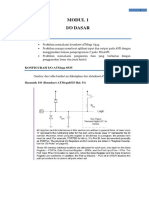

Diagram sirkuit Half-Adder

Pembicaraan mengenai Adder biasanya dimulai dari Half-Adder, kemudian Full-Adder, dan yang ketiga adalah Ripple-Carry-Adder. Pada Half-Adder, berdasarkan dua input A dan B, maka output Sum, S dari Adder ini akan dihitung berdasarkan operasi XOR dari A dan B. Selain output S, ada satu output yang lain yang dikenal sebagai C atau Carry, dan C ini dihitung berdasarkan operasi AND dari A dan B. Pada prinsipnya output S menyatakan penjumlahan bilangan pada input A dan B, sedangkan output C menyatakan MSB (most significant bit atau carry bit) dari hasil jumlah itu.

Tabel logika/kebenaran dari Half-Adder akan mengikuti seperti berikut:

Input Output

A B C

0 0

0 1

1 0

1 1

Diagram blok Full-Adder

Rangkaian Full-Adder, pada prinsipnya bekerja seperti Half-Adder, tetapi mampu menampung bilangan Carry dari hasil penjumlahan sebelumnya. Jadi jumlah inputnya ada 3: A, B dan Ci, sementara bagian output ada 2: S dan Co. Ci ini dipakai untuk menampung bit Carry dari penjumlahan sebelumnya.

Diagram sirkuit Full-Adder

Input

Output

Rangkaian dari n buah Full-Adder bisa dipakai untuk menjumlahkan n bit bilangan biner. Maka dalam hal ini, kita akan memperoleh rangkaian yang disebut Ripple-Carry-Adder.

Diagram sirkuit untuk ripple carry adder 4-bit

=======================

============================== http://habibie16.blogspot.com/2013/01/half-adder-dan-full-adder.html

Half Adder dan Full Adder

Hmmmmmm. Sekarang disini kita mencoba ngenal Rangkaina Half Adder dan Full Adder Gmn ada yg udah pada tw blon?????.... kl udah coba cek takutnya ada kesalahan dalam materi di bawah ini

CAPCUUUUUUUUUSSSSS Ke TKP.

Half Adder

Adalah rangkaian elektronika yang bekerja melakukan perhitungan penambahan/penjumlahan dari 2 buah bilagan binary yg terdiri dari 1 bit.

Half Adder memiliki dua input dan dua buah output, dengan menggunakan dua buah gerbang logika XOR nan AND, salah satu outputnya dipakai sebagai tempat nilai pindahan dari hasil penjumlahan dan satunya lagi sebagai hasil dari penjumlahan.

Gambar Rangkaian Half Adder

Truth Table Half Adder

Full Adder merupakan rangkaian elektronika yang menjumlahkan dua bilangan yang telah dikonversikan menjadi bilangan-bilangan biner.

Masing-masing bit pada posisi yang sama saling dijumlahkan. Full Addersebagai penjumlah pada bit-bit selain yang terendah. Full Adder menjumlahkan dua bit input ditambah dengan nilai Carry-Out dari penjumlahan bit sebelumnya. Output dari Full Adder adalah hasil penjumlahan (Sum) dan bit kelebihannya (carry-out)

Gambar Rangkaian Full Adder

Truth Table Full Adder

nah... sekian penjelasan mengenail half dan full Adder, disini kita sama" belajar jadi klo terdapat kesalahan dalam penjelasan di atas di keritik aja untuk di luruskan

============================

SISTEM DIGITAL

Tutorial Half Adder dan Full Adder

BAB I PENDAHULUAN

A. Latar Belakang Perkembangan Teknologi Digital saat ini yang semakin maju.Masyarakat saat ini telah terpesona oleh komputer dan kalkulator modern. Ini mungkin karena mesin tersebut menghasilkan fungsi aritmatika dengan ketelitian dan kecepatan yang sangat menakjubkan. Bab ini membicarakan beberapa rangkaian logika yang dapat menjumlahkan dan mengurangkan. Penambahan dan pengurangan dikerjakan dalam biner. Gerbang logika biasa akan kita rangkai satu sama yang lain untuk menghasilkan penambahan dan pengurangan. B. Tujuan Secara luas, dengan adanya rangkaian half adder, full adder dan parallel adder diharapkan kita atau si pembaca nantinya dapat memanfaatkan rangkaian tersebut untuk kepentingan masyarakat banyak dan menunjang kehidupan manusia. Semoga dengan ditemukannya alat yang menggunakan prinsip Half Adder, Full Adder dan parallel dan dapat dipublikasikan kepublic sehingga masyarakat banyak didunia bias memakainya. Secara khusus tujuan dari penulis adalah agar :

1. Mahasiswa dapat membentuk bilangan biner bertanda dari bilangan desimal positif dan negatif 2. Mahasiswa dapat melakukan operasi penjumlahan bilangan-bilangan biner bertanda dengan bentuk-bentuk complement. 3. Menjelaskan operasi rangkaian Half, Full, dan Parallel Adder. 4. Menentukan persamaan operasional rangkaian Half, Full, dan Parallel Adder

BAB II PEMBAHASAN

ALU (Aritmetic and Logic Unit)

Unit Aritmetika dan Logika merupakan bagian pengolah bilangan dari sebuah komputer.Operasi Aritmatika terdiri dari berbagai macam operasi diantaranya adalah operasi penjumlahan, pengurangan, perkalian, dan pembagian. Cara Pendesinan pada ALU hampir sama dengan mendesain enkoder, multiplexer, dan di Multiplexer. Rangkaian utama yang digunakan untuk melakukan perhitungan ALU adalah Adder. Rangkaian pada ALU (Arithmetic and Logic Unit) yang digunakan untuk menjumlahkan bilangan dinamakan dengan Adder. Adder digunakan untuk memproses operasi aritmetika, Adder juga disebut rangkaian kombinasional aritmatika. Ada 3 jenis adder: 1.Rangkaian Adder dengan menjumlahkan dua bit disebut Half Adder. 2.Rangkaian Adder dengan menjumlahkan tiga bit disebut Full Adder. 3.Rangkain Adder dengan menjumlahkan banyak bit disebut Paralel Adder . A. Half Adder Rangkaian Half Adder merupakan dasar penjumlahan bilangan Biner yang terdiri dari satu bit, oleh karena itu dinamai Penjumlah Tak Lengkap. 1. jika A = 0 dan B = 0 dijumlahkan, hasilnya S ( Sum ) = 0. 2. jika A = 0 dan B = 1 dijumlahkan, hasilnya S ( Sum ) = 1. 3. jika A = 1 dan B = 1 dijumlahkan, hasilnya S ( Sum ) = 0 4. jika A = 1 dan B =1 dijumlahkan, hasilnya S ( Sum ) = 0. dengan nilai pindahan cy(Carry Out) = 1

Dengan demikian, half adder memiliki 2 masukan ( A dan B ) dan dua keluaran ( S dan Cy ). Tabel Kebenaran Rangkaian Half Adder A 0 0 1 B 0 1 0 S 0 1 1 C 0 0 0

1 Ket: S = Sum, hasil jumlah C = Carry, sisa hasil jumlah

A. HALF ADDER Sebuah rangkaian Adder terdiri dari Half Adder dan Full Adder. Half Adder menjumlahkan dua buah bit input, dan menghasilkan nilai jumlahan (sum) dan nilai lebihnya (carry-out). Half Adderdiletakkan sebagai penjumlah dari bit-bit terendah (Least Significant Bit). seperti gabar di bawah. Half Adder A B S CBOB

INPUT OUTPUT

Prinsip kerja Half Adder ditunjukkan pada gambar di bawah.

Sebuah Half Adder mempunyai Tabel Kebenaran seperti yaitu:

Berdasarkan output-output yang didapatkan dari Tabel Kebenaran, dibuat rangkaian seperti gambar di bawah.

Persamaan Half Adder:

B. FULL ADDER Sebuah Full Adder menjumlahkan dua bilangan yang telah dikonversikan menjadi bilangan-bilangan biner. Masing-masing bit pada posisi yang sama saling dijumlahkan. Full Adder sebagai penjumlah pada bit-bit selain yang terendah. Full Adder menjumlahkan dua bit input ditambah dengan nilai Carry-Out dari penjumlahan bit sebelumnya. Output dari Full Adder adalah hasil penjumlahan (Sum) dan bit kelebihannya (carry-out). Blok diagram dari sebuah full adder diberikan pada gambar di bawah. Full Adder A B S CBBBOBBB CBBBINBBB

INPUT OUTPUT

Tabel Kebenaran untuk sebuah Full Adder yaitu:

Berdasarkan output-output yang didapatkan dari Tabel Kebenaran, dibuat rangkaian seperti gambar di bawah. A1 B1 CIN COUT S1

Persamaan Full Adder:

C. PARALEL ADDER Rangkaian Parallel Adder adalah rangkaian penjumlah dari dua bilangan yang telah dikonversikan ke dalam bentuk biner. Anggap ada dua buah register A dan B, masing-masing register terdiri dari 4 bit biner : A3A2A1A0 dan B3B2B1B0. Penjumlahan dari kedua register itu dapat dinyatakan sebagai berikut :

Rangkaian Parallel Adder dari persamaan di atas ditunjukkan pada gambar 9-2.

Rangkaian Parallel Adder terdiri dari Sebuah Half Adder (HA) pada Least Significant Bit(LSB) dari masing-masing input dan beberapa Full Adder pada bit-bit berikutnya. Prinsip kerja dari Parallel Adder adalah sebagai berikut : penjumlahan dilakukan mulai dari LSB-nya. Jika hasil penjumlahan adalah bilangan desimal 2 atau lebih, maka bit kelebihannya disimpan pada Cout, sedangkan bit di bawahnya akan dikeluarkan pada . Begitu seterusnya menuju ke Most Significant Bit (MSB)nya.

BAB III PENUTUP

1. Kesimpulan 1. Half Adder Adalah suatu operasi penjumlahan dua bit biner tanpa menyertakan carry-in nya 2. Persamaan Half Adder:

3. Persamaan Half Adder:

1.

4. Full Adder adalah sebuah rangkaian kombinasional yang melaksanakan operasi penjumlahan aritmetika dari 3 bit input 5. Parallel Adder adalah rangkaian penjumlah dari dua bilangan yang telah dikonversikan ke dalam bentuk biner Saran-saran 1. Carilah bahan yang paling mudah dimegerti, ringkas, dan idak berbelit-belit. 2. Bahan yang disiapkan harus benar-benar tepat mengenai topik yang diinginkan. 3. Carilah bahan dari berbagai sumber, sehingga topik tidak terlalu monoton.

DAFTAR PUSTAKA

-Internet, www.indoskripsi.com -Internet, www.Google.com

Anda mungkin juga menyukai

- Half AdderDokumen3 halamanHalf AdderOpal Afra RamizBelum ada peringkat

- Laporan AdderSubtractorFIKSDokumen21 halamanLaporan AdderSubtractorFIKSAyu NingrumBelum ada peringkat

- Laporan Rangkaian Adder Deva Nur Avivah 19063042 EadDokumen10 halamanLaporan Rangkaian Adder Deva Nur Avivah 19063042 EadDeva AvivahBelum ada peringkat

- Half Adder & Full AdderDokumen6 halamanHalf Adder & Full AdderAnonymous 9birR2tIBelum ada peringkat

- D4TE - 1A-07-Muhammad Ibnu AbbasDokumen7 halamanD4TE - 1A-07-Muhammad Ibnu AbbasMUHAMMAD IBNUBelum ada peringkat

- Rangkaian KombinasiDokumen29 halamanRangkaian KombinasiBagus FatkhurroziBelum ada peringkat

- Medan ElektromagnetikDokumen24 halamanMedan ElektromagnetikZulkifli Arfah IIBelum ada peringkat

- 4-BIT Binary Up/Down Counter With VHDLDokumen6 halaman4-BIT Binary Up/Down Counter With VHDLInesh EskanesiariBelum ada peringkat

- Praktik Sistem Digital 5Dokumen22 halamanPraktik Sistem Digital 5PuPo TechBelum ada peringkat

- Teknik Digital2Dokumen116 halamanTeknik Digital2bersinar terangBelum ada peringkat

- Asynchronous CounterDokumen14 halamanAsynchronous CounterwenBelum ada peringkat

- Shift RegisterDokumen9 halamanShift RegisterIkhsanul ArifBelum ada peringkat

- Modul 5 Rangkaian AritmatikaDokumen18 halamanModul 5 Rangkaian AritmatikaShihabul Milah IbrahimBelum ada peringkat

- Mengklasifikasikan Rangkaian MultiplexerDokumen6 halamanMengklasifikasikan Rangkaian MultiplexerZira WhiterBelum ada peringkat

- Rangkaian CounterDokumen16 halamanRangkaian CounterAnda SugandaBelum ada peringkat

- Teorema Superposisi Thevenin-NortonDokumen22 halamanTeorema Superposisi Thevenin-Nortonelfri_gBelum ada peringkat

- Percobaan 13Dokumen13 halamanPercobaan 13I Made WBelum ada peringkat

- Rangkaian AdderDokumen15 halamanRangkaian AdderFiras Iffat Altamis100% (1)

- Rangkaian Flip Flop SRDokumen10 halamanRangkaian Flip Flop SRIrvan NdooBelum ada peringkat

- II Transformasi LaplaceDokumen15 halamanII Transformasi LaplaceNur AzizahBelum ada peringkat

- Observasi BusDokumen10 halamanObservasi BusYogi AmtaraBelum ada peringkat

- Jurnal Sensor Suhu Tubuh ArduinoDokumen88 halamanJurnal Sensor Suhu Tubuh ArduinoRadilsha MaharaniBelum ada peringkat

- Laporan Praktikum Sistem DigitalDokumen13 halamanLaporan Praktikum Sistem DigitalResy Dwi LarasBelum ada peringkat

- Rangkaian DIGITAL ARITMATIKDokumen15 halamanRangkaian DIGITAL ARITMATIKKrisna SinghBelum ada peringkat

- Counter DownDokumen7 halamanCounter DownPratiwi PutriyanBelum ada peringkat

- Laporan Praktikum MikroprosesorDokumen6 halamanLaporan Praktikum MikroprosesorSyifa NurulBelum ada peringkat

- Laporan Half Adder Dan Full Adder Kelompok 4Dokumen27 halamanLaporan Half Adder Dan Full Adder Kelompok 4Muhammad RizkiBelum ada peringkat

- Irvan Sandi Manullang - Tugas 1 Mikon 2Dokumen6 halamanIrvan Sandi Manullang - Tugas 1 Mikon 2Irvan ManullangBelum ada peringkat

- Makalah Kontrol P Sistem KendaliDokumen6 halamanMakalah Kontrol P Sistem Kendalirida ameliaBelum ada peringkat

- Fungsi-Fungsi IC Digital KombinasionalDokumen12 halamanFungsi-Fungsi IC Digital KombinasionalCelig CeyigBelum ada peringkat

- 04 D-4 Aulia Raden Puteh 118130106 EL2209 Okta PriyaniDokumen9 halaman04 D-4 Aulia Raden Puteh 118130106 EL2209 Okta Priyaniya yaBelum ada peringkat

- P05.5-Memory Mapping Practice 02-WACDokumen20 halamanP05.5-Memory Mapping Practice 02-WACNigel BryanBelum ada peringkat

- LAPORAN LAB ELDA AdderDokumen14 halamanLAPORAN LAB ELDA AdderNabilaBelum ada peringkat

- Adder & Subtractor Kelompok 5Dokumen10 halamanAdder & Subtractor Kelompok 5They HarryBelum ada peringkat

- Febriansyah Naufal Akbar - Modul 3Dokumen7 halamanFebriansyah Naufal Akbar - Modul 3Febriansyah Naufal AkbarBelum ada peringkat

- 7 InterruptDokumen20 halaman7 InterruptMelfini TambaBelum ada peringkat

- Praktikum - 2 - Analog Input OutputDokumen6 halamanPraktikum - 2 - Analog Input Outputiqbal ramadhanBelum ada peringkat

- Artikel Filter DigitalDokumen5 halamanArtikel Filter DigitalekaBelum ada peringkat

- Modul 1Dokumen6 halamanModul 1nonameBelum ada peringkat

- Bab 2 Fix (Encoder)Dokumen3 halamanBab 2 Fix (Encoder)Angfika Septianto WijayaBelum ada peringkat

- Percobaan 3 - Rangkaian Dasar Penyederhanaan Dengan K-MapsDokumen12 halamanPercobaan 3 - Rangkaian Dasar Penyederhanaan Dengan K-Mapsroicha dwiBelum ada peringkat

- Rangkaian Pada Lampu Lalu LintasDokumen5 halamanRangkaian Pada Lampu Lalu Lintasrhiyanoke100% (1)

- Rangkuman Sinyal Informasi Dasar Sistem TelekomunikasiDokumen6 halamanRangkuman Sinyal Informasi Dasar Sistem Telekomunikasiteuku afrianBelum ada peringkat

- Operational AmplifierDokumen4 halamanOperational AmplifierBima Dwi ErlanggaBelum ada peringkat

- Shift RegisterDokumen9 halamanShift RegisterRisga Gracela WibowoBelum ada peringkat

- Flip-Flop, Counter, GERBANG LOGIKA DAN RANGKAIAN KOMBINASIONALDokumen10 halamanFlip-Flop, Counter, GERBANG LOGIKA DAN RANGKAIAN KOMBINASIONALFikri Hidayat75% (4)

- Lecture 2 PSTLDokumen23 halamanLecture 2 PSTLYhola YosevinBelum ada peringkat

- UTS Mesin Mesin Listrik AC Syekila NazifahDokumen23 halamanUTS Mesin Mesin Listrik AC Syekila NazifahSyekila nazifaBelum ada peringkat

- 01 - F-1 - EL3109 SIskomDokumen12 halaman01 - F-1 - EL3109 SIskomAnton NugrohoBelum ada peringkat

- Laporan Praktikum Sistem Komputer Mux Dan DemuxDokumen9 halamanLaporan Praktikum Sistem Komputer Mux Dan DemuxMawaddatur RizaBelum ada peringkat

- Tugas Perancangan Sistem Kendali DigitalDokumen34 halamanTugas Perancangan Sistem Kendali DigitalHiro CrownBelum ada peringkat

- Diktat UTS Genap 2018 Sinyal Dan SistemDokumen29 halamanDiktat UTS Genap 2018 Sinyal Dan SistemVERONIKABelum ada peringkat

- BAB II Sistem Kendali SederhanaDokumen9 halamanBAB II Sistem Kendali SederhanaMywa BenzeaBelum ada peringkat

- Feh2l3 Uts 080319 SolusiDokumen5 halamanFeh2l3 Uts 080319 SolusiMuhammad Zhafran AlivaBelum ada peringkat

- Multiplexer Dan DemultiplexerDokumen14 halamanMultiplexer Dan DemultiplexerRegita PebrianaBelum ada peringkat

- Parameter Dari Elemen IDokumen4 halamanParameter Dari Elemen IPutri Widya Sari TamaBelum ada peringkat

- TestDokumen8 halamanTestNurhasanBelum ada peringkat

- BPF AktifDokumen10 halamanBPF Aktifserena enjelBelum ada peringkat

- Makalah Sistem DigitalDokumen17 halamanMakalah Sistem DigitalMunirBelum ada peringkat

- Link Assassin Creed BrotherhoodDokumen7 halamanLink Assassin Creed BrotherhoodVebri PradanaBelum ada peringkat